Chips de memoria y dispositivos que los emplean.

Un dispositivo de memoria que comprende:

un primer chip de memoria (10) para recibir una señal de dirección de entrada (ADDin) y acoplado a una tableta deespera (Pw);

y

un segundo chip de memoria (11) para recibir la señal de dirección de entrada (ADDin) y acoplado a la tableta deespera (Pw), en donde el primer chip de memoria (10) y el segundo chip de memoria (11) operan alternativamenteen un modo activo,

en donde

cada uno del primer chip de memoria (10) y el segundo chip de memoria (11) comprende:

una unidad de control (100,110) para recibir la señal de dirección de entrada ADDin y al menos una señal decomando (Scom), que determina y controla un modo de operación del chip de memoria correspondiente de acuerdocon la señal de dirección de entrada (ADDin) y al menos una señal de comando (Scom), y generar una primer señalde control (CS1, CS1_b) de acuerdo al resultado de determinación;

un controlador de espera (101, 111) acoplado a la tableta de espera, (Pw), para recibir la primera señal de control(CS1) y cambiar un estado de una señal de espera (Sw) a la tableta de espera (Pw) de acuerdo con la primera señalde control (CS1, CS1_b); y un receptor de espera (102, 112), acoplado a una tableta de espera (Pw), para recibir laseñal de espera (Sw) y detectar el estado de la señal de espera (Sw) para generar una segunda señal de control(CS2, CS2_b).

en donde el primer chip de memoria (10) opera en un modo activo y el segundo chip de memoria (11) opera en unmodo inactivo, si la unidad de control (100) del primer chip de memoria (10) determina que el primer chip dememoria (10) cambiará para operar en el modo inactivo de acuerdo con la señal de dirección de entrada (ADDin) elcontrolador de espera (101) del primer chip de memoria (10) cambia el estado de la señal de espera (Sw )desde unestado no declarado a un estado declarado de acuerdo con la primera señal de control correspondiente (CS1); yen donde cuando el receptor de espera (112) del segundo chip de memoria (11) detecta que el estado de la señal deespera (Sw) ha cambiado desde el estado no declarado al estado declarado, en la unidad de control (110) delsegundo chip de memoria (11) determina que el segundo chip de memoria (11) va a cambiar para operar en el modoactivo después de que la última línea de palabra en el primer chip de memoria (10) es accesada de acuerdo con laseñal de dirección de entrada (ADDin) y la segunda señal de control correspondiente (CS2_b).

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E10170014.

Solicitante: Winbond Electronics Corp.

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: No. 8 Keya 1st Rd., Daya District, Central Taiwan Science Park Taichung City, Taiwan TAIWAN.

Inventor/es: SUN,CHI HSIANG.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C8/12 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 8/00 Disposiciones para seleccionar una dirección en una memoria digital (circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Circuitos de selección de grupo, p. ej. para la selección de un bloque de memoria, la selección de un circuito integrado, la selección de una red de celdas.

PDF original: ES-2394652_T3.pdf

Fragmento de la descripción:

Chips de memoria y dispositivos que los emplean Antecedentes de la Invención Campo de la Invención La invención se relaciona con un chip de memoria, y más particularmente con un dispositivo de memoria que puede detectar la ocurrencia una operación de cruce de límite de extinción entre dos chips de memoria al monitorear una tableta de espera.

Descripción de la Técnica Relacionada Para un chip de memoria convencional, tal como un chip CRAM (RAM celular) , después de que la última palabra en una línea de palabra activa se lee/se escribe, se efectúa una operación de cruce de límite para conmutar la operación de lectura/escritura a la siguiente línea de palabra; esto es, la línea de palabra se vuelve inactiva mientras que la siguiente línea de palabra se vuelve activa. La operación e lectura/escritura se puede efectuar continuamente en la siguiente línea de palabra. Cuando se efectúa la operación de cruce de límite, se declara una señal en la tableta de espera del chip de memoria hasta que se activa la siguiente línea de palabra. Así, al monitorear la tableta de espera, los usuarios pueden conocer el estado de la operación de lectura/escritura.

En algunas aplicaciones, se pueden apilar por lo menos dos chips de memoria para formar un dispositivo de memoria. Se puede efectuar una operación de cruce del límite entre la última línea de palabra de un chip de memoria superior y la primera línea de palabra de un chip de memoria inferior; esto es, la última línea de palabra del chip de memoria superior se vuelve inactiva mientras que la primer línea de palabra del chip de memoria inferior se vuelve activa. En este caso, la operación de cruce de límite se denomina como “operación de cruce de límite de extinción”.

El documento US 2007/0 143 556 describe la activación cíclica de chips de memoria. Una vez que una hilera de un chip se ha accedido completamente, se selecciona para acceso un siguiente chip.

Así, se desea suministrar un dispositivo de memoria que pueda detectar la ocurrencia de una operación de cruce de límite entre dos chips de memoria.

Breve Resumen de la Invención Una realización de ejemplo de un dispositivo de memoria comprende un primer chip de memoria y un segundo chip de memoria. Tanto el primero como el segundo chip de memoria reciben una señal de dirección de entrada y al menos una señal de comando. Tanto el primer como el segundo chip de memoria están acoplados a una tableta de espera. El primer chip de memoria y el segundo chip de memoria operan alternativamente en un modo activo, y cada uno del primer chip de memoria y el segundo chip de memoria comprenden una unidad de control, o un controlador de espera, y un receptor de espera. La unidad de control recibe la señal de dirección de entrada y la al menos una señal de comando determina y controla un modo de operación del chip de memoria correspondiente de acuerdo con la señal de dirección de entrada y la al menos una señal de comando, y genera una primera señal de control de acuerdo con el resultado de determinación. El controlador de espera se acopla a la tableta de espera. El controlador de espera recibe adicionalmente la primera señal de control y cambia un estado de una señal de espera a una tableta de espera de acuerdo con la primera señal de control. El receptor de espera se acopla a la tableta de espera para recibir la señal de espera y detecta el estado de la señal de espera para generar una segunda señal de control. Cuando el primer chip de memoria opera en un modo activo y el segundo chip de memoria opera en un modo inactivo, si la unidad de control de la primera memoria determina que el primer chip de memoria cambiará para operar en modo inactivo de acuerdo con la señal de dirección de entrada, el controlador de espera de la primera memoria cambia el estado de la señal de espera de un estado no declarado a un estado declarado de acuerdo con la primera señal de control correspondiente. Cuando el receptor de espera del segundo chip de memoria detecta que el estado de la señal de espera se ha cambiado del estado no declarado al estado declarado, la unidad de control del segundo chip de memoria determina que el segundo chip de memoria es cambiado para operar en modo activo después de que la última línea de palabra del primer chip de memoria es accedida de acuerdo con la señal de dirección de entrada y la segunda señal de control correspondiente.

Se da una descripción detallada de las siguientes realizaciones con referencia a los dibujos que la acompañan.

Breve Descripción de los Dibujos La invención se puede entender más completamente al leer la siguiente descripción detallada y los ejemplos con referencias hechas a los dibujos que la acompañan, en donde:

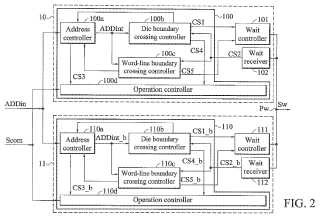

La Fig. 1 muestra una realización de ejemplo de un chip de memoria; La Fig. 2 muestra una realización de ejemplo de un dispositivo de memoria;

La Fig. 3 muestra una tabla de tiempo de la señal de memoria en la Fig. 2;

La Fig. 4 es un diagrama de flujo de una realización de ejemplo del método de operación del dispositivo de memoria en la Fig. 2;

La Fig. 5 es un diagrama de flujo de otra realización de ejemplo del método de operación del dispositivo de memoria en la Fig. 2.

Descripción Detallada de la Invención La siguiente descripción es el mejor modo contemplado de llevar a cabo la invención. Esta descripción se hace con el propósito de ilustrar los principios generales de la invención y no se debe tomar en un sentido limitante. El alcance de la invención se determina mejor mediante referencia a las reivindicaciones finales.

Se suministran chips de memoria. En una realización de ejemplo de un chip de memoria 10 en la Fig. 1, un chip de memoria 10 recibe una señal de dirección de entrada ADDin y al menos una señal de comando Scom. Más aún, el chip de memoria 10 se acopla a una tableta de espera Pw. Como se muestra en la Fig. 1, el chip de memoria 10 comprende una unidad de control 100, un controlador de espera 101, y un receptor de espera 102. La señal de dirección de entrada ADDin se suministra a la unidad de control 100. En la realización, la señal de dirección de entrada ADDin puede ser ingresada por un usuario o un dispositivo de módulo de interfaz. La unidad de control 100 determina y controla el modo de operación del chip de memoria 10, tal como un modo activo o un modo inactivo, de acuerdo con la señal de dirección de entrada ADDin y al menos una señal de comando Scom y genera una señal de control CS1 de acuerdo al resultado de determinación. El controlador de espera 101 se acopla a la tableta de espera Pw y recibe la señal de control CS1 de la unidad de control 100. El controlador de espera 101 cambia un estado de una señal de espera Sw a la tableta de espera Pw de acuerdo con la señal de control CS1. El receptor de espera 102 se acopla a la tableta de espera Pw para recibir la señal de espera Sw. El receptor de espera 102 detecta además el estado de la señal de espera Sw para generar una señal de control CS2 a la unidad de control 100.

Asumir que el chip de memoria 10 opera en un modo activo. Cuando la unidad de control 100 determina que el chip de memoria 10 se cambiará para operar en el modo inactivo de acuerdo con la señal de dirección de entrada ADDin y al menos una señal de comando Scom, el controlador de espera 101 cambia el estado de la señal de espera Sw de un estado no declarado a un estado declarado de acuerdo con la señal de control SC1. Después, el chip de memoria 10 se cambia para operar en el módulo inactivo. De otro lado, cuando el chip de memoria 10 opera en el modo inactivo y el receptor de espera 102 detecta que el estado de la señal de espera Sw se ha cambiado del estado no declarado al estado declarado para generar la señal de control CS2, la unidad de control 100 determina si el chip de memoria 10 se cambiara para operar en el modo activo de acuerdo con la señal de dirección de entrada ADDin y la señal de control CS2. Después de que la unidad de control 100 determina que el chip de memoria 10 cambiara para operar en el modo activo, la unidad de control 100 controla el chip de memoria 10 para operar en el modo activo.

La descripción detallada de las operaciones del chip de memoria 10 se describirá en lo que sigue. Como se muestra en la Fig. 1 la unidad de control 100 comprende un controlador de dirección 100a, y un controlador de cruce de límite de extinción 100b, un controlador de cruce de límite de línea de palabras 100c, y un controlador de operación 100d. El controlador de dirección 100a recibe la señal de dirección de entrada ADDin y genera una señal de dirección interna ADDint y una señal de control CS3 de acuerdo con la señal de dirección de entrada ADDin. La señal de dirección... [Seguir leyendo]

Reivindicaciones:

1. Un dispositivo de memoria que comprende:

un primer chip de memoria (10) para recibir una señal de dirección de entrada (ADDin) y acoplado a una tableta de espera (Pw) ; y

un segundo chip de memoria (11) para recibir la señal de dirección de entrada (ADDin) y acoplado a la tableta de espera (Pw) , en donde el primer chip de memoria (10) y el segundo chip de memoria (11) operan alternativamente en un modo activo,

en donde cada uno del primer chip de memoria (10) y el segundo chip de memoria (11) comprende:

una unidad de control (100, 110) para recibir la señal de dirección de entrada ADDin y al menos una señal de comando (Scom) , que determina y controla un modo de operación del chip de memoria correspondiente de acuerdo con la señal de dirección de entrada (ADDin) y al menos una señal de comando (Scom) , y generar una primer señal de control (CS1, CS1_b) de acuerdo al resultado de determinación;

un controlador de espera (101, 111) acoplado a la tableta de espera, (Pw) , para recibir la primera señal de control (CS1) y cambiar un estado de una señal de espera (Sw) a la tableta de espera (Pw) de acuerdo con la primera señal de control (CS1, CS1_b) ; y un receptor de espera (102, 112) , acoplado a una tableta de espera (Pw) , para recibir la señal de espera (Sw) y detectar el estado de la señal de espera (Sw) para generar una segunda señal de control (CS2, CS2_b) .

en donde el primer chip de memoria (10) opera en un modo activo y el segundo chip de memoria (11) opera en un modo inactivo, si la unidad de control (100) del primer chip de memoria (10) determina que el primer chip de memoria (10) cambiará para operar en el modo inactivo de acuerdo con la señal de dirección de entrada (ADDin) el controlador de espera (101) del primer chip de memoria (10) cambia el estado de la señal de espera (Sw ) desde un estado no declarado a un estado declarado de acuerdo con la primera señal de control correspondiente (CS1) ; y

en donde cuando el receptor de espera (112) del segundo chip de memoria (11) detecta que el estado de la señal de espera (Sw) ha cambiado desde el estado no declarado al estado declarado, en la unidad de control (110) del segundo chip de memoria (11) determina que el segundo chip de memoria (11) va a cambiar para operar en el modo activo después de que la última línea de palabra en el primer chip de memoria (10) es accesada de acuerdo con la señal de dirección de entrada (ADDin) y la segunda señal de control correspondiente (CS2_b) .

2. El chip de memoria como se reivindicó en la reivindicación 1, en donde para cada uno del primer chip de memoria (10) y el segundo chip de memoria (11) , la unidad de control (100, 110) comprende:

un controlador de dirección (100a, 110a) para recibir la señal de dirección de entrada (ADDin) y generar una señal de dirección interna (ADDint, ADDint_b) una tercera señal de control (CS3, CS3_b) de acuerdo con la señal de dirección de entrada (ADDin) ;

un primer controlador de cruce de límite (100b, 110b) , para recibir la señal de dirección interna (ADDint, ADDint_b) y la segunda señal de control (CS2, CS2_b) , determinando si el modo de operación del chip de memoria correspondiente se cambiará de acuerdo con la señal de dirección interna (ADDint, ADDint_b) y la segunda señal de control (CS2, CS2_b) , y generar la primera señal de control (CS1, CS1_b) y la cuarta señal de control (CS4, CS4_b) , de acuerdo al resultado de determinación; y

un controlador de operación (100d, 110d) para recibir la tercera señal de control (CS3, CS3_b) y la cuarta señal de control (CS4, CS4_b) y la al menos una señal de comando (Scom) y controlar la operación del chip de memoria correspondiente de acuerdo con la tercera señal de control (CS3, CS3_b) y la cuarta señal de control (CS4, CS4_b) .

3. El dispositivo de memoria como se reivindicó en la reivindicación 2, en donde cuando el controlador de operación (100d) del primer chip de memoria (10) controla el primer chip de memoria (10) para operar en el modo activo de acuerdo con la tercera señal de control correspondiente (CS3, CS3_b) y la al menos una señal de comando (Scom) y el controlador de operación (110d) del segundo chip de memoria (11) controla el segundo chip de memoria (11) para operar en el modo inactivo de acuerdo con la tercera señal de control correspondiente (CS3, CS3_b) y la al menos una señal de comando (Scom) , si el primer controlador de cruce de límite (100b) del primer chip de memoria (10) determina que el primer chip de memoria (10) cambiará para operar en el modo inactivo de acuerdo con la señal de dirección interna correspondiente (ADDint, ADDint_b) el controlador de espera (101) del primer chip de memoria (10) cambia el estado de la señal de espera (Sw) desde el estado no declarado al estado declarado de acuerdo con la primera señal de control correspondiente (CS1) , el primer controlador de cruce de límite (100b) del primer chip de memoria (10) actualiza el controlador de dirección (100a) y el primer chip de memoria (10)

para cambiar la señal de dirección interna correspondiente (ADDint, ADDint_b) , y el primer controlador de cruce de límite (100b) del segundo chip de memoria (11) actualiza el controlador de dirección (110a) del segundo chip de memoria (11) de acuerdo con la segunda señal de control correspondiente (CS2) para cambiar la señal de dirección interna correspondiente (ADDint, ADDint_b) .

4. El dispositivo de memoria como se reivindicó en la reivindicación 1, en donde después de que el controlador de espera (101) del primer chip de memoria (10) cambia el estado de la señal de espera (Sw) desde el estado no declarado al estado declarado de acuerdo con la primera señal de control correspondiente (CS1) , el controlador de operación (100d) del primer chip de memoria (10) controla el primer chip de memoria (10) para operar en el modo inactivo de acuerdo con la cuarta señal de control correspondiente (CS4, CS4_b) , y el controlador de operación (110d) del segundo chip de memoria (11) controla el segundo chip de memoria (11) para operar en el modo activo de acuerdo con la cuarta señal de control correspondiente (CS4, CS4_b) .

5. El dispositivo de memoria como se reivindicó en la reivindicación 3, en donde cuando el receptor de espera

(112) del segundo chip de memoria (11) detecta que el estado de la señal de espera (Sw) ha cambiado desde el estado no declarado al estado declarado, el primer controlador de cruce de límite (110b) del segundo chip de memoria (11) determina si el segundo chip de memoria (11) cambiará para operar en el modo activo de acuerdo con la señal de dirección interna correspondiente (ADDint, ADDint_b) y la segunda señal de control correspondiente (CS2) ; y

en donde si el primer controlador de cruce de límite (110b) del segundo chip de memoria (11) determina que el segundo chip de memoria (11) cambiará para operar en el modo activo, el primer controlador de cruce de límite (110b) del segundo chip de memoria (11) actualiza el controlador de dirección (110a) del segundo chip de memoria

(11) de acuerdo con la segunda señal de control correspondiente para cambiar la señal de dirección interna correspondiente (ADDint, ADDint_b) , y el primer controlador de cruce de límite (100b) del primer chip de memoria

(10) actualiza el controlador de dircción (100a) del primer chip de memoria (10) para cambiar la señal de dirección interna correspondiente (ADDint, ADDint_b) .

6. El dispositivo de memoria como se reivindicó en la reivindicación 5, en donde después de que el primer controlador de cruce de límite (110b) del segundo chip de memoria (11) determina que el segundo chip de memoria (11) cambiará para operar en el modo activo, el controlador de operación (110d) de la segunda memoria controla el segundo chip de memoria (11) para operar en el modo activo de acuerdo con la cuarta señal de control correspondiente (CS4, CS4_b) , y el controlador de operación (100d) del primer chip de memoria (10) controla el primer chip de memoria (10) para operar en el modo inactivo de acuerdo con la cuarta señal de control correspondiente (CS4, CS4_b) .

7. El dispositivo como se reivindicó en la reivindicación 2, para cada uno del primer chip de memorias (10) y el segundo chip de memoria (11) , en donde la unidad de control (100, 110) comprende además:

un segundo controlador de cruce de límite (100c, 110c) , para recibir la señal de dirección interna (ADDint, ADDint_b) , determinando si una operación de cruce de límite de línea de palabra del correspondiente chip de memoria se efectuará en el correspondiente chip de memoria de acuerdo con la señal de dirección interna (ADDint, ADDint_b) cuando el controlador de operación (100d, 110d) controla el chip de memoria correspondiente para operar en el modo activo de acuerdo con la tercera señal de control (CS3, CS3_b) y la al menos una señal de comando (Scom) , y generando una quinta señal de control (CS5, CS5_b) de acuerdo al resultado de determinación para el controlador de espera (101, 111) .

8. El dispositivo de memoria como se reivindicó en la reivindicación 7, en donde cuando el controlador de operación (100d, 110d) controla el correspondiente chip de memoria para operar en el nodo activo de acuerdo con la tercera señal de control (CS3, CS3_b) y la al menos una señal de comando (Scom) , si el segundo controlador de cruce de límite (100c, 110c) determina que la operación de cruce de límite del correspondiente chip de memoria se efectuará, el controlador de espera (101, 111) cambia el estado de la señal de espera (Sw) desde el estado no declarado al estado declarado de acuerdo con la quinta señal de control (CS5, CS5_b) , y el segundo controlador de cruce de límite (100c, 110c) actualiza el controlador de dirección (100a, 110a) para cambiar la señal de dirección interna (ADDint, ADDint_b) .

9. El dispositivo de memoria como se reivindicó en la reivindicación 8, en donde después de que el controlador de espera (101, 111) cambia el estado de la señal de espera (Sw) desde el estado no declarado al estado declarado, se efectúa la operación de cruce de límite del chip de memoria correspondiente.

10. El dispositivo de memoria como se reivindicó en la reivindicación 7, en donde para cada uno del primer chip de memoria (10) y el segundo chip de memoria (11) , el segundo controlador de cruce de límite (100c, 110c) determina además si la operación de cruce de límite de línea de palabra se efectuará en el otro chip de memoria de acuerdo con la señal de dirección interna (ADDint, ADDint_b) y la segunda señal de control (CS2) ; y si el segundo controlador de cruce de límite (100c, 110c) determina que la operación de cruce de límite de línea de palabra se efectuará en el otro chip de memoria, el segundo controlador de cruce de límite (100c, 110c) actualiza el controlador de dirección (100a, 110a) para cambiar la señal de dirección interna (ADDint, ADDint_b) .

Controlador

Controlador de cruceControlador

de

de límite de extinción de

dirección espera

ReceptordeControlador de cruceesperade límite delínea de palabra Controlador de Operación

ControladordeDirección

ControladordeDirección Controlador de crucede límite de extinción

Controlador de cruce de límite de línea de palabra

Controlador de Operación

Controlador de crucede límite de extinción Controlador de cruce de límite de línea de palabra

Controlador de Operación Controlador de Espera

ReceptordeEspera

Controlador de Espera

ReceptordeEspera

no declaradoalto Z declarado

Patentes similares o relacionadas:

Direccionamiento tridimensional para memoria, del 25 de Marzo de 2020, de HEWLETT-PACKARD DEVELOPMENT COMPANY, L.P.: Dispositivo de memoria del cabezal de impresión , que comprende: una serie de bancos de memoria de solo lectura programables (EPROM) borrables (114-1, 114-N), […]

Banco de memoria dividido, del 12 de Febrero de 2020, de HEWLETT-PACKARD DEVELOPMENT COMPANY, L.P.: Un cartucho de impresión integrado que comprende un depósito de tinta , una matriz de chorro de fluido , un cable flexible , almohadillas […]

Sistema y procedimiento para reducir el esfuerzo de tensión de programación en dispositivos de celdas de memoria, del 8 de Enero de 2020, de QUALCOMM INCORPORATED: Una memoria OTP programable una vez , que comprende: una primera línea de palabra global (GWL1); un primer conjunto de líneas […]

Dispositivo de memoria híbrida con una única interfaz, del 23 de Enero de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento que comprende: recibir, en un controlador , órdenes, direcciones y datos en un dispositivo de memoria mediante una interfaz definida asociada […]

Difusión general selectiva de datos en dispositivos conectados en serie, del 9 de Abril de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Método para seleccionar un subconjunto de dispositivos de una pluralidad de dispositivos conectados en serie a un controlador de memorias con el fin […]

Métodos y aparatos para la sincronización de señal de reloj en una configuración de dispositivos semiconductores conectados en serie, del 9 de Octubre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un aparato , que comprende: - un controlador del sistema ; y - una configuración de dispositivos semiconductores conectados […]

Control de decodificación con detección de transición de dirección en función de borrado de página, del 19 de Septiembre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Una memoria no volátil que comprende bloques de memoria , cada bloque de memoriacomprende: celdas de memoria no volátil dispuestas en una pluralidad […]

ARQUITECTURA DE MEMORIA FLASH QUE IMPLEMENTA MULTIPLES BANCOS DE MEMORIA FLASH PROGRAMABLES SIMULTANEAMENTE, QUE SON COMPATIBLES CON UNA CENTRAL, del 1 de Mayo de 2008, de LEXAR MEDIA, INC.: Un sistema de memoria flash que comprende una pluralidad de bancos de memoria separados y direccionables independientemente (1020, 1022, 1024, […]

ARQUITECTURA DE MEMORIA FLASH QUE IMPLEMENTA MULTIPLES BANCOS DE MEMORIA FLASH PROGRAMABLES SIMULTANEAMENTE, QUE SON COMPATIBLES CON UNA CENTRAL, del 1 de Mayo de 2008, de LEXAR MEDIA, INC.: Un sistema de memoria flash que comprende una pluralidad de bancos de memoria separados y direccionables independientemente (1020, 1022, 1024, […]