Métodos y aparatos para la sincronización de señal de reloj en una configuración de dispositivos semiconductores conectados en serie.

Un aparato (502), que comprende:

- un controlador del sistema (102);

y

- una configuración de dispositivos semiconductores conectados en serie (104-0, 104-1, ... , 104-7);

- estando adaptado el controlador del sistema (102) para comunicar con dicha configuración, comprendiendo elcontrolador del sistema:

- una salida configurada para proporcionar una primera señal de reloj a un primer dispositivo (104-0) en laconfiguración;

- una entrada configurada para recibir una segunda señal de reloj procedente de un último dispositivo (104-7) en laconfiguración, correspondiendo la segunda señal de reloj a una versión de la primera señal de reloj que ha sidosometida a procesamiento mediante el sincronizador de reloj (110), por lo menos, en uno de los dispositivos (104-0,104-1, ..., 104-7) en la configuración;

- un detector para procesar la primera y la segunda señales de reloj a efectos de detectar una diferencia de faseentre ambas; y

- un controlador (106) configurado para ordenar un ajuste al sincronizador de reloj, por lo menos en uno de dichosdispositivos en la configuración, en base a la diferencia de fase detectada por el detector.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E11009644.

Solicitante: MOSAID TECHNOLOGIES INCORPORATED.

Nacionalidad solicitante: Canadá.

Dirección: 11 Hines Road, Suite 203 Ottawa, ON K2K 2X1 CANADA.

Inventor/es: OH,HakJune.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F1/10 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 1/00 Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76). › Distribución de las señales de reloj.

- G11C19/00 G […] › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › Memorias digitales en las que la información es movida por escalones, p. ej. registros de desplazamiento.

- G11C8/12 G11C […] › G11C 8/00 Disposiciones para seleccionar una dirección en una memoria digital (circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Circuitos de selección de grupo, p. ej. para la selección de un bloque de memoria, la selección de un circuito integrado, la selección de una red de celdas.

- G11C8/18 G11C 8/00 […] › Circuitos de sincronización o de reloj; Generación o gestión de señales de control de dirección, p. ej. para las señales de selección de dirección de línea [RAS] o de selección de dirección de columna [CAS].

- H03L7/081 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › con un desfasador controlado adicional.

PDF original: ES-2441951_T3.pdf

Fragmento de la descripción:

Métodos y aparatos para la sincronización de señal de reloj en una configuración de dispositivos semiconductores conectados en serie.

REFERENCIA CRUZADA A SOLICITUD RELACIONADA

Esta solicitud reivindica el beneficio de la anterior solicitud de patente provisional de U.S.A. número 60/894 246, presentada el 12 de marzo de 2007.

CAMPO DE LA INVENCIÓN

La presente invención se refiere, en general, a dispositivos semiconductores, y más en particular, a métodos y aparatos para sincronizar una señal de reloj propagada a lo largo de una configuración de dichos dispositivos conectados en serie.

ANTECEDENTES

Los sistemas basados en ordenadores contienen habitualmente dispositivos semiconductores, tales como, por ejemplo, memorias. Los dispositivos semiconductores están controlados por medio de un controlador, que puede formar parte de la unidad central de procesamiento (CPU, central processing unit) del ordenador o puede ser independiente de la misma. El controlador tiene una interfaz para comunicar información con los dispositivos semiconductores. Cuando se desea una comunicación con una serie de dispositivos semiconductores, son posibles varias configuraciones. En particular, puede formarse una configuración de dispositivos semiconductores conectados en serie mediante conectar dispositivos semiconductores entre sí a través de sus interfaces, en un esquema punto a punto.

El documento US 2004/148482 A1 se refiere a un sistema de memoria que tiene una serie de dispositivos de memoria y un controlador de memoria. Los dispositivos de memoria están acoplados entre sí en una cadena. El controlador de memoria está acoplado a la cadena y configurado para emitir un comando de acceso a la memoria, que es recibido por cada uno de los dispositivos de memoria de la cadena, y se selecciona un conjunto de dos o más de dichos dispositivos de memoria para su acceso.

El documento US 2007/046346 A1 da a conocer un controlador de reloj para utilizar con un excitador externo al chip, e incluye un primer elemento de retardo, un segundo elemento de retardo, un circuito de restablecimiento y un circuito de ajuste. El controlador de reloj incluye un nodo que recibe un reloj de referencia representado, por lo menos, por una señal de reloj. El primer elemento de retardo está configurado para retardar una de dicha por lo menos una señal de reloj, mediante un primer tiempo de retardo, y el segundo elemento de retardo está configurado para retardar una de dicha por lo menos una señal de reloj, mediante un segundo tiempo de retardo. El circuito de restablecimiento está configurado para proporcionar por lo menos un primer reloj de salida al excitador externo al chip, en el que el excitador externo al chip proporciona datos de salida en base, por lo menos, al primer reloj de salida. El circuito de ajuste está configurado para ajustar el primer y el segundo tiempos de retardo a efectos de ajustar los flancos del primer reloj de salida, de manera que los datos de salida procedentes del excitador externo al chip estén alineados con los flancos del reloj de referencia, y para ajustar el segundo tiempo de retardo a efectos de mantener el primer reloj de salida en un ciclo de trabajo deseado.

RESUMEN DE LA INVENCIÓN

De acuerdo con un primer aspecto general, la presente invención pretende dar a conocer un dispositivo semiconductor para su utilización en una configuración de dispositivos conectados en serie. El dispositivo semiconductor comprende una entrada para recibir una señal de reloj originada en un dispositivo anterior en la configuración; una salida para proporcionar una señal de reloj sincronizada destinada a un dispositivo sucesivo en la configuración; un sincronizador de reloj configurado para producir la señal de reloj sincronizada mediante procesar la señal de reloj recibida y la versión anterior de la señal de reloj sincronizada; y un controlador configurado para ajustar un parámetro utilizado por el sincronizador de reloj en el procesamiento de dicha versión anterior de la señal de reloj sincronizada.

De acuerdo con un segundo aspecto general, la presente invención pretende dar a conocer un método, que comprende recibir una señal de reloj originada en un dispositivo anterior en una configuración de dispositivos conectados en serie; producir una señal de reloj sincronizada destinada a un dispositivo sucesivo en dicha configuración, mediante procesar la señal de reloj recibida y una versión anterior de la señal de reloj sincronizada; ajustar un parámetro utilizado por el sincronizador de reloj en el procesamiento de la versión anterior de dicha señal de reloj sincronizada; y entregar dicha señal de reloj sincronizada.

De acuerdo con un tercer aspecto general, la presente invención pretende dar a conocer un sistema, que comprende: una configuración de dispositivos semiconductores conectados en serie; y un controlador configurado para producir una señal de reloj que es transmitida a un primer dispositivo de los dispositivos en dicha configuración, propagada en serie a través de otros de los dispositivos en la configuración, y devuelta al controlador mediante el último de los dispositivos de la configuración, en el que una versión respectiva de la señal de reloj en cada uno de los dispositivos en la configuración controla el funcionamiento de dicho dispositivo. Por lo menos uno de los dispositivos de la configuración comprende un respectivo sincronizador de reloj configurado para procesar la versión respectiva de la señal de reloj para su distribución a un dispositivo sucesivo de los dispositivos de la configuración, o para devolverla al controlador. El controlador está configurado además para ajustar un parámetro de, por lo menos, un sincronizador de reloj, en base al procesamiento de la señal de reloj transmitida al primero de los dispositivos de la configuración y a la señal de reloj devuelta por el último de los dispositivos en la configuración.

De acuerdo con un cuarto aspecto general, la presente invención pretende dar a conocer un método, que comprende proporcionar una primera señal de reloj a un primer dispositivo en una configuración de dispositivos semiconductores conectados en serie; recibir una segunda señal de reloj desde un segundo dispositivo en dicha configuración, correspondiendo dicha segunda señal de reloj a una versión de la primera señal de reloj que ha sido sometida a procesamiento mediante el sincronizador de reloj en, por lo menos, uno de los dispositivos de la configuración; procesar la primera y la segunda señales de reloj para detectar una diferencia de fase entre ambas; y ordenar un ajuste al sincronizador de reloj, por lo menos, en uno de los dispositivos de la configuración, en base a la diferencia de fase.

De acuerdo con un quinto aspecto general, la presente invención pretende dar a conocer un controlador para una configuración de dispositivos semiconductores conectados en serie. El controlador comprende una salida configurada para proporcionar una primera señal de reloj a un primer dispositivo de la configuración; una entrada configurada para recibir una segunda señal de reloj procedente de un segundo dispositivo de la configuración, correspondiendo la segunda señal de reloj a una versión de la primera señal de reloj que ha sido sometida a procesamiento mediante un sincronizador de reloj, por lo menos, en uno de los dispositivos de la configuración; un detector para procesar la primera y la segunda señales de reloj a efectos de detectar una diferencia de fase entre ambas; y un controlador de sincronización configurado para ordenar un ajuste al sincronizador de reloj, por lo menos, en uno de los dispositivos de la configuración, en base a la diferencia de fase detectada por el detector.

Estos y otros aspectos y características de la presente invención resultarán más evidentes a los expertos en la materia tras examinar la siguiente descripción de realizaciones específicas de la invención, junto con los dibujos adjuntos.

BREVE DESCRIPCIÓN DE LOS DIBUJOS

A continuación se describirán realizaciones de la presente invención, solo a modo de ejemplo, haciendo referencia a los dibujos adjuntos, en los cuales:

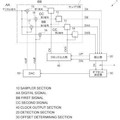

la figura 1 es un diagrama de bloques que muestra un sistema acorde con una realización de la presente invención, incluyendo el sistema una configuración de dispositivos semiconductores conectados en serie, en comunicación con un controlador del sistema;

la figura 2A es un diagrama de bloques que muestra detalles de uno de los dispositivos de la figura 1, de acuerdo con un ejemplo no limitativo de realización de la presente invención;

la figura 2B es un diagrama de bloques que muestra detalles adicionales de uno de los dispositivos mostrados... [Seguir leyendo]

Reivindicaciones:

1. Un aparato (502) , que comprende:

- un controlador del sistema (102) ; y

- una configuración de dispositivos semiconductores conectados en serie (104-0.

10. 1, ... .

10. 7) ;

- estando adaptado el controlador del sistema (102) para comunicar con dicha configuración, comprendiendo el controlador del sistema:

- una salida configurada para proporcionar una primera señal de reloj a un primer dispositivo (104-0) en la configuración;

- una entrada configurada para recibir una segunda señal de reloj procedente de un último dispositivo (104-7) en la configuración, correspondiendo la segunda señal de reloj a una versión de la primera señal de reloj que ha sido sometida a procesamiento mediante el sincronizador de reloj (110) , por lo menos, en uno de los dispositivos (104-0.

10. 1, ....

10. 7) en la configuración;

- un detector para procesar la primera y la segunda señales de reloj a efectos de detectar una diferencia de fase entre ambas; y

- un controlador (106) configurado para ordenar un ajuste al sincronizador de reloj, por lo menos en uno de dichos dispositivos en la configuración, en base a la diferencia de fase detectada por el detector.

2. El aparato (502) según la reivindicación 1, en el que para ordenar el ajuste, el controlador está configurado para emitir un comando para efectuar un ajuste a un retardo que está siendo aplicado mediante un trayecto de retroalimentación en el sincronizador de reloj, en dicho por lo menos uno de dichos dispositivos de la configuración.

3. El aparato (502) según la reivindicación 2, en el que dicho ajuste es un aumento incremental o una reducción incremental basados en la diferencia de fase.

4. El aparato (502) según la reivindicación 2 o la reivindicación 3, en el que cuando el comando es emitido a una serie de los dispositivos de la configuración, el ajuste de es distribuido de manera sustancialmente uniforme en la totalidad de dicha pluralidad de los dispositivos de la configuración.

5. El aparato (502) según la reivindicación 2 o la reivindicación 3, en el que el controlador está configurado para determinar si la magnitud de la diferencia de fase excede un valor umbral y, en caso afirmativo, para emitir el comando a un subconjunto de los dispositivos de la configuración, siendo el número de dispositivos de dicho subconjunto una función de la magnitud de la diferencia de fase.

6. El aparato (502) según la reivindicación 5, en el que si la magnitud de la diferencia de fase no excede el valor umbral pero excede un segundo valor umbral, el controlador está configurado para emitir un primer comando a uno de los dispositivos de la configuración, y emitir a continuación un segundo comando a un nuevo subconjunto de dispositivos en la configuración, siendo el número de dispositivos de dicho nuevo subconjunto una función de la magnitud de una nueva lectura de la diferencia de fase obtenida del detector.

7. El aparato (502) según la reivindicación 2 o la reivindicación 3, en el que el controlador está configurado para determinar si la magnitud de la diferencia de fase excede un valor umbral y, en caso afirmativo, emitir el comando a todos los dispositivos de la configuración.

8. El aparato (502) según la reivindicación 7, en el que el controlador está configurado para emitir secuencialmente el comando a todos los dispositivos de la configuración.

9. El aparato (502) según la reivindicación 7, en el que el controlador está configurado para difundir el comando a todos los dispositivos de la configuración.

10. Un método para hacer funcionar el aparato (502) según las reivindicaciones 1 a 9, que comprende:

- proporcionar una primera señal de reloj a un primer dispositivo (104-0) en una configuración de dispositivos semiconductores conectados en serie (104-0.

10. 1, ....

10. 7) ;

- recibir una segunda señal de reloj desde el último dispositivo (104-7) de la configuración, correspondiendo la segunda señal de reloj a una versión de la primera señal de reloj que ha sido sometida a procesamiento mediante el sincronizador de reloj (110) , por lo menos en uno de los dispositivos de la configuración;

- procesar la primera y la segunda señales de reloj para detectar una diferencia de fase entre ambas; y

- emitir un comando para ajustar el sincronizador de reloj, por lo menos, en uno de dichos dispositivos de la configuración, en base a la diferencia de fase.

Patentes similares o relacionadas:

Arquitectura central en serie de memoria no volátil, del 3 de Septiembre de 2014, de Conversant Intellectual Property Management Inc: Sistema de memoria que comprende: banco de memoria para suministrar datos de lectura de flujo de bits en serie en respuesta a una operación […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]

METODO PARA LA LECTURA DE UN DISPOSITIVO DIRECCIONABLE POR MATRIZ PASIVA Y DISPOSITIVO PARA LLEVAR A CABO EL MISMO., del 1 de Abril de 2007, de THIN FILM ELECTRONICS ASA: Método para la lectura de un dispositivo direccionable por matriz pasiva, particularmente un dispositivo de memoria o un dispositivo sensor […]

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Circuito para generar señales precisas de fase de reloj para un serializador/deserializador de alta velocidad, del 24 de Noviembre de 2016, de QUALCOMM INCORPORATED: Un circuito para generar cuatro señales de reloj con relaciones de temporización en cuadratura, incluyendo el circuito: un convertidor de lógica de modo de corriente, […]

Sistemas y métodos para proporcionar señales retardadas, del 9 de Abril de 2014, de NIITEK, INC: Un aparato de retardo variable, que comprende: una unidad de retardo variable configurada para recibir una señal de disparo y una serie de entradas de palabra de […]

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

Bucle cerrado de retardo analógico/digital, del 23 de Mayo de 2012, de MOSAID TECHNOLOGIES INCORPORATED: Un bucle cerrado de retardo incluyendo: un circuito de retardo digital que permite que elementos de retardo digital proporcionen ajuste […]