Dispositivos de memoria y procedimientos de operación de los mismos.

Un dispositivo (100, 1620) de memoria, siendo el dispositivo (100,

1620) de memoria una memoria dinámica de acceso aleatorio, DRAM, y que comprende:

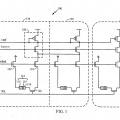

una matriz (180) de memoria que incluye un primer grupo de células (21, 22, 23) de memoria y un segundo grupo de células (21, 22, 23) de memoria acopladas a una pluralidad de líneas (221, 222, 223, 224, 321, 322) de bits y una pluralidad de líneas (211, 212, 213, 214, 215, 216, 217, 218) de palabras;

una pluralidad de circuitos (130) de los amplificadores de detección acoplados a la pluralidad de líneas (221, 222, 223, 224, 321, 322) de bits, en el que cada circuito (130) del amplificador de detección incluye un amplificador (251, 252, 253, 254, 330) de detección y está configurado para detectar y amplificar una diferencia de tensión entre dos de las líneas (221, 222, 223, 224, 321, 322) de bits acopladas a los mismos,

en el que la pluralidad de circuitos (130) de los amplificadores de detección incluye además:

una pluralidad (520, 820, 860, 1020, 1060) de conmutadores de bloqueo acoplados a aquellas correspondientes de las líneas (221, 222, 223, 224, 321, 322) de bits a las que se acopla el primer grupo de células (21, 22, 23) de memoria;

una pluralidad de bloqueos (540, 840, 880, 1040, 1080) acoplados a través de la pluralidad de conmutadores (520, 820, 860, 1020, 1060) de bloqueo a las líneas (221, 222, 223, 224, 321, 322) de bits a las que se acopla el primer grupo de células (21, 22, 23) de memoria,

en el que cada circuito (130) del amplificador de detección incluye uno de los conmutadores (520, 820, 860, 1020, 1060) de bloqueo y uno de los bloqueos (540, 840, 880, 1040, 1080),

en el que cada conmutador (520, 820, 860, 1020, 1060) de bloqueo permite el bloqueo de datos en el bloqueo (540, 840, 880, 1040, 1080) acoplado al mismo;

en el que el segundo grupo de células (21, 22, 23) de memoria está acoplado a las líneas (221, 222, 223, 224, 321, 322) de bits a las que se acopla el primer grupo de células (21, 22, 23) de memoria;

un decodificador (140) de direcciones configurado para recibir y decodificar las direcciones del primer grupo de células de memoria y del segundo grupo de células (21, 22, 23) de memoria para habilitar las correspondientes de las líneas (221, 222, 223, 224 ,321, 322) de bits y las líneas (211, 212, 213, 214, 215, 216, 217, 218) de palabras;

un controlador de actualización (160) configurado para controlar la actualización de datos de las células (201, 202) de memoria; y

un controlador (120) de modo configurado para controlar el dispositivo (100, 1620) de memoria para operar en diferentes modos de operación, incluido un modo de apagado profundo, DPD,

en el que el controlador (120) de modo está configurado para controlar los correspondientes de los bloqueos (540, 840, 880, 1040, 1080) y amplificadores (251, 252, 253, 254, 330) de detección para que los datos del primer grupo de las células (21, 22, 23) de memoria se encierren en los bloqueos (540, 840, 880, 1040, 1080) correspondientes acoplados a los mismos a través de las líneas (221, 222, 223, 224, 321, 322) de bits mientras que los datos del segundo grupo de células (21, 22, 23) de memoria se bloquea en los amplificadores (251, 252, 253, 254, 330) de detección correspondientes acoplados a los mismos a través de las líneas (221, 222, 223, 224, 321, 322) de bits cuando el dispositivo (100, 1620) de memoria entra al modo DPD.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E18151717.

Solicitante: Winbond Electronics Corp.

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: No. 8 Keya 1st Rd. Daya District Central Taiwan Science Park 42881 Taichung City TAIWAN.

Inventor/es: PARK,SAN-HA.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C11/406 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 11/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento eléctricos o magnéticos particulares; Elementos de almacenamiento correspondientes (G11C 14/00 - G11C 21/00 tienen prioridad). › Organización o control de los ciclos de de refresco o de regeneración de la carga.

- G11C11/4072 G11C 11/00 […] › Circuitos para la inicialización, para la puesta en o fuera de tensión, para el borrado de la memoria o para el preajuste.

- G11C11/4074 G11C 11/00 […] › Circuitos de alimentación o de generación de tensión, p. ej. generadores de tensión de polarización, generadores de tensión de substrato, alimentación de seguridad, circuitos de control de alimentación.

- G11C11/4076 G11C 11/00 […] › Circuitos de sincronización (para la gestión de la regeneración G11C 11/406).

- G11C11/4091 G11C 11/00 […] › Amplificadores de lectura o de lectura/refresco, o circuitos de lectura asociados, p. ej. para la precarga, la compensación o el aislamiento de las líneas de bits acoplados.

- G11C11/4094 G11C 11/00 […] › Circuitos de control o de gestión de líneas de bits.

- G11C11/4096 G11C 11/00 […] › Circuitos de control o de gestión de entrada/salida [I/O] de datos, p. ej.circuitos para la lectura o la escritura, circuitos de activación de entrada/salida, conmutadores de líneas de bits.

- G11C5/02 G11C […] › G11C 5/00 Detalles de memorias cubiertos por el grupo G11C 11/00. › Disposición de elementos de almacenamiento, p. ej. bajo la forma de una matriz.

- G11C7/06 G11C […] › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Amplificadores para lectura; Circuitos asociados.

PDF original: ES-2770608_T3.pdf

Patentes similares o relacionadas:

Circuito de detección para RRAM, del 12 de Noviembre de 2019, de Winbond Electronics Corp: Un dispositivo de memoria de acceso aleatorio resistivo que comprende: una matriz de RRAM que comprende: una pluralidad de celdas […]

Dispositivo de memoria para aplicaciones de memoria resistiva, del 30 de Septiembre de 2013, de QUALCOMM INCORPORATED: Un dispositivo de memoria que comprende: una célula de memoria que incluye un elemento de memoria resistivaacoplado a un transistor […]

DISPOSITIVO SENSOR PARA MEMORIA DE MATRIZ PASIVA Y METODO DE LECTURA CORRESPONDIENTE., del 1 de Mayo de 2006, de THIN FILM ELECTRONICS ASA: Un dispositivo sensor para leer datos almacenados en una memoria de matriz pasiva consistente en celdas de memoria en forma de condensadores ferroeléctricos, en el […]

MEMORIA INTEGRADA QUE COMPRENDE UN AMPLIFICADOR DE DETECCION., del 1 de Diciembre de 1995, de PHILIPS ELECTRONICS N.V.: UNA MEMORIA INTEGRADA QUE COMPRENDE UN AMPLIFICADOR DE DETECCION QUE TIENE UN EFECTO DE ECUALIZACION SOBRE LOS VOLTAJES EN LAS ENTRADAS […]

RED DE COMPUTACION ALTAMENTE PARALELA CON VELOCIDAD DE RESPUESTA NORMALIZADA., del 16 de Diciembre de 1993, de AMERICAN TELEPHONE AND TELEGRAPH COMPANY: EN REDES COMPUTACIONALES ALTAMENTE PARALELAS SE OBTIENEN SUPERIORES RENDIMIENTOS ECUALIZANDO LAS CONSTANTES DE TIEMPO DE LOS AMPLIFICADORES. […]

AMPLIFICADOR DE SENTIDO DE DOBLE FASE PARA MEMORIAS DE ACCESO ALEATORIAS., del 1 de Diciembre de 1991, de INTERNATIONAL BUSINESS MACHINES CORPORATION: EN COMBINACION CON UNA MEMORIA ELECTRONICA DEL TIPO QUE TIENE UNA PLURALIDAD DE ACUMULADORES DE MEMORIA (CA, ... CN) CONECTADO ENTRE DOS LINEAS DE BIT (BLT, BLC) QUE TIENEN […]

PERFECCIONAMIENTOS INTRODUCIDOS EN UN PREAMPLIFICADOR PARA DETECCION DE SEÑALES., del 16 de Enero de 1978, de INTERNATIONAL BUSINES MACHINES CORPORATION.: Perfeccionamientos introducidos en un preamplificador para detección de señales que comprende primeros y segundos dispositivos accionables por transferencia de carga, […]

Configuración de memoria de acceso aleatorio magnética (MRAM) con patrón uniforme, del 9 de Julio de 2014, de QUALCOMM INCORPORATED: Una matriz de memoria, que comprende:

un patrón de células binarias adyacentes de tamaño uniforme; y

caracterizado por comprender:

un […]

Configuración de memoria de acceso aleatorio magnética (MRAM) con patrón uniforme, del 9 de Julio de 2014, de QUALCOMM INCORPORATED: Una matriz de memoria, que comprende:

un patrón de células binarias adyacentes de tamaño uniforme; y

caracterizado por comprender:

un […]