Configuración de memoria de acceso aleatorio magnética (MRAM) con patrón uniforme.

Una matriz (302) de memoria, que comprende:

un patrón de células binarias (314) adyacentes de tamaño uniforme;

y

caracterizado por comprender:

un conjunto de circuitos (306) de distribución de señales configurado para ofrecer un área con un volumen total coincidente con un volumen total de un número entero de las células binarias (314) de tamaño uniforme.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2011/055634.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE SAN DIEGO, CA 92121 ESTADOS UNIDOS DE AMERICA.

Inventor/es: KANG,Seung H, KIM,TAE HYUN, LI,XIA, LEE,KANGHO, KIM,JUNG PILL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C5/02 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 5/00 Detalles de memorias cubiertos por el grupo G11C 11/00. › Disposición de elementos de almacenamiento, p. ej. bajo la forma de una matriz.

- H01L27/02 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 27/00 Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00). › incluyendo componentes semiconductores especialmente adaptados para rectificación, amplificación, generación de oscilaciones, conmutación y teniendo al menos una barrera de potencial o una barrera de superficie.; incluyendo elementos de circuito pasivos integrados con al menos una barrera de potencial o una barrera de superficie.

PDF original: ES-2496446_T3.pdf

Fragmento de la descripción:

Configuración de memoria de acceso aleatorio magnética (MRAM) con patrón uniforme Campo técnico

La presente divulgación se refiere, en general, al campo de las memorias de acceso aleatorio magnéticas (MRAM). Más en concreto, la presente divulgación se refiere a unos procedimientos y a unos aparatos para fabricar dispositivos de MRAM.

Antecedentes

A diferencia de las técnicas de chip de memoria de acceso aleatorio (RAM) convencionales, en la RAM magnética (MRAM) los datos no son almacenados como carga eléctrica sino que, en su lugar, son almacenados por polarización magnética de los elementos de almacenamiento. Los elementos de almacenamiento están formados a partir de dos capas ferromagnéticas separadas por una capa de tunelización. Una de las dos capas presenta al menos una polarización magnética de espiga (o capa fija) fijada a una polaridad concreta. La polaridad magnética de la otra capa magnética (o capa libre) es alterada para representar o bien un 1 (por ejemplo, antiparalela a la capa fija) o bien un (por ejemplo, paralela a la capa fija). Un dispositivo de este tipo que incorpora una capa fija, una capa de tunelización y una capa sobre es una unión túnel magnética (MTJ). La resistencia eléctrica de la MTJ depende de la polaridad magnética de la capa libre en comparación con la polaridad magnética de la capa fija. Un dispositivo de memoria, como por ejemplo una MRAM está construida a partir de una matriz de MTJs dirigibles individualmente.

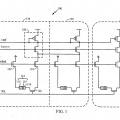

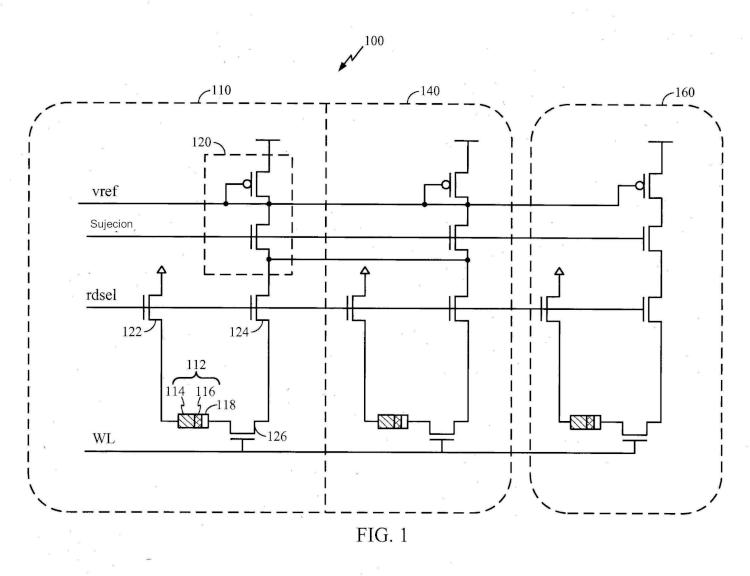

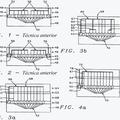

La FIGURA 1 es un circuito esquemático que ¡lustra una porción de una memoria de acceso aleatorio magnética (MRAM) convencional. Una MRMA 1 está dividida en una pluralidad de células binarias 11, 14, 16. Durante la lectura de la célula binaria 16, la resistencia de la célula binaria 16 es comparada con la célula binaria 11 paralela de referencia y con la célula binaria 14 antiparalela de referencia. La resistencia de las células binarias 11, 14, 16 se mide aplicando una tensión primaria y determinando una cantidad de corriente que fluye a través de las células binaras 11, 14, 16. Por ejemplo, en la célula binaria 11, una tensión primaria 12 es aplicada a una unión túnel magnética (MTJ) 112 mediante unos transistores 122, 124 de selección de lectura y un transistor 126 de selección de línea de palabra. La MTJ 112 incluye una capa 114 fija, una capa 116 de tunelización y una capa 118 libre. Cuando la capa 118 libre y la capa 114 fija incorporan magnetizaciones alineadas sustancialmente en paralelo, la resistencia de la MTJ 112 y con ello de la célula binaria 11, es baja. Cuando la capa 118 libre y la capa 114 fija incorporan magnetizaciones alineadas sustancialmente antiparalelas, la resistencia de la MTJ 112 y con ello de la célula binaria 11, es alta.

Las células binarias de una memoria de acceso aleatorio magnética pueden estar dispuestas en una o más matrices que incluyan un patrón de elementos de memoria (por ejemplo, una MTJ en el caso de la MRAM). Con el fin de obtener unas matrices de memoria de alto rendimiento, es fundamental controlar estrictamente el tamaño de los elementos de memoria. Las técnicas de diseño anteriores para implementar matrices de memoria a gran escala han resultado lastradas por el efecto de macrocarga que es inherente al procedimiento de ataque al ácido. Por ejemplo, la tasa de ataque al ácido de los elementos de memoria puede ser mayor en el borde de las matrices en comparación con el centro de las matrices porque la densidad de los patrones es menor en el borde. Como resultado de ello, el tamaño de una MTJ en el borde de un bloque de matriz unitario puede diferir sustancialmente del tamaño de una MTJ cerca del centro del bloque de la matriz. Esto puede provocar la reducción de los rendimientos de producción.

La estructuración de un gran número de células de memoria de tamaño uniforme en una matriz de memoria a gran escala, como por ejemplo una matriz de MRAM puede proporcionar una densidad de patrones uniformes en un área relativamente amplia y puede incrementar los rendimientos obtenidos. El efecto de macrocarga se puede reducir disponiendo unas matrices a gran escala de células de memoria de tamaño uniforme para que un gran número de células de memoria se aloje en áreas de densidad de patrones uniformes después del ataque al ácido. Sin embargo, diversos condicionamientos y problemas de diseño han lastrado el desarrollo de matrices de MRAM a gran escala con una densidad de patrones uniforme.

Los procedimientos anteriormente propuestos para proporcionar matrices de MRAM a gran escala no han proporcionado el emplazamiento de unas líneas o conjuntos de circuitos de distribución de señales dentro de las matrices de memoria. Las líneas de distribución de señales como por ejemplo una banda de línea de palabra (WL) y son necesarias en diseños prácticos, por ejemplo para proporcionar circuitos de señales de baja resistencia a células binarias situadas dentro de una pluralidad de submatrices de células binarias. Se puede utilizar un conjunto de circuitos de intensificación simple de las señales en lugar de la banda metálica. Así mismo, se pueden colocar ligaduras de sustratos periódicamente dentro de las matrices de memoria para proporcionar la conexión masiva de los transistores de acceso dispuestos en las células binarias. En general, la anchura de la banda metálica de la WL y de las ligaduras de los sustratos se reducen al mínimo con las normas de diseño aplicables para ahorrar área.

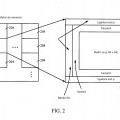

Un procedimiento de provisión del emplazamiento de las líneas de distribución de señales en una matriz de memoria a gran escala se describe con referencia a la FIGURA 2. La matriz 22 de memoria a gran escala se divide en una

pluralidad de submatrices 24 cada una de las cuales incluye un patrón de células binarias de 64 x 64, por ejemplo. Para compensar el efecto de macrocarga en el borde de cada submatriz se puede situar una pluralidad de células binaras ficticias alrededor del perímetro de cada submatriz 24. Estas células binarias ficticias pueden incluir unas células de memoria no funcionales, como por ejemplo unas MTJs flotantes que no estén conectadas al conjunto de circuitos de control de la memoria. Sin embargo, la banda metálica de la línea de palabras y de las ligaduras de sustrato puede ocupar áreas que no incluyan MTJs.

En la FIGURA 2, las líneas o conjunto de circuitos de distribución de señales provocan discontinuidades del patrón que afectan a la densidad global del patrón de la matriz. Debido a que las matrices a gran escala incluyen un gran número de submatñces relativamente pequeñas, este procedimiento genera un gran número de discontinuidades del patrón para acomodar el emplazamiento de las líneas de distribución de señales, como por ejemplo las ligaduras del sustrato o la banda metálica de la WL. Aunque el aumento del número de células ficticias puede mitigar este problema, este sistema no es práctico desde el punto de vista económico porque las múltiples líneas de células ficticias dispuestas en las submatrices incrementarían drásticamente el número total de chips. Por lo tanto, en las matrices de memoria de la práctica, se puede colocar el número mínimo de células de memoria ficticias, y su tamaño puede ser relativamente mayor que el de las células de memoria activas dispuestas dentro de las submatarices 24 para compensar el efecto de carga intenso en los bordes de las submatñces. Sin embargo, este sistema a menudo se traduce en una degradación considerable de la uniformidad del patrón.

La construcción de matrices de memoria a gran escala con una densidad de patrón uniforme a lo largo de ellas ha sido sugerida para reducir el efecto de macrocarga e incrementar los rendimientos de fabricación. Dichas sugerencias no han conseguido dar respuesta a los diversos condicionamientos de diseño y no han suministrado un procedimiento para la colocación de la banda metálica de la WL o de las ligaduras del sustrato, por ejemplo.

El documento US 25/237791 se refiere a un dispositivo de memoria magnética de gran capacidad en el que el campo magnética para la escritura es casi uniforme para todos los elementos de la memoria. Se lleva a cabo reduciendo la deformación del patrón de la capa protectora que se produce en fotolitografía cuando los patrones de fotomáscara están en íntima proximidad unos respecto de otros.

Breve sumario

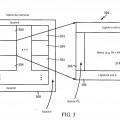

Aspectos de la presente divulgación incluyen una matriz de memoria a gran escala que incluye un patrón uniforme de elementos de memoria. Submatñces dentro de la matriz de memoria a gran escala están separadas por líneas o conjuntos de circuitos de distribución de señales, como por ejemplo la banda de línea de palabra (WL) y de ligaduras de sustrato. En formas de realización... [Seguir leyendo]

Reivindicaciones:

1Una matriz (32) de memoria, que comprende:

un patrón de células binarias (314) adyacentes de tamaño uniforme; y caracterizado por comprender:

un conjunto de circuitos (36) de distribución de señales configurado para ofrecer un área con un volumen total coincidente con un volumen total de un número entero de las células binarias (314) de tamaño uniforme.

2.- La matriz (32) de memoria de la reivindicación 1, en la que las células binarias (314) adyacentes de tamaño uniformen comprenden una pluralidad de células binarias (314) activas situadas fuera del volumen total del conjunto de circuitos (36) de distribución de señales.

3.- La matriz (32) de memoria de la reivindicación 2, que comprende:

un elemento de memoria resistivo configurado en cada una de las células binarias (314) activas.

4.- La matriz (32) de memoria de la reivindicación 2, que comprende:

una unión túnel magnética configurada en cada una de las células binarias (314) activas.

5.- La matriz (32) de memoria de la reivindicación 2, en la que las células binarias (314) adyacentes de tamaño uniforme comprenden una pluralidad de células binarias ficticias (312) dentro del volumen total del conjunto de circuitos (36) de distribución de señales.

6.- La matriz (32) de memoria de la reivindicación 2, en la que el conjunto de circuitos de distribución de señales está acoplado a las células binarias (314) activas.

7.- La matriz (32) de memoria de la reivindicación 1, en la que el conjunto de circuitos (36) de distribución de señales, comprende:

una banda metálica de línea de palabra que se extiende en una primera dimensión del patrón; o al menos una ligadura de sustrato que se extiende en una segunda dimensión del patrón.

8.- La matriz (32) de memoria de la reivindicación 1, que comprende además una pluralidad de células (314) ficticias de borde que se extiende alrededor de un perímetro de la matriz (32) de memoria.

9.- La matriz (32) de memoria de la reivindicación 8, en la que las células ficticias de borde comprenden una pluralidad de células binarias (314) de tamaño uniforme.

1.- La matriz (32) de memoria de la reivindicación 8, en la que las células ficticias de borde comprenden unas células ficticias de mayor tamaño que las células binarias (314) de tamaño uniforme.

11.- La matriz (32) de memoria de la reivindicación 1, integrada en una memoria de acceso aleatorio magnética, MRAM.

12.- La matriz (32) de memoria de la reivindicación 1, integrada en al menos un elemento de entre un teléfono móvil, un descodificador, un reproductor de música, un reproductor de vídeo, una unidad de esparcimiento, un dispositivo de navegación, un ordenador, una unidad de sistemas de comunicaciones personales, PCS, portátil, una unidad de datos portátil y una unidad de datos de emplazamiento fijo.

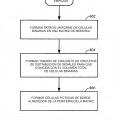

13.- Un procedimiento, que comprende:

la formación de un patrón de células binarias (314) adyacentes de tamaño uniforme en una matriz (32) de memoria, y caracterizado por

la formación de un conjunto de circuitos (36) de distribución de señales en un área que presenta un volumen total del patrón coincidente con un patrón total de un número entero de las células binarias (314) uniforme.

14.- El procedimiento de la reivindicación 13, que comprende:

la integración de la matriz (32) de memoria en al menos un elemento de entre un teléfono móvil, un descodificador, un reproductor de música, un reproductor de vídeo, una unidad de esparcimiento, un dispositivo de navegación, un ordenador, una unidad de sistemas de comunicaciones personales (PCS) portátil, una unidad de datos portátil y una unidad de datos de emplazamiento fijo.

15.- Un aparato, que comprende:

un medio para formar un patrón de células binarias (314) adyacentes de tamaño uniforme en una matriz (32) de memoria; y

caracterizado por comprender

un medio para formar un conjunto de circuitos (36) de distribución de señales en un área que presenta un

volumen total del patrón coincidente con un volumen total de un número entero de las células binarias (314) de tamaño uniforme.

Patentes similares o relacionadas:

Interruptor de alimentación de bloque con protección integrada contra descargas electrostáticas (esd) y polarización adaptativa del cuerpo, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento de fabricación de un circuito, que comprende: formar un interruptor de alimentación que comprenda múltiples etapas conectadas […]

Protección contra descargas electrostáticas para un transistor de efecto de campo sensible a iones, del 4 de Diciembre de 2019, de DNAE GROUP HOLDINGS LIMITED: Dispositivo que comprende una estructura de protección contra descargas electrostáticas , un transistor de efecto de campo sensible a iones […]

Disposición del circuito para la protección de una unidad que debe operarse desde una red de suministro contra sobretensiones, del 6 de Noviembre de 2019, de DEHN SE + Co KG: Disposición del circuito para proteger una unidad que debe operarse desde una red de suministro contra sobretensiones con una entrada que tiene una […]

Bloques de construcción distribuidos de circuitos de fijación r-c en el área central de la pastilla semiconductora, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Un aparato, que comprende:

una pastilla semiconductora que incluye un área central y un anillo de soporte;

circuitos de fijación […]

Bloques de construcción distribuidos de circuitos de fijación r-c en el área central de la pastilla semiconductora, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Un aparato, que comprende:

una pastilla semiconductora que incluye un área central y un anillo de soporte;

circuitos de fijación […]

Esquemas de interconexión posterior a la pasivación en la parte superior de los chips IC, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Una estructura de interconexión posterior a la pasivación, que comprende:

uno o más circuitos internos que comprenden uno o más dispositivos activos formados en […]

Esquemas de interconexión posterior a la pasivación en la parte superior de los chips IC, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Una estructura de interconexión posterior a la pasivación, que comprende:

uno o más circuitos internos que comprenden uno o más dispositivos activos formados en […]

Montaje de circuito para la protección de una unidad que debe operarse desde una red de suministro contra sobretensiones, del 22 de Mayo de 2019, de DEHN + SOHNE GMBH + CO. KG: Montaje de circuito para proteger una unidad que debe operarse desde una red de suministro contra sobretensiones con una entrada que tiene primera y […]

Semiconductor de potencia no uniforme y método de fabricación, del 7 de Mayo de 2019, de IXYS CORPORATION: Un dispositivo semiconductor transistor bipolar de puerta aislada comprendiendo: una pastilla semiconductora con un área activa comprendiendo un conjunto de celdas […]

Desfasador, del 30 de Enero de 2019, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Un desfasador que comprende: una señal de entrada ; una señal de salida ; un circuito de protección contra descarga […]