Chips de memoria y circuitos de evaluación de los mismos.

Un chip de memoria que opera en una pluralidad de modos, que comprende:

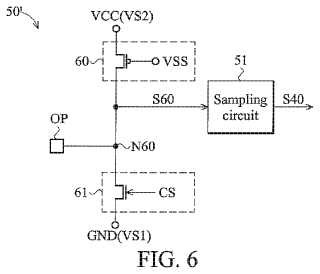

Una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de detección (50') acoplada a la plaqueta de opción en un primer nodo (N60) y controlada por una señal de control (CS) para generar una señal de detección (S60) de acuerdo con el estado en curso de la plaqueta de opción; En donde la unidad de detección comprende:

Un elemento (60) de alto nivel débil acoplado entre una fuente de voltaje de alto nivel (Vd.) y el primer nodo (N60); y Un elemento de conmutación (61) acoplado entre el primer nodo (N60) y un voltaje de tierra (GND), y activado por la señal de control activada (CS);

en donde el elemento de conmutación (61) momentáneamente conduce con un potencial de la plaqueta de opción (OP) hacia un nivel de la fuente de voltaje de tierra (GND) cuando la señal de control CS está activada, y en donde la señal de detección (S61) está generada en el primer nodo (N60); y

una unidad de muestreo (51) para recibir la señal de detección (S60) y para muestrear la señal de detección (S60) dos veces después de que la señal de control (CS) haya sido desactivada para generar una señal de evaluación (S40);

En donde la señal de evaluación (S40) indica cual es el modo en que está operando el chip de memoria.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E09180423.

Solicitante: Winbond Electronics Corp.

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: No. 8, Keya 1st Road Central Taiwan Science Park Taichung City, Taiwan TAIWAN.

Inventor/es: Tu,Ying-Te.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C5/00 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › Detalles de memorias cubiertos por el grupo G11C 11/00.

PDF original: ES-2384136_T3.pdf

Fragmento de la descripción:

Chips de memoria y circuitos de evaluación de los mismos.

ANTECEDENTES DE LA INVENCIÓN

Campo de la invención La invención está relacionada con un chip de memoria, y más en particular con un circuito de resolución para evaluar que un chip de memoria está operando como una plaqueta de memoria única o una plaqueta de chips de memoria apilados de acuerdo con los estados de una plaqueta de opción del chip de memoria.

Descripción de la técnica relacionada La figura 1 es una vista esquemática que muestra un chip de memoria de 256 Mb. Con referencia a la figura 1, el chip de memoria 1 comprende 23 plaquetas de direcciones A0-A22, una plaqueta de opción OP, y una plaqueta artificial NC. Cuando el chip de memoria 1 opera como una sola plaqueta de memoria, tanto la plaqueta de opción OP como la plaqueta artificial NC se encuentran en estado flotante. Un circuito de extracción débil de niveles alto/bajo en el interior del chip de memoria 1 extrae gradualmente un nodo interior, el cual está conectado con la plaqueta de opción OP a un nivel de voltaje alto/bajo. En la siguiente descripción, un circuito de nivel alto de extracción débil y una operación de nivel alto débil par la plaqueta de opción OP se proporcionan como un ejemplo.

En algunas aplicaciones, al menos dos chips de memoria 1, tal como se muestra en la figura 1, pueden apilarse para formar un dispositivo de memoria. Tal como se muestra en la figura 2, el dispositivo de memoria 2 de 512 Mb tiene dos chips de memoria apilados 20 y 21 de 256 Mb, que se proporciona como un ejemplo. Cada uno de los chips de memoria apilados 20 y 21 tienen la misma estructura que el chip de memoria de la figura 1, y la plaqueta NC artificial del chip de memoria 1 sirve como la plaqueta de direcciones A23 de 24 direcciones para direccionar los dos chips de memoria 20 y 21. El chip de memoria superior 20 está apilado sobre el chip 21 de memoria inferior, y un espaciador 23 se encuentra en la posición intermedia. La figura 3 es una vista esquemática que muestra la conexión entre las plaquetas de direcciones A0-A23 de los chips de memoria 20 y 21. Con el fin de mostrar en forma clara la conexión, los chips de memoria 20 y 21 se muestran juntos lado con lado, y no obstante en la práctica, el chip de memoria superior 20 está apilado sobre el chip 21 de memoria inferior, tal como se muestra en la figura 2. Con referencia a la figura 3, las plaquetas de direcciones A0-A23 del chip de memoria 20 están conectadas a las plaquetas de direcciones A0-A23 del chip de memoria 21 en las plaquetas de direcciones A0'-A23', respectivamente. Los chips de memoria 20 y 21 reciben una señal de direccionamiento a través de las plaquetas de direcciones A0'-A23'.

En la figura 3, la plaqueta de opción OP del chip 20 de memoria superior está conectada a una fuente de voltaje alto VDD, y un nodo interno está conectado a la plaqueta de opción OP que por tanto está un nivel alto. La plaqueta OP de opción del chip 21 de memoria inferior está conectado a una fuente de bajo voltaje VSS, y un nodo interno está conectado a una plaqueta de opción OP que por tanto está a un nivel bajo de voltaje. Así pues, cuando la plaqueta de direcciones A23' recibe una señal lógica alta (H) el chip de memoria 20 superior se activa y el chip 21 de memoria inferior se inactiva. Por el contrario, cuando la plaqueta A23' de direcciones recibe una señal de nivel bajo (L) , el chip 21 de memoria inferior se activa, y el chip 20 de memoria superior se inactiva.

Así pues, un chip de memoria, tal como los chips de memoria 20 y 21 pueden operar en tres modos, de acuerdo con el estado de su plaqueta de opción. En el primer modo, el chip de memoria opera como una matriz de memoria única cuando la plaqueta de opción OP de la misma está en flotación; en el segundo modo, el chip de memoria opera como una matriz de memoria superior entre dos matrices de memoria apiladas cuando la plaqueta de opción OP está conectada a una fuente de voltaje alto VDD; y en el tercer modo, el chip de memoria opera como una matriz de memoria inferior entre dos matrices de memoria apiladas cuando la plaqueta de opción OP está conectada a la fuente de voltaje VSS. En los tres modos, el nodo interno conectado a la plaqueta de opción OP del chip de memoria pasa a nivel alto en forma débil de la memoria, a nivel alto fuertemente y a nivel bajo fuertemente en la forma respectiva. De acuerdo con la anterior descripción, cuando un chip de memoria opera en el primer modo y en el segundo modo, un nodo interno conectado a una plaqueta de opción OP del chip de memoria pasa a nivel alto. Así pues, cuando el nodo interno está a alto nivel, el chip de memoria en sí no puede determinar que está operando como una matriz de memoria única (primer modo) o como una matriz de memoria superior entre dos matrices de memoria apiladas (segundo modo) . Esta situación puede tener lugar para un chip de memoria que se quiera que sea una matriz de memoria superior entre dos matrices de memoria apiladas, tal como el chip de memoria superior 20 en la figura 2.

Supóngase que un circuito de nivel bajo débil y una operación baja de nivel débil se aplican para hacer que flote la plaqueta de opción OP. De acuerdo con la anterior descripción, cuando un chip de memoria opera en el primer modo y el tercer modo, un nodo interno conectado a una plaqueta de opción OP del chip de memoria pasa a nivel bajo. Así pues, cuando el nodo interno está a un nivel bajo de voltaje, el chip de memoria en si mismo no puede determinar que esté operando como una única matriz de memoria (primer modo) o como una matriz de memoria única entre dos matrices de memoria apiladas (tercer modo) . Esta situación puede tener lugar en un chip de memoria que se desee que sea un chip de memoria entre dos matrices apiladas, tal como el chip de memoria 21 inferior en la figura 2.

Así pues, es deseable proporcionar un circuito de resolución para enjuiciar que un chip de memoria está operando como una sola matriz de memoria o como una matriz entre las matrices de memoria apiladas.

Los chips tal como están expuestos en los documentos US 6225836 y US 4987325 tienen unos circuitos de direccionamiento del modo que pueden discriminar entre los tres modos.

BREVE RESUMEN DE LA INVENCIÓN

Se proporciona una realización a modo de ejemplo de un chip de memoria. El chip de memoria opera en una pluralidad de modos. El chip de memoria comprende una plaqueta de opción y una unidad de detección. La plaqueta de opción tiene una pluralidad de estados. La unidad de detección está acoplada a la plaqueta de opción en un primer modo, y está controlada por una señal de control para generar una señal de detección de acuerdo con el estado en curso de la plaqueta de opción. La unidad de detección comprende un elemento de nivel alto de extracción débil acoplado entre una fuente de voltaje alto y el primer nodo. Comprende además un elemento de conmutación el cual está acoplado entre el primer nodo y una fuente de voltaje de tierra, y se activa por medio de la señal de control activada. Además el elemento de conmutación activa momentáneamente un potencial del nodo de opción a un nivel de la fuente de voltaje de tierra cuando la señal de control se activa, y la señal de activación se genera en el primer nodo. El chip de memoria además comprende una unidad de muestreo para recibir la señal de detección y el muestreo de la señal de detección dos veces después de que la señal de control se haya desactivado para generar una señal de evaluación, en donde la señal de resolución indicará cual es el modo en que esté operando el chip de memoria.

En las siguientes realizaciones se proporciona una descripción detallada con referencia a los dibujos adjuntos.

BREVE DESCRIPCIÓN DE LOS DIBUJOS

La invención puede comprenderse mejor en su totalidad mediante la lectura de la siguiente descripción detallada y con sus ejemplos, con referencia a los dibujos adjuntos, en donde:

La figura 1 es una vista esquemática que muestra un chip de memoria;

La figura 2 muestra un dispositivo de memoria que tiene dos chips de memoria apilados;

La figura 3 es una vista esquemática que muestra la conexión entre las plaquetas de direccionamiento A0-A23 de los chips de memoria 20 y 21 en la figura 2:

La figura 4 muestra una realización a modo de ejemplo de un chip de memoria;

La figura 5 muestra una realización a modo de ejemplo del circuito de resolución 40 en la figura 4;

La... [Seguir leyendo]

Reivindicaciones:

1. Un chip de memoria que opera en una pluralidad de modos, que comprende: Una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de detección (50') acoplada a la plaqueta de opción en un primer nodo (N60) y controlada por una señal de control (CS) para generar una señal de detección (S60) de acuerdo con el estado en curso de la plaqueta de opción; En donde la unidad de detección comprende:

Un elemento (60) de alto nivel débil acoplado entre una fuente de voltaje de alto nivel (Vd.) y el primer nodo (N60) ; y Un elemento de conmutación (61) acoplado entre el primer nodo (N60) y un voltaje de tierra (GND) , y activado por la señal de control activada (CS) ;

en donde el elemento de conmutación (61) momentáneamente conduce con un potencial de la plaqueta de opción (OP) hacia un nivel de la fuente de voltaje de tierra (GND) cuando la señal de control CS está activada, y en donde la señal de detección (S61) está generada en el primer nodo (N60) ; y una unidad de muestreo (51) para recibir la señal de detección (S60) y para muestrear la señal de detección (S60) dos veces después de que la señal de control (CS) haya sido desactivada para generar una señal de evaluación (S40) ;

En donde la señal de evaluación (S40) indica cual es el modo en que está operando el chip de memoria.

2. El chip de memoria tal como se reivindica en la reivindicación 1 que además comprende un circuito de control para recibir la señal de evaluación y para controlar el chip de memoria de acuerdo con la señal de evaluación.

3. El chip de memoria tal como se expone en la reivindicación 1, en donde el elemento de alto nivel débil está implementado por un transistor PMOS que siempre está activado en conducción.

4. Un chip de memoria operando en una pluralidad de modos que comprende:

Una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de detección (50') acoplada a la plaqueta de opción en un primer nodo (N60) y controlada por una señal de control (CS) para generar una señal de detección (S60) de acuerdo con el estado en curso de la plaqueta de opción (OP) ; en donde la unidad de detección comprende:

Un elemento (60) de bajo nivel débil acoplado entre una fuente de voltaje de tierra (GND) y el prime nodo; y Un elemento de conmutación (61) acoplado entre el primer nodo y una fuente de voltaje de alto nivel (VCC) y activado por la señal de control activada (CS) ;

en donde el elemento de conmutación (61) momentáneamente activa un potencial de la plaqueta de opción (OP) hacia un nivel de la fuente de voltaje de alto nivel (Vd.) cuando la señal de control (CS) se activa, y en donde la señal de detección (S60) se genera en el primer nodo;

una unidad de muestreo (51) para recibir la señal de detección (S60) y poder muestrear la señal de detección (S60) dos veces después de que la señal de control (CS) haya sido desactivada para generar una señal de evaluación; en donde la señal de evaluación indica cual es el modo en que está operando el chip de memoria.

5. El chip de memoria según la reivindicación 4 que además comprende un circuito de control para recibir la señal de evaluación y para controlar el chip de memoria de acuerdo con la señal de evaluación.

6. El chip de memoria según la reivindicación 4, en donde el elemento de bajo nivel débil está implementado por un transistor NMOS, el cual está siempre activado en conducción.

7. Un chip de memoria que opera en una pluralidad de modos, que comprende: una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de detección (50") acoplada a la plaqueta de opción (OP) en un primer nodo (N90) y controlada por una

señal de control (CS) para generar una primera señal de detección (S90) y una segunda señal de detección (S91) de acuerdo con el estado en curso de la plaqueta de opción (OP) ; en donde la unidad de detección (50") comprende: un primer elemento de conmutación (90) acoplado entre el primer nodo (N90) y una fuente de voltaje de tierra (GND) y activado por la señal de control activada (CS) ;

un segundo elemento de conmutación (91) acoplado entre el primer nodo (N90) y un segundo nodo (N91) , en donde el segundo elemento de conmutación (91) está activado en un primer periodo y desactivado en un segundo periodo siguiente al primer periodo; y un elemento de alto nivel débil (92) acoplado entre una fuente de voltaje de alto nivel (VCC) y el segundo nodo (N91) ;

en donde el primer elemento de conmutación (90) momentáneamente activa un potencial de la plaqueta de opción (OP) a un nivel de la fuente de voltaje de tierra (GND) cuando la señal de control (CS) se activa durante el segundo periodo; y en donde la primera señal de detección (S90) se genera en el primer nodo (N90) , y en donde la segunda señal de detección (S91) se genera en el segundo nodo (N91) ; y una unidad de muestreo (51) para recibir la primera (S90) y la segunda (S91) señales de detección y muestrear la primera (S90) y la segunda (S91) señales de detección en instantes distintos (T3/T4) después de que la señal de control (CS) haya sido desactivada para generar una señal de evaluación;

cuando la señal de evaluación indique cual es el modo en que opera el chip de memoria.

8. El chip de memoria según la reivindicación 7, en donde el elemento de conducción débil de alto nivel está implementado por un transistor PMOS que siempre está activado en conducción.

9. El chip de memoria según la reivindicación 7, en donde la señal de control está activada en el segundo periodo, y después de activar la señal de control, en donde la unidad de muestreo muestrea la primera señal de detección para obtener un primer valor lógico, y para muestrear la segunda señal de detección para obtener un segundo valor lógico, y el primer y segundo valores lógicos a partir de la señal de evaluación.

10. Un chip de memoria que opera en una pluralidad de modos, que comprende:

una plaqueta de opción (OP) que tiene una pluralidad de estados:

y una unidad de detección (50") acoplada a la plaqueta de opción (OP) en un primer nodo (N90) y controlada por una señal de control (CS) para generar una primera señal de detección (S90) y una segunda señal de detección (S91) de acuerdo con el estado en curso de la plaqueta de opción (OP) ; en donde la unidad de detección comprende:

un primer elemento de conmutación (90) acoplado entre el primer nodo (N90) y una fuente de voltaje de alto nivel (VCC) y activado por la señal de control activada (CS) ;

un segundo elemento de conmutación (91) acoplado entre el primer nodo (N90) y un segundo nodo (N91) , en donde el segundo elemento de conmutación (91) está activado en conducción en un primer periodo y desactivado en un segundo periodo siguiente al primer periodo; y un elemento (92) de nivel alto de conducción débil acoplado entre una fuente de voltaje de tierra (GND) y el segundo nodo (N91) ;

en donde el primer elemento de conmutación (90) conduce momentáneamente un potencial de la plaqueta de opción (OP) a un nivel de la fuente (Vcc) de voltaje de alto nivel, cuando la señal de control (CS) se active durante el segundo periodo; y en donde la primera señal de detección (S90) se genera en el primer nodo (N90) ; y la segunda señal de detección (S91) que se genera en el segundo nodo (N91) ; y una unidad de muestreo (51) para recibir la primera (S90) y segunda (S91) señales de detección y el muestreo de la primera (S90) y segunda (S91) señales de detección en distintos instantes (T3/T4) después de que la señal de control (CS) haya sido desactivada para generar una señal de evaluación;

en donde la señal de evaluación indique cual es el modo en que está operando el chip.

11. El chip de memoria según la reivindicación 10, en donde el elemento de bajo nivel débil está implementado por un transistor NMOS que siempre está activado en conducción.

12. El chip de memoria según la reivindicación 10, en donde la señal de control está activada en el segundo periodo, y después de activar la señal de control, en donde la unidad de muestreo muestrea la primera señal de detección para obtener un primer valor lógico y muestreando la segunda señal de detección para obtener un segundo valor lógico, y el primero y segundo valores lógicos que forman la señal de evaluación.

Patentes similares o relacionadas:

Dispositivo de memoria que corrige el efecto de colisiones de partículas de alta energía, del 28 de Agosto de 2019, de THALES: Dispositivo de memoria que corrige automáticamente el efecto de colisiones de partículas de alta energía, que comprende una célula (CM) de memoria; […]

Sistema de memoria caché y método para generar objetos que no están almacenados en la memoria caché a partir de componentes de objetos en la memoria caché y almacenados, del 26 de Octubre de 2016, de AWARE, INC.: En un sistema de procesamiento de datos que tiene una memoria caché , un método para generar una imagen no almacenada en la memoria caché que comprende: […]

Difusión general selectiva de datos en dispositivos conectados en serie, del 9 de Abril de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Método para seleccionar un subconjunto de dispositivos de una pluralidad de dispositivos conectados en serie a un controlador de memorias con el fin […]

Lectura de registro para memoria volátil, del 3 de Octubre de 2012, de QUALCOMM INCORPORATED: Un procedimiento de lectura de datos de un módulo SDRAM (RAM, Memoria de Acceso Dinámico Síncrona), no estando almacenados tales datos en una matriz DRAM […]

Sistema y procedimiento para el control de potencia en sistemas de comunicación inalámbrica, del 24 de Abril de 2012, de QUALCOMM INCORPORATED: Un metodo para variar un nivel de potencia de una seral proporcionada a un amplificador de potencia de un transmisor de un dispositivo de comunicacion inalambrica, […]

Detección y correccion de errores para una memoria cuyos estados de bit tienen una resistencia de error diferente, del 28 de Marzo de 2012, de ASTRIUM SAS: Una memoria que comprende:

- celdas de memoria , únicas o múltiples, de comportamiento disimétrico,

- un comportamiento disimétrico resultante de la sensibilidad […]

Detección y correccion de errores para una memoria cuyos estados de bit tienen una resistencia de error diferente, del 28 de Marzo de 2012, de ASTRIUM SAS: Una memoria que comprende:

- celdas de memoria , únicas o múltiples, de comportamiento disimétrico,

- un comportamiento disimétrico resultante de la sensibilidad […]

MATRIZ PASIVA NO VOLATIL Y METODO PARA LA LECTURA DE LA MISMA., del 16 de Agosto de 2005, de THIN FILM ELECTRONICS ASA: Dispositivo que constituye una memoria de matriz pasiva no volátil y comprende un material de memoria dieléctrico eléctricamente polarizable […]

ESCRITURA EN TIEMPO REAL ASEGURADA PARA MEMORIA NO VOLATIL, del 16 de Marzo de 2009, de GEMPLUS: Procedimiento para escribir datos iniciales contenidos en una petición de escritura (RE1) transmitida por un medio de tratamiento de datos (PR, AP) a […]

ESCRITURA EN TIEMPO REAL ASEGURADA PARA MEMORIA NO VOLATIL, del 16 de Marzo de 2009, de GEMPLUS: Procedimiento para escribir datos iniciales contenidos en una petición de escritura (RE1) transmitida por un medio de tratamiento de datos (PR, AP) a […]