MATRIZ PASIVA NO VOLATIL Y METODO PARA LA LECTURA DE LA MISMA.

Dispositivo (10) que constituye una memoria de matriz pasiva no volátil y comprende un material de memoria dieléctrico eléctricamente polarizable (12) que presenta histéresis,

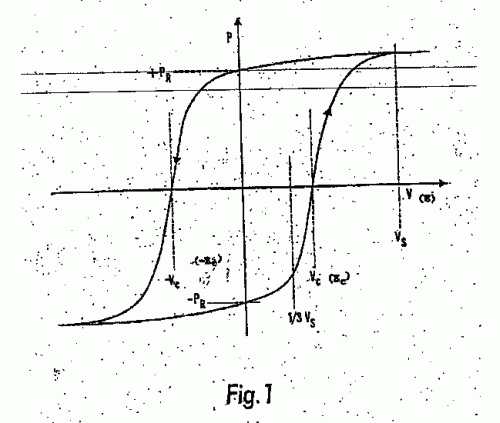

y en particular un material ferroeléctrico, estando dicho material de memoria (12) previsto de forma tal que está intercalado en una capa entre un primer conjunto y un segundo conjunto (14; 15) de respectivos electrodos de direccionamiento paralelos, constituyendo los electrodos del primer conjunto (14) líneas de palabra (WL1, ...m) del dispositivo que constituye una memoria y estando dichos electrodos del primer conjunto previstos de forma tal que guardan una relación prácticamente de ortogonalidad con los electrodos del segundo conjunto (15), constituyendo éstos últimos las líneas de bit (BL1, ...n) del dispositivo que constituye una memoria, estando una celda de memoria (13) con una estructura del tipo de la de un condensador definida en el material de memoria (12) en los cruces entre las líneas de palabra y las líneas de bit, constituyendo las celdas de memoria (13) del dispositivo que constituye una memoria los elementos de una matriz pasiva (11), pudiendo ser cada celda de memoria (13) direccionada selectivamente para una operación de grabación/lectura a través de una línea de palabra (WL) y de una línea de bit (BL), teniendo lugar una operación de grabación en una celda de memoria (13) a base de establecer un deseado estado de polarización en la celda por medio de un voltaje que es aplicado a la celda a través de la respectiva línea de palabra (WL) y de la respectiva línea de bit (BL) que definen la celda, estableciendo dicho voltaje aplicado un determinado estado de polarización en la celda de memoria (13) o siendo dicho voltaje aplicado capaz de conmutar entre los estados de polarización de la misma, y teniendo lugar una operación de lectura a base de aplicar un voltaje mayor que el voltaje coercitivo (Vc) a la celda de memoria (13) y de detectar al menos un parámetro eléctrico de una corriente de salida en las líneas de bit (BL).

Tipo: Resumen de patente/invención.

Solicitante: THIN FILM ELECTRONICS ASA.

Nacionalidad solicitante: Noruega.

Dirección: P.O. BOX 1872 VIKA,0124 OSLO.

Inventor/es: CARLSSON, JOHAN, THOMPSON, MICHAEL, WOMACK, RICHARD, GUSTAFSSON, GIRAN.

Fecha de Publicación: .

Fecha Solicitud PCT: 24 de Agosto de 2001.

Fecha Concesión Europea: 9 de Marzo de 2005.

Clasificación Internacional de Patentes:

- G11C5/00 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › Detalles de memorias cubiertos por el grupo G11C 11/00.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Oficina Europea de Patentes, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania, Armenia, Azerbayán, Bielorusia, Ghana, Gambia, Kenya, Kirguistán, Kazajstán, Lesotho, República del Moldova, Malawi, Mozambique, Federación de Rusia, Sudán, Sierra Leona, Tayikistán, Turkmenistán, República Unida de Tanzania, Uganda, Zimbabwe, Burkina Faso, Benin, República Centroafricana, Congo, Costa de Marfil, Camerún, Gabón, Guinea, Malí, Mauritania, Niger, Senegal, Chad, Togo, Organización Regional Africana de la Propiedad Industrial, Swazilandia, Guinea-Bissau, Guinea Ecuatorial, Organización Africana de la Propiedad Intelectual, Organización Eurasiática de Patentes.

Patentes similares o relacionadas:

Dispositivo de memoria que corrige el efecto de colisiones de partículas de alta energía, del 28 de Agosto de 2019, de THALES: Dispositivo de memoria que corrige automáticamente el efecto de colisiones de partículas de alta energía, que comprende una célula (CM) de memoria; […]

Sistema de memoria caché y método para generar objetos que no están almacenados en la memoria caché a partir de componentes de objetos en la memoria caché y almacenados, del 26 de Octubre de 2016, de AWARE, INC.: En un sistema de procesamiento de datos que tiene una memoria caché , un método para generar una imagen no almacenada en la memoria caché que comprende: […]

Difusión general selectiva de datos en dispositivos conectados en serie, del 9 de Abril de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Método para seleccionar un subconjunto de dispositivos de una pluralidad de dispositivos conectados en serie a un controlador de memorias con el fin […]

Lectura de registro para memoria volátil, del 3 de Octubre de 2012, de QUALCOMM INCORPORATED: Un procedimiento de lectura de datos de un módulo SDRAM (RAM, Memoria de Acceso Dinámico Síncrona), no estando almacenados tales datos en una matriz DRAM […]

Sistema y procedimiento para el control de potencia en sistemas de comunicación inalámbrica, del 24 de Abril de 2012, de QUALCOMM INCORPORATED: Un metodo para variar un nivel de potencia de una seral proporcionada a un amplificador de potencia de un transmisor de un dispositivo de comunicacion inalambrica, […]

Detección y correccion de errores para una memoria cuyos estados de bit tienen una resistencia de error diferente, del 28 de Marzo de 2012, de ASTRIUM SAS: Una memoria que comprende:

- celdas de memoria , únicas o múltiples, de comportamiento disimétrico,

- un comportamiento disimétrico resultante de la sensibilidad […]

Detección y correccion de errores para una memoria cuyos estados de bit tienen una resistencia de error diferente, del 28 de Marzo de 2012, de ASTRIUM SAS: Una memoria que comprende:

- celdas de memoria , únicas o múltiples, de comportamiento disimétrico,

- un comportamiento disimétrico resultante de la sensibilidad […]

Chips de memoria y circuitos de evaluación de los mismos, del 14 de Marzo de 2012, de Winbond Electronics Corp: Un chip de memoria que opera en una pluralidad de modos, que comprende: Una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de […]

Chips de memoria y circuitos de evaluación de los mismos, del 14 de Marzo de 2012, de Winbond Electronics Corp: Un chip de memoria que opera en una pluralidad de modos, que comprende: Una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de […]

ESCRITURA EN TIEMPO REAL ASEGURADA PARA MEMORIA NO VOLATIL, del 16 de Marzo de 2009, de GEMPLUS: Procedimiento para escribir datos iniciales contenidos en una petición de escritura (RE1) transmitida por un medio de tratamiento de datos (PR, AP) a […]

ESCRITURA EN TIEMPO REAL ASEGURADA PARA MEMORIA NO VOLATIL, del 16 de Marzo de 2009, de GEMPLUS: Procedimiento para escribir datos iniciales contenidos en una petición de escritura (RE1) transmitida por un medio de tratamiento de datos (PR, AP) a […]