LECTURA NO DESTRUCTIVA.

Un procedimiento para determinar un estado lógico de células (1) de memoria seleccionadas,

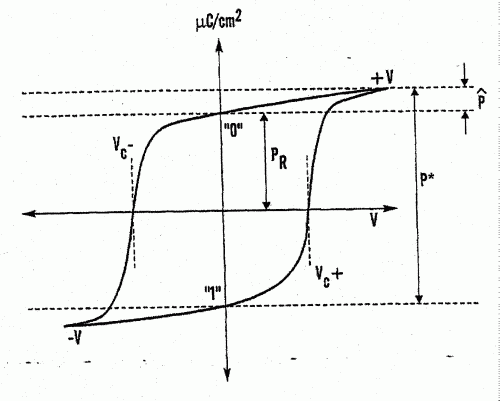

proporcionadas en un dispositivo pasivo de almacenamiento de datos, matricialmente direccionable, que contiene líneas de palabra y de bit (LP; LB), en el cual a un estado lógico específico se asigna un único valor lógico, según un protocolo predeterminado, en donde dichas células (1) almacenan datos en forma de un estado de polarización eléctrica en estructuras similares a condensadores, que comprenden un material polarizable, en particular, un material ferroeléctrico o 'electret', capaz de manifestar histéresis, en donde dicho material polarizable es capaz de mantener una polarización eléctrica no volátil en ausencia de un voltaje impreso externamente a través de dichas estructuras similares a condensadores, en donde tiene lugar una selección de células de memoria al activar la línea de palabra (LP) o la línea de bit (LB), o ambas, que se cruzan en una célula (1) de memoria en cuestión, en donde la activación de una línea de palabra (LP) o de una línea de bit (LB) se efectúa por medio de diferencias de potencial entre las mismas, aplicadas externamente, sometiendo así a dichas células seleccionadas (1) a un voltaje de sondeo de señal reducida, que surge de la diferencia de potencial aplicada, por lo cual se genera una corriente de respuesta desde dichas células, en donde dicho voltaje de sondeo de señal reducida depende del tiempo, en forma arbitrariamente seleccionable, y tiene amplitudes y / o duraciones de voltaje menores que aquellas requeridas para causar un cambio significativo permanente en los estados de polarización de dichas células.

Tipo: Resumen de patente/invención.

Solicitante: THIN FILM ELECTRONICS ASA.

Nacionalidad solicitante: Noruega.

Dirección: P.O. BOX 1872 VIKA,0124 OSLO.

Inventor/es: NORDAL, PER-ERIK, GUDESEN, HANS, GUDE, LEISTAD, GEIRR, I..

Fecha de Publicación: .

Fecha Solicitud PCT: 15 de Febrero de 2002.

Clasificación Internacional de Patentes:

- G11C11/22 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 11/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento eléctricos o magnéticos particulares; Elementos de almacenamiento correspondientes (G11C 14/00 - G11C 21/00 tienen prioridad). › que utilizan elementos ferroeléctricos.

- G11C7/12 G11C […] › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Circuitos de control de líneas de bits, p. ej. circuitos de excitación, de potencia, de arrastre hacía arriba (pull-up), de empuje hacía abajo (pull-down), circuitos de precarga, circuitos de igualación, para líneas de bits.

- G11C8/08 G11C […] › G11C 8/00 Disposiciones para seleccionar una dirección en una memoria digital (circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Circuitos de control de líneas de palabras, p. ej. circuitos de excitación, de potencia, de arrastre hacía arriba (pull-up), de empuje hacía abajo (pull-down), circuitos de precarga, circuitos de igualación, para líneas de palabras.

Clasificación PCT:

- G11C11/22 G11C 11/00 […] › que utilizan elementos ferroeléctricos.

- G11C7/12 G11C 7/00 […] › Circuitos de control de líneas de bits, p. ej. circuitos de excitación, de potencia, de arrastre hacía arriba (pull-up), de empuje hacía abajo (pull-down), circuitos de precarga, circuitos de igualación, para líneas de bits.

- G11C8/08 G11C 8/00 […] › Circuitos de control de líneas de palabras, p. ej. circuitos de excitación, de potencia, de arrastre hacía arriba (pull-up), de empuje hacía abajo (pull-down), circuitos de precarga, circuitos de igualación, para líneas de palabras.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Oficina Europea de Patentes, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Patentes similares o relacionadas:

Circuitos de líneas de bits globales de Memoria Estática de Acceso Aleatorio (SRAM) para reducir los fallos de energía durante los accesos de lectura de memoria, y procedimientos y sistemas relacionados, del 17 de Abril de 2019, de QUALCOMM INCORPORATED: Un circuito de línea de bits global de memoria estática de acceso aleatorio, SRAM, para una pluralidad de células de bits de SRAM, que […]

Mejora de estabilidad de lectura de memoria usando precarga selectiva de secciones de línea de bits, del 8 de Octubre de 2018, de QUALCOMM INCORPORATED: Un dispositivo de memoria que comprende: medios para precargar una primera sección de una primera línea de bits de una primera célula de bits […]

Procedimiento y aparato para reducir la corriente de fugas en formaciones de memoria, del 28 de Septiembre de 2016, de QUALCOMM INCORPORATED: Un circuito integrado que comprende: una formación de memoria que comprende una pluralidad de filas y una pluralidad de columnas de celdas de memoria ; […]

Control de impedancia dinámica para memorias intermedias de entrada/salida, del 25 de Junio de 2014, de Conversant Intellectual Property Management Inc: Circuito de excitación y terminación, que comprende: una red de pull-up de impedancia variable que tiene una primera pluralidad de 5 transistores ; una red de […]

Arquitectura de núcleos en serie de memoria no volátil, del 14 de Mayo de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Tampón de página de banco de memoria que comprende matriz de memoria acoplada a bitlines (BL) y wordlines (WL), caracterizado: por primeras […]

Dispositivo de memoria para aplicaciones de memoria resistiva, del 30 de Septiembre de 2013, de QUALCOMM INCORPORATED: Un dispositivo de memoria que comprende: una célula de memoria que incluye un elemento de memoria resistivaacoplado a un transistor […]

Sistema de memoria de múltiples flujos de instrucciones, del 6 de Mayo de 2020, de QUALCOMM INCORPORATED: Un dispositivo de memoria que comprende: un decodificador ; una pluralidad de células de memoria , en el que cada una de las células […]

Sistema y procedimiento para reducir el esfuerzo de tensión de programación en dispositivos de celdas de memoria, del 8 de Enero de 2020, de QUALCOMM INCORPORATED: Una memoria OTP programable una vez , que comprende: una primera línea de palabra global (GWL1); un primer conjunto de líneas […]