Control de impedancia dinámica para memorias intermedias de entrada/salida.

Circuito de excitación y terminación, que comprende:

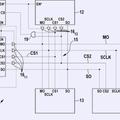

una red de pull-up de impedancia variable (40) que tiene una primera pluralidad de 5 transistores (43);

una red de pull-down de impedancia variable (42) que tiene una segunda pluralidad de transistores (45); estando configurada cada una de entre la red de pull-up (40) y la red de pull-down (42) para presentar una impedancia deseada variando el número de transistores activados;

una primera pluralidad de bits de control de un bus de control de impedancia para establecer una configuración de terminación de la red de pull-up (40);

una segunda pluralidad de bits de control del bus de control de impedancia para establecer una configuración de terminación de la red de pull-down (42);

una tercera pluralidad de bits de control del bus de control de impedancia para establecer una configuración de excitación de la red de pull-up (40); y

una cuarta pluralidad de bits de control del bus de control de impedancia para establecer una configuración de excitación de la red de pull-down (42);

en el que las primera a cuarta pluralidades de bits de control son independientes entre sí;

presentando el circuito un modo de funcionamiento de terminación en el cual la red de pull-up de impedancia variable (40) está configurada para presentar una impedancia de terminación de red de pull-up sobre la base de la primera pluralidad de bits de control, y la red de pull-down de impedancia variable (42) está configurada para presentar una impedancia de terminación de red de pull-down sobre la base de la segunda pluralidad de bits de control, funcionando la red de pull-up (40) y la red de pull-down (42) en combinación como una terminación dividida;

presentando el circuito un modo de funcionamiento de excitación, en el cual:

para excitar una salida alta, la red de pull-up (40) está configurada para generar una impedancia específica cuando está activada sobre la base de la tercera pluralidad de bits de control; y

para excitar una salida baja, la red de pull-down (42) está configurada para generar una impedancia específica cuando está activada sobre la base de la cuarta pluralidad de bits de control.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/CA2008/001069.

Solicitante: Conversant Intellectual Property Management Inc.

Inventor/es: MILLAR,BRUCE.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C11/407 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 11/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento eléctricos o magnéticos particulares; Elementos de almacenamiento correspondientes (G11C 14/00 - G11C 21/00 tienen prioridad). › para celdas de memoria del tipo efecto de campo.

- G11C7/10 G11C […] › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

- G11C7/12 G11C 7/00 […] › Circuitos de control de líneas de bits, p. ej. circuitos de excitación, de potencia, de arrastre hacía arriba (pull-up), de empuje hacía abajo (pull-down), circuitos de precarga, circuitos de igualación, para líneas de bits.

- H03H7/38 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03H REDES DE IMPEDANCIA, p. ej. CIRCUITOS RESONANTES; RESONADORES (medidas, ensayos G01R; disposiciones para producir una reverberación sonora o un eco G10K 15/08; redes de impedancia o resonadores que se componen de impedancias distribuidas, p. ej. del tipo guía de ondas, H01P; control de la amplificación, p. ej. control del ancho de banda de los amplificadores, H03G; sintonización de circuitos resonantes, p. ej. sintonización de circuitos resonantes acoplados, H03J; redes para modificar las características de frecuencia de sistemas de comunicación H04B). › H03H 7/00 Redes de varios accesos que tienen como componentes únicamente elementos eléctricos pasivos (circuitos de entrada de receptores H04B 1/18; redes que simulan un trozo de cable de comunicación H04B 3/40). › Redes de adaptación de impedancia.

- H03K19/0175 H03 […] › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › Disposiciones para el acoplamiento; Disposiciones para la interfase (disposiciones para la interfase para computadores digitales G06F 3/00, G06F 13/00).

PDF original: ES-2507075_T3.pdf

Fragmento de la descripción:

Control de ¡mpedancia dinámica para memorias intermedias de entrada/salida.

Campo de la invención

La invención se refiere al control de impedancia para memorias intermedias de entrada/salida.

Antecedentes de la invención

Los Controladores de Memorias para Memorias Dinámicas Síncronas de Acceso Aleatorio (SDRAM) se usan en Ordenadores Personales y en una amplia variedad de productos de electrónica, en general, donde, en el producto, se integran microprocesadores y SDRAM para definir las características de control y la interfaz de usuario del producto. Los Controladores de Memorias de SDRAM permiten que los microprocesadores accedan eficientemente a SDRAM de alta velocidad cuando se ejecutan programas.

A medida que los fabricantes de chips reducen inexorablemente el tamaño característico (feature size) de los procesos que involucran silicio, llevando la tecnología del silicio hacia un rendimiento eléctrico y económico cada vez mejor, surgen importantes problemas de integridad de las señales en la interfase física entre chips en aplicaciones de sistemas, en la medida en la que las velocidades de los relojes y los datos con frecuencia se duplican con cada nueva generación. A velocidades más altas del reloj la integridad de la señal se deteriora, principalmente, debido a efectos de la línea de transmisión en la interconexión entre el chip controlador de memorias y el chip de SDRAM.

Los efectos de la línea de transmisión, que incluyen reflexiones, atenuación, interferencia cruzada y el rebote de masa (ground bounce), juegan todos ellos un papel en el deterioro de la calidad de la señal en la interconexión entre chips. Las reflexiones en la interconexión de un chip con otro, si no se gestionan correctamente, pueden destruir de forma completa la integridad de la señal en cualquier sistema de alta velocidad.

Todas las líneas de transmisión tienen una impedancia característica y una velocidad característica de la señal, que quedan definidas por la geometría de los conductores y la constante dieléctrica del medio aislante que rodea los conductores. Las reflexiones de la señal que se propagan de un lado a otro a través de líneas de transmisión pueden deteriorar la calidad de la señal hasta el punto de no resultar viables si no se controlan. No obstante, en una línea de transmisión no se producen reflexiones de la señal si la impedancia de fuente del circuito que excita un extremo de la línea de transmisión y la impedancia de terminación de circuitos en el otro extremo de la línea coinciden con la ¡mpedancia característica de la línea de transmisión. Cuando se usan circuitos de semiconductores, típicamente transistores CMOS (metal óxido semiconductor complementario), para llevar señales fuera del chip sobre pistas de placas de circuito impreso (PCB), que serán recibidas por circuitos de semiconductores en otros chips de la placa de circuito impreso, con frecuencia se producen reflexiones significativas de la señal si los extremos de recepción de las pistas no terminan con alguna impedancia que coincida fuertemente con la impedancia de la línea de transmisión.

Con anterioridad, las señales de alta velocidad se excitaban con memorias intermedias de l/O (Entrada/Salida) que presentaban impedancias de salida que eran muy inferiores a la impedancia característica de la pista de la PCB. Las pistas de la PCB se terminaban usando resistores fijos con valores de resistencia que coincidían con la impedancia característica de la pista. En algunas aplicaciones, se colocaban además resistores fijos en serie con la memoria intermedia de excitación para mejorar la integridad de la señal. La llegada de la SDRAM de DDR (Doble Velocidad de Datos) incentivó la industria de los semiconductores para encontrar formas de incorporar en su interior impedancias de fuente y de terminación con el fin de prescindir de los resistores externos fijos necesarios para igualar las impedancias de las pistas de la PCB en estos nuevos sistemas de memoria. La motivación consiste siempre en disminuir los costes y reducir el consumo de potencia. Se demostró claramente que se puede obtener una buena integridad de la señal en sistemas de Memorias de DDR cuando se dispone de una impedancia de terminación adaptada. Mientras la terminación absorba la señal que se propaga hasta el final de la línea, no se producirán reflexiones. En estos sistemas, la impedancia de fuente de los circuitos que excitan la línea se materializó intencionadamente de manera que fuera inferior a la impedancia característica de las pistas de la PCB con el fin de producir una mayor excursión de la señal con vistas a obtener una mejor inmunidad al ruido.

Se pueden diseñar circuitos de l/O CMOS de manera que se adapten a las impedancias de la línea de transmisión bastante bien en condiciones específicas aunque presentando grandes variaciones de impedancia, que superan frecuentemente la relación 2:1, durante el intervalo completo de Procesos, Voltajes y Temperaturas (PVT) esperado para el circuito. Para contrarrestar la variación de PVT, los diseñadores de circuitos han venido incorporando cierta adaptabilidad para la Excitación Fuera del Chip (Off-Chip Dríve) (OCD) y la Terminación En el Dado (On-D/e Termination) (ODT).

El documento US 27/126467 A1 describe un dispositivo para terminación en el dado y sugiere la provisión de, entre otros, una unidad de control para activar selectivamente una pluralidad de señales pull-up y una pluralidad de señales pull-down y la provisión de una unidad pull-uplpull-down para excitar selectivamente una pluralidad de

excitadores de pull-up y una pluralidad de excitadores de pull-down de acuerdo con las señales pull-up y las señales pull-down con el fin de dar salida a una resistencia correspondiente del terminal de salida en un modo de funcionamiento de lectura.

A partir del documento US 27/126466 A1 se conoce un dispositivo de semiconductores para ajustar una impedancia de salida de un excitador de salida de datos. Basándose en una comparación de una señal de prueba y una señal de referencia aplicadas en un terminal (en inglés, "pad") de prueba y en mediciones de impedancia, se ajusta una Impedancia de un terminal de entrada/salida de datos.

El documento US 24/183565 A1 se refiere a un aparato para su uso en calidad tanto de excitador fuera del chip como de circuito de terminación en el dado del chip. Un circuito de función dual permite excitar una señal desde una línea de señal sobre una línea de transmisión y terminar señales entrantes de la línea de transmisión.

En la actualidad se están usando varias soluciones para una impedancia de salida programable, especialmente en aplicaciones de Lógica de Transceptores de Alta Velocidad (HSTL) y de DDR. En muchos casos, para el control de la impedancia de salida se dispone de hasta solamente dos configuraciones de excitación. En muchos casos, las ¡mpedanclas de salida no se ajustan dinámicamente con respecto a una referencia de impedancia.

Sigue existiendo la necesidad de un circuito combinado más eficiente de excitación y terminación.

Sumario

La invención proporciona una solución de acuerdo con las reivindicaciones independientes.

Según un amplio aspecto, la invención proporciona un circuito combinado de excitación y terminación que comprende: una red de pull-up de impedancia variable; una red de pull-down de impedancia variable; por lo menos una entrada de control para ajustar una configuración de la red de pull-up; por lo menos una entrada de control para ajustar una configuración de la red de pull-down; presentando el aparato un modo de funcionamiento de terminación en el cual la red de pull-up de impedancia variable está configurada para presentar una impedancia de terminación de red de pull-up y la red de pull-down de impedancia variable está configurada para presentar una impedancia de terminación de red de pull-down, funcionando la red de pull-up y la red de pull-down en combinación como una terminación dividida; presentando el aparato un modo de funcionamiento de excitación en el cual: para excitar una salida alta, la red de pull-up está configurada para generar una impedancia específica cuando se activa; para excitar una salida baja, la red de pull-down está configurada para generar una impedancia específica cuando se activa.

En algunas formas de realización, un aparato comprende: lógica central; una pluralidad de l/O (entradas/salidas), presentando cada una de ellas un terminal respectivo de l/O; para cada l/O, un circuito combinado respectivo de excitación y terminación según se ha resumido anteriormente; funcionando los circuitos combinados de excitación y terminación de manera que generan salidas desde la lógica central y... [Seguir leyendo]

Reivindicaciones:

1. Circuito de excitación y terminación, que comprende:

una red de pull-up de impedancia variable (4) que tiene una primera pluralidad de transistores (43);

una red de pull-down de impedancia variable (42) que tiene una segunda pluralidad de transistores (45);

estando configurada cada una de entre la red de pull-up (4) y la red de pull-down (42) para presentar una impedancia deseada variando el número de transistores activados;

una primera pluralidad de bits de control de un bus de control de impedancia para establecer una configuración de terminación de la red de pull-up (4);

una segunda pluralidad de bits de control del bus de control de Impedancia para establecer una configuración de terminación de la red de pull-down (42);

una tercera pluralidad de bits de control del bus de control de Impedancia para establecer una configuración de excitación de la red de pull-up (4); y

una cuarta pluralidad de bits de control del bus de control de Impedancia para establecer una configuración de excitación de la red de pull-down (42);

en el que las primera a cuarta pluralidades de bits de control son independientes entre sí;

presentando el circuito un modo de funcionamiento de terminación en el cual la red de pull-up de impedancia variable (4) está configurada para presentar una Impedancia de terminación de red de pull-up sobre la base de la primera pluralidad de bits de control, y la red de pull-down de impedancia variable (42) está configurada para presentar una impedancia de terminación de red de pull-down sobre la base de la segunda pluralidad de bits de control, funcionando la red de pull-up (4) y la red de pull-down (42) en combinación como una terminación dividida;

presentando el circuito un modo de funcionamiento de excitación, en el cual:

para excitar una salida alta, la red de pull-up (4) está configurada para generar una impedancia específica cuando está activada sobre la base de la tercera pluralidad de bits de control; y

para excitar una salida baja, la red de pull-down (42) está configurada para generar una impedancia específica cuando está activada sobre la base de la cuarta pluralidad de bits de control.

2. Aparato, que comprende: una lógica central (1);

una pluralidad de l/O (entradas/salidas), presentando cada una de ellas un terminal respectivo de l/O; y

para cada l/O, un circuito combinado respectivo de excitación y terminación según la reivindicación 1;

funcionando los circuitos combinados de excitación y terminación de manera que generen salidas desde la lógica central (1) y actúen a modo de terminación para entradas externas para la lógica central (1).

3. Aparato según la reivindicación 2, en el que las redes de pull-up y pull-down (4, 42) se conmutan dinámicamente entre dos configuraciones de impedancia cuando cambian entre los modos de excitación y de terminación.

4. Aparato según cualquiera de las reivindicaciones 2, 3, que comprende además:

para cada l/O, una lógica de pre-excitador que comprende una lógica AND-OR-AND, que recibe una primera entrada para indicar un nivel alto de excitación, una segunda entrada para indicar un nivel bajo de excitación, y una tercera entrada para indicar terminación, y conmuta en consecuencia entre dos configuraciones de impedancia.

5. Circuito según la reivindicación 1 en combinación con una lógica de calibración que calibra las impedancias con respecto a una referencia de impedancia.

6. Aparato, que comprende:

una lógica central (1);

una pluralidad de entradas que presentan, cada una de ellas, un terminal de entrada respectivo, y una pluralidad de salidas que presentan, cada una de ellas, un terminal de salida respectivo;

para cada terminal de entrada, un circuito combinado respectivo de excitación y terminación, según cualquiera de las reivindicaciones 1, 5 configurado permanentemente para estar en modo determinación; y

para cada terminal de salida, un circuito combinado respectivo de excitación y terminación según la reivindicación 1, configurado permanentemente para estar en modo de excitación.

7. Circuito combinado de excitación y terminación según la reivindicación 1, en el que: cada una de las pluralidades de bits de control incluye un bit por transistor.

8. Circuito combinado de excitación y terminación según cualquiera de las reivindicaciones 1, 5, en el que:

la red de pull-up (4) comprende una pluralidad de transistores (43) conectados conjuntamente en paralelo, siendo controlada la impedancia variable de la red de pull-up mediante la activación selectiva de cierto número de la pluralidad de transistores (43); y

la red de pull-down (42) comprende una pluralidad de transistores (45) conectados conjuntamente en paralelo, siendo controlada la impedancia variable de la red de pull-down (42) mediante la activación selectiva de cierto número de la pluralidad de transistores (45).

9. Aparato, que comprende:

el circuito combinado de excitación y terminación según cualquiera de las reivindicaciones 1, 5, 8; y

una réplica de por lo menos parte del circuito combinado de excitación y terminación para su uso en la ejecución de la calibración.

1. Aparato según la reivindicación 9, que comprende además:

un controlador que controla la calibración que se está llevando a cabo en cuatro etapas:

1) calibración de la red de pull-up para el modo de excitación cuando una salida de datos es un nivel lógico alto;

2) calibración de la red de pull-down para el modo de excitación cuando una salida de datos es un nivel lógico

bajo;

3) calibración de la red de pull-up para el modo de terminación; y

4) calibración de la red de pull-down para el modo de terminación.

11. Aparato según la reivindicación 9, en el que la red de pull-up comprende una pluralidad de transistores mosfet de tipo P (11), y la red de pull-down comprende una pluralidad de transistores mosfet de N (112), comprendiendo además el aparato un controlador que controla la calibración que se está llevando a cabo en cuatro etapas:

1) calibración de la impedancia de salida de dispositivos N para determinar cuántos de los transistores de tipo N (112) hay que habilitar para el modo de excitación cuando una salida de datos es un nivel lógico bajo;

2) calibración de la impedancia de salida de dispositivos P para determinar cuántos de los transistores de tipo P (11) hay que habilitar para el modo de excitación cuando una salida de datos es un nivel lógico alto;

3) calibración de terminación de dispositivos N para determinar cuántos de los transistores de tipo N (112) hay que habilitar para el modo de terminación; y

4) calibración de terminación de dispositivos P para determinar cuántos de los transistores de tipo P (11) hay que habilitar para el modo de terminación.

12. Aparato según la reivindicación 9, en el que la red de pull-up (4) y la red de pull-down (42) se forman, cada una de ellas, en su totalidad, con transistores de tipo P (11) o transistores de tipo N (112), comprendiendo además el aparato:

un controlador que controla la calibración que se está llevando a cabo en dos etapas:

1) calibración de la red de pull-up para el modo de excitación cuando una salida de datos es un nivel lógico

alto; y

2) calibración de la red de pull-up para el modo de terminación.

13. Aparato según la reivindicación 1, en el que el número de transistores activados (43, 45) se hace variar progresivamente usando una codificación unaria.

14. Aparato según la reivindicación 13, que comprende además el uso de un código gray para codificar el número de transistores activados (43, 45) que se convierte a la codificación unaria.

15. Método para proporcionar excitación y terminación combinadas, comprendiendo el método:

en un modo de funcionamiento de terminación, configurar una red de pull-up de impedancia variable (4) para presentar una impedancia de terminación de red de pull-up sobre la base de una primera pluralidad de bits de control de un bus de control de impedancia y configurar una red de pull-down de impedancia variable (42) para presentar una impedancia de terminación de red de pull-down sobre la base de una segunda pluralidad de bits de control del bus de control de impedancia, funcionando la red de pull-up (4) y la red de pull-down (42) en combinación como una terminación dividida, presentando cada una de entre la red de pull-up (4) y la red de pull-down (42) una pluralidad de transistores dimensionados para proporcionar impedancias idénticas, y estando cada una de entre la red de pull-up (4) y la red de pull-down (42) configurada para presentar una impedancia deseada haciendo variar progresivamente el número de transistores activados (43, 45);

en un modo de funcionamiento de excitación, para excitar una salida alta, configurar la red de pull-up (4) para generar una primera impedancia de excitación sobre la base de una tercera pluralidad de bits de control del bus de control de impedancia; y

en el modo de funcionamiento de excitación, para excitar una salida baja, configurar la red de pull-down (42) para generar una segunda impedancia de excitación sobre la base de una cuarta pluralidad de bits de control del bus de control de impedancia;

en el que las primera a cuarta pluralidades de bits de control son independientes entre sí; y

en el que cada una de entre la red de pull-up y la red de pull-down está configurada para presentar una impedancia deseada haciendo variar el número de transistores activados.

Patentes similares o relacionadas:

Circuitos de líneas de bits globales de Memoria Estática de Acceso Aleatorio (SRAM) para reducir los fallos de energía durante los accesos de lectura de memoria, y procedimientos y sistemas relacionados, del 17 de Abril de 2019, de QUALCOMM INCORPORATED: Un circuito de línea de bits global de memoria estática de acceso aleatorio, SRAM, para una pluralidad de células de bits de SRAM, que […]

Mejora de estabilidad de lectura de memoria usando precarga selectiva de secciones de línea de bits, del 8 de Octubre de 2018, de QUALCOMM INCORPORATED: Un dispositivo de memoria que comprende: medios para precargar una primera sección de una primera línea de bits de una primera célula de bits […]

Procedimiento y aparato para reducir la corriente de fugas en formaciones de memoria, del 28 de Septiembre de 2016, de QUALCOMM INCORPORATED: Un circuito integrado que comprende: una formación de memoria que comprende una pluralidad de filas y una pluralidad de columnas de celdas de memoria ; […]

Arquitectura de núcleos en serie de memoria no volátil, del 14 de Mayo de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Tampón de página de banco de memoria que comprende matriz de memoria acoplada a bitlines (BL) y wordlines (WL), caracterizado: por primeras […]

Dispositivo de memoria para aplicaciones de memoria resistiva, del 30 de Septiembre de 2013, de QUALCOMM INCORPORATED: Un dispositivo de memoria que comprende: una célula de memoria que incluye un elemento de memoria resistivaacoplado a un transistor […]

LECTURA NO DESTRUCTIVA., del 16 de Marzo de 2007, de THIN FILM ELECTRONICS ASA: Un procedimiento para determinar un estado lógico de células de memoria seleccionadas, proporcionadas en un dispositivo pasivo de almacenamiento de datos, matricialmente […]

Circuito terminal en un inversor, del 8 de Marzo de 2019, de LSIS Co., Ltd: Un circuito terminal de un inversor, que comprende: un fotoacoplador configurado para aislar eléctricamente señales de entrada/salida, […]

Circuito eléctrico para la transmisión de señales entre dos maestros y uno o varios esclavos, del 22 de Enero de 2016, de ROBERT BOSCH GMBH: Circuito eléctrico que comprende dos maestros y uno o varios esclavos , diseñado para la transmisión de señales entre dos maestros (11, […]

Circuito eléctrico para la transmisión de señales entre dos maestros y uno o varios esclavos, del 22 de Enero de 2016, de ROBERT BOSCH GMBH: Circuito eléctrico que comprende dos maestros y uno o varios esclavos , diseñado para la transmisión de señales entre dos maestros (11, […]