Circuito de terminación para terminación en troquel.

Un circuito de terminación (500) para proporcionar terminación en troquel para un terminal (14) de undispositivo semiconductor (100;

200), en el que el terminal (14) está conectado a una parte interna (16) deldispositivo semiconductor (100; 200), el circuito de terminación (500) comprendiendo:

- una pluralidad de transistores (502, 504, 506, 508) conectados entre el terminal (14) y una fuente dealimentación (450), la pluralidad de transistores (502, 504, 506, 508) incluyendo al menos un transistor NMOS(506, 508) y al menos un transistor PMOS (502, 504);

- circuitería de control (528A; 528B) para accionar una puerta de cada uno de los al menos un transistorNMOS (506, 508) con una correspondiente tensión de puerta NMOS (EN_506, EN_508) y para accionar unapuerta de cada uno de los al menos un transistor PMOS (502, 504) con una correspondiente tensión depuerta PMOS (EN_502, EN_504), la circuitería de control (528A; 528B) estando configurada para controlarlas tensiones de puerta NMOS y PMOS a fin de colocar la pluralidad de transistores (502, 504, 506 , 508) enuna región óhmica de funcionamiento cuando está habilitada la terminación en troquel;

en el que la fuente de alimentación (450) suministra una tensión que es menor que cada una de dichastensiones de puerta NMOS (EN_506, EN_508) y mayor que cada una de dichas tensiones de puerta PMOS(EN_502, EN_504); y

en el que la circuitería de control (528A; 528B) comprende circuitos de calibración (302A; 302B) con acceso auna resistencia de referencia (306), la circuitería de calibrador (302A; 302B) configurada para llevar a cabo unproceso de calibración para identificar una pluralidad de tensiones analógicas de calibración (372, 374, 376,378) que haría que el al menos un transistor NMOS (506, 508) y el al menos un transistor PMOS (502, 504)impartan colectivamente una resistencia sustancialmente igual a la resistencia de referencia (306) si sesuministran a cada uno de dichos transistores MOS como las tensiones de puerta correspondientes NMOS yPMOS, respectivamente.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/CA2010/000027.

Solicitante: MOSAID TECHNOLOGIES INCORPORATED.

Nacionalidad solicitante: Canadá.

Dirección: 11 Hines Road, Suite 203 Ottawa, ON K2K 2X1 CANADA.

Inventor/es: GILLINGHAM,PETER B.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C5/06 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 5/00 Detalles de memorias cubiertos por el grupo G11C 11/00. › Disposiciones para interconectar eléctricamente elementos de almacenamiento, p. ej. por cableado.

- H01L23/50 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › para dispositivos de circuito integrado (H01L 23/482 - H01L 23/498 tienen prioridad).

- H03H11/46 H […] › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03H REDES DE IMPEDANCIA, p. ej. CIRCUITOS RESONANTES; RESONADORES (medidas, ensayos G01R; disposiciones para producir una reverberación sonora o un eco G10K 15/08; redes de impedancia o resonadores que se componen de impedancias distribuidas, p. ej. del tipo guía de ondas, H01P; control de la amplificación, p. ej. control del ancho de banda de los amplificadores, H03G; sintonización de circuitos resonantes, p. ej. sintonización de circuitos resonantes acoplados, H03J; redes para modificar las características de frecuencia de sistemas de comunicación H04B). › H03H 11/00 Redes que utilizan elementos activos. › Redes de un acceso.

PDF original: ES-2445402_T3.pdf

Fragmento de la descripción:

Circuito de terminación para terminación en troquel

ANTECEDENTES

Cuando una señal se desplaza a lo largo de un camino que tiene una discontinuidad de impedancia (o "desajuste") , la señal se refleja en parte. La señal reflejada interfiere con la señal original y esto puede resultar en una pérdida de integridad de la señal y en que se detecte un nivel de señal incorrecto. Para mitigar la aparición de la señal de reflexión, es beneficioso colocar circuitos con la cantidad equivalente de impedancia en el punto de discontinuidad. Esto se conoce como "terminación". Por ejemplo, las resistencias se pueden colocar en las placas base de ordenadores para finalizar los buses de alta velocidad.

Aunque las resistencias de terminación reducen los reflejos en un extremo de la ruta de señal, no son capaces de evitar las reflexiones resultantes de ramales que conectan con otros troqueles de semiconductores en varios puntos a lo largo del camino. Esta situación puede surgir, por ejemplo, cuando múltiples módulos de memoria están conectados a lo largo de un bus de memoria. Una señal que se propaga desde un controlador de memoria a lo largo del bus de memoria se encuentra con una discontinuidad de impedancia en cada ramal que conduce a un módulo de memoria en particular. La señal que se propaga a lo largo del ramal que conduce al módulo de memoria particular, se refleja de nuevo en el bus de memoria, introduciendo de este modo el ruido no deseado en la señal.

Por consiguiente, es útil proporcionar a cada troquel semiconductor su propio circuito de terminación. Proporcionar este circuito de terminación en el mismo troquel semiconductor que incluye un transmisor/receptor de bus se conoce como terminación en troquel (ODT: “On-Die Termination” en inglés”) . La terminación en troquel puede reducir el número de elementos de resistencia y cableados complejos en la placa base. Por lo tanto, además de mejorar la integridad de la señal, que permite a los componentes operar a frecuencias más altas, la terminación en troquel permite un diseño de sistema más simple y económico.

Sin embargo, las técnicas convencionales de terminación en troquel han tendido a ser de alto consumo de potencia y/o inflexibles.

En US 2002/0180479 A1 se divulga una terminación de polarización, que se forma utilizando un transistor de metal óxido semiconductor de tipo N (NMOS) conectado en paralelo a un transistor de óxido metal semiconductor de tipo P (PMOS) . Esta terminación logra una resistencia constante usando la tensión de control más alta en el electrodo de puerta. Esta terminación de polarización que usa transistores NMOS incluye un transistor PMOS conectado en paralelo con un transistor NMOS, en el que un extremo está conectado a una fuente de tensión con el otro extremo conectado a un terminal de entrada/salida. La puerta del transistor NMOS está conectada a una tensión de control y el sustrato a tierra, en donde la puerta del transistor PMOS está conectada a la tensión de control con una fase invertida y el sustrato a la fuente de tensión.

El documento US 7, 417, 452 B1 divulga las técnicas para ajustar individualmente la impedancia de terminación en troquel que se genera mediante memorias temporales de entrada y salida (IO) en un panel de entrada/salida (IO) en un circuito integrado. Este documento divulga que las memorias temporales IO en un panel de IO pueden generar diferentes impedancias de terminación en troquel, y como resultado, un panel de IO puede admitir más de una clase de interfaces de memoria. De acuerdo con este documento, un bloque de calibración OCT genera un código de calibración digital de terminación en troquel (OCT) , en el que en algunas realizaciones, los circuitos en los paneles IO se puede configurar para cambiar el código de calibración OCT, uno o más bits para ajustar la impedancia de terminación en troquel en serie y/o en paralelo en una o más memorias temporales IO.

RESUMEN

De acuerdo con un aspecto amplio, la presente invención pretende proporcionar un circuito de terminación para proporcionar la terminación en troquel para un terminal del dispositivo semiconductor de acuerdo con la reivindicación 1. El circuito de terminación comprende una pluralidad de transistores conectados entre el terminal y una fuente de alimentación, la pluralidad de transistores que incluye al menos un transistor NMOS y al menos un transistor PMOS y los circuitos de control para accionar una puerta de cada uno de los al menos un transistor NMOS con una tensión de puerta NMOS correspondiente y para el accionamiento de una puerta de cada uno de los al menos un transistor PMOS con una tensión de puerta PMOS correspondiente, el circuito de control está configurado para controlar las tensiones de puerta NMOS y PMOS a fin de colocar la pluralidad de transistores en una región óhmica de funcionamiento cuando la terminación en troquel está habilitada. La fuente de alimentación suministra una tensión que es menor que cada una de dichas tensiones de puerta NMOS y mayor que cada una de dichas tensiones de puerta PMOS.

Este y otros aspectos y características de la presente invención se harán evidentes para los expertos normales en la técnica tras la revisión de la siguiente descripción de realizaciones específicas de la invención junto con los dibujos

adjuntos.

Breve descripción de los dibujos En los dibujos adjuntos:

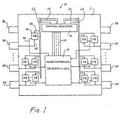

Las Figuras 1 y 2 son diagramas de un circuito de terminación para proporcionar terminación en troquel para un terminal de un dispositivo semiconductor, de acuerdo con realizaciones no limitativas específicas de la presente invención;

La Figura 3A es un diagrama de bloques de un circuito de control de terminación que está equipado con calibración digital, para su uso con el circuito de terminación de las Figuras 1 y 2;

La Figura 3B es un diagrama de bloques de un circuito de control de terminación equipado con funcionalidad de calibración analógica, para su uso con el circuito de terminación de las Figuras 1 y 2;

La Figura 3C es un diagrama de circuito de un multiplexor que se puede utilizar en el circuito de control de terminación de la Figura 3B;

Las Figuras 4A y 4B son diagramas de circuito de un generador de tensión para generar una tensión que se puede suministrar al circuito de terminación de las Figuras 1 y 2;

La Figura 5 es un diagrama de circuito de un circuito de terminación para proporcionar terminación en troquel para una pluralidad de terminales de un dispositivo semiconductor, de acuerdo con una realización no limitativa específica de la presente invención;

Las Figuras 6A y 6B son diagramas de circuito que muestran versiones complementarias de un desplazador de nivel que puede ser utilizado para ampliar el rango de una señal de tensión, de acuerdo con realizaciones no limitativas específicas de la presente invención; y

Las Figuras 7 y 8 son diagramas de circuito de un circuito de terminación para proporcionar terminación en troquel para un terminal de un dispositivo semiconductor, de acuerdo con otras realizaciones no limitativas específicos de la presente invención.

Ha de entenderse expresamente que la descripción y los dibujos son pretenden ilustrar ciertas realizaciones de la invención y son una ayuda para su comprensión. No están destinadas a ser una definición de los límites de la invención.

Descripción detallada Con referencia a las Figuras 1 y 2, se muestra un circuito de terminación 500 para la terminación en troquel de un terminal 14 conectado a una parte interna 16 de un dispositivo semiconductor 100, 200. El troquel de terminación puede usarse para preservar la integridad de una señal que se transmite y/o recibe a través del terminal 14. De acuerdo con ello, el terminal 14 puede ser un terminal de entrada, un terminal de salida o un terminal de entrada/salida bidireccional. En ciertas realizaciones no limitativas, el terminal 14 puede configurarse para transmitir y/o recibir señales de datos que varían entre dos niveles de tensión representativas de los correspondientes valores lógicos. El dispositivo semiconductor 100, 200 que incluye la parte interna 16 y el terminal 14 pueden ser un troquel de memoria (tal como una memoria de acceso aleatorio dinámico (DRAM) , DRAM síncrona (SDRAM) , doble velocidad de datos (DDR) SDRAM, etc.) o cualquier otro tipo de dispositivo semiconductor que puede beneficiarse de la terminación en troquel.

Aunque el circuito de terminación 500 se muestra estando conectado dentro del dispositivo de semiconductores 100, 200 a un punto (o nodo) 18 que está entre el terminal 14 y la parte interna 16 del dispositivo semiconductor 100, 200, se debe apreciar... [Seguir leyendo]

Reivindicaciones:

1. Un circuito de terminación (500) para proporcionar terminación en troquel para un terminal (14) de un dispositivo semiconductor (100; 200) , en el que el terminal (14) está conectado a una parte interna (16) del 5 dispositivo semiconductor (100; 200) , el circuito de terminación (500) comprendiendo:

-una pluralidad de transistores (502, 504, 506, 508) conectados entre el terminal (14) y una fuente de alimentación (450) , la pluralidad de transistores (502, 504, 506, 508) incluyendo al menos un transistor NMOS (506, 508) y al menos un transistor PMOS (502, 504) ;

- circuitería de control (528A; 528B) para accionar una puerta de cada uno de los al menos un transistor NMOS (506, 508) con una correspondiente tensión de puerta NMOS (EN_506, EN_508) y para accionar una puerta de cada uno de los al menos un transistor PMOS (502, 504) con una correspondiente tensión de puerta PMOS (EN_502, EN_504) , la circuitería de control (528A; 528B) estando configurada para controlar

las tensiones de puerta NMOS y PMOS a fin de colocar la pluralidad de transistores (502, 504, 506 , 508) en una región óhmica de funcionamiento cuando está habilitada la terminación en troquel;

en el que la fuente de alimentación (450) suministra una tensión que es menor que cada una de dichas tensiones de puerta NMOS (EN_506, EN_508) y mayor que cada una de dichas tensiones de puerta PMOS

(EN_502, EN_504) ; y

en el que la circuitería de control (528A; 528B) comprende circuitos de calibración (302A; 302B) con acceso a una resistencia de referencia (306) , la circuitería de calibrador (302A; 302B) configurada para llevar a cabo un proceso de calibración para identificar una pluralidad de tensiones analógicas de calibración (372, 374, 376,

378) que haría que el al menos un transistor NMOS (506, 508) y el al menos un transistor PMOS (502, 504) impartan colectivamente una resistencia sustancialmente igual a la resistencia de referencia (306) si se suministran a cada uno de dichos transistores MOS como las tensiones de puerta correspondientes NMOS y PMOS, respectivamente.

2. El circuito de terminación definido en la reivindicación 1, en el que para colocar la pluralidad de transistores (502, 504, 506, 508) en una región óhmica de funcionamiento, la puerta de cada uno de los al menos un transistor NMOS (506, 508) es alimentada por una primera tensión y la puerta de cada uno de los al menos un transistor PMOS (502, 504) es alimentada por una segunda tensión y en el que la tensión suministrada por la fuente de alimentación (450) está sustancialmente a medio camino entre la primera tensión y la segunda tensión.

3. El circuito de terminación definido en la reivindicación 1, en el que:

- el al menos un transistor NMOS (506, 508) incluye al menos dos transistores NMOS (506, 508) , los al

menos dos transistores NMOS (506, 508) siendo colocados en la región óhmica de funcionamiento mediante las correspondientes tensiones de puerta NMOS (EN_506, EN_508) ajustadas a diferentes niveles, y

- el al menos un transistor PMOS (502, 504) incluyendo al menos dos transistores PMOS (502, 504) , los al menos dos transistores PMOS (502, 504) siendo colocados en la región óhmica de funcionamiento mediante las correspondientes tensiones de puerta (PMOS EN_502, EN_504) ajustadas a diferentes niveles.

4. El circuito de terminación definido en la reivindicación 1, que comprende además la fuente de alimentación, la fuente de alimentación comprendiendo una etapa de polarización (602) , una etapa de salida (604) y un condensador (608) , la etapa de salida (604) incluyendo un par complementario de transistores MOS (614, 616) , en los que la tensión suministrada por la fuente de alimentación se toma de una unión (613) entre el par

complementario de transistores MOS (614, 616) , estando conectado el condensador (608) eléctricamente entre la unión (613) y un potencial de referencia.

5. El circuito de terminación definido en la reivindicación 1, que comprende además la fuente de alimentación,

comprendiendo la fuente de alimentación: 55

(i) una cadena de polarización (650) ;

(ii) un amplificador operacional (654) en una configuración de ganancia unitaria que tiene una entrada

conectada a la cadena de polarización y una salida; y 60

(iii) un condensador (658) conectado entre la salida del amplificador operacional y un potencial de referencia;

en el que la tensión suministrada por la fuente de alimentación se toma de una unión entre la salida del amplificador operacional y el condensador.

6. El circuito de terminación definido en la reivindicación 1, en el que:

- cada uno de los al menos un transistor NMOS (506, 508) comprende la puerta y un par de electrodos

portadores de corriente (506S, 508S, 506D, 508D) , en donde uno de los electrodos portadores de corriente está conectado al terminal (14) , en el que el otro de los electrodos portadores de corriente está conectado a la fuente de alimentación (450) y en el que la puerta es alimentada por la correspondiente tensión de puerta NMOS (EN_506, EN_508) desde la circuitería de control (528A; 528B) ;

- cada uno de los al menos un transistor PMOS (502, 504) comprende la puerta y un par de electrodos portadores de corriente (502s, 504s, 502D, 504D) , en donde uno de los electrodos portadores de corriente está conectado al terminal (14) , en donde el otro de los electrodos portadores de corriente está conectado a la fuente de alimentación (450) y en el que la puerta es alimentada por la correspondiente tensión de puerta PMOS (EN_502, EN_504) desde la circuitería de control (528A; 528B) ;

- cada uno de los al menos un transistor NMOS (506, 508) comprende además un electrodo de sustrato (506T, 508T) conectado a una fuente de alimentación (420) que suministra una primera tensión de sustrato, y en donde cada uno de los al menos un transistor PMOS (502, 504) comprende además un electrodo de sustrato (502T, 504T) conectado a una fuente de alimentación (410) que suministra una segunda tensión de

sustrato mayor que la primera tensión de sustrato; y

- colocar la pluralidad de transistores (502, 504, 506, 508) en una región óhmica de funcionamiento, estableciéndose las tensiones de puerta NMOS (EN_506, EN_508) en una primera tensión común y estableciéndose las tensiones de puerta PMOS (EN_502, EN_504) en una segunda tensión común, en donde

la segunda tensión de sustrato es igual a la primera tensión, y en donde la primera tensión de sustrato es igual a la segunda tensión.

7. El circuito de terminación definido en la reivindicación 6, que comprende además: 30

- un desplazador de nivel (852) entre la circuitería de control (528A; 528B) y la puerta de uno correspondiente de los al menos un transistor NMOS (506, 508) , el desplazador de nivel configurado para emitir la correspondiente tensión de puerta NMOS (EN_506+) en base a una tensión de entrada (EN_506) proporcionada por la circuitería de control (528A; 528B) , teniendo la tensión de entrada un rango dinámico

menor que la tensión de puerta NMOS correspondiente; y

- un segundo desplazador de nivel (802) entre la circuitería de control (528A; 528B) y la puerta de uno correspondiente de los al menos un transistor PMOS (502, 504) ; el segundo desplazador de nivel configurado para entregar la tensión de puerta PMOS correspondiente (EN_502+) en base a una segunda tensión de

entrada (EN_502) proporcionada por la circuitería de control (528A; 528B) , teniendo la segunda tensión de entrada un rango dinámico menor que la correspondiente tensión de puerta PMOS.

8. El circuito de terminación definido en la reivindicación 1, seleccionándose la pluralidad de transistores (502,

504, 506, 508) como transistores MOS, el circuito de terminación comprendiendo además al menos un transistor MOS no seleccionado conectado entre el terminal (14) y la fuente de alimentación (450 ) , cada uno de los al menos un transistor MOS no seleccionados teniendo una puerta alimentada por una tensión de puerta correspondiente que coloca el al menos un transistor MOS no seleccionado en un estado apagado cuando está habilitada la terminación en troquel y también cuando la terminación en troquel está

deshabilitada.

9. El circuito de terminación definido en la reivindicación 8, en el que los transistores MOS seleccionados y el al menos un transistor MOS no seleccionado constituyen un conjunto general de transistores MOS, en el que la circuitería de calibrador (302A; 302B) está configurada además para llevar a cabo un proceso de calibración 55 para identificar la pluralidad de transistores MOS seleccionados dentro del conjunto global de transistores MOS.

10. El circuito de terminación definido en la reivindicación 8, en el que la resistencia eléctrica entre la fuente de alimentación (450) y el terminal (14) es atribuible en una parte sustancial a la pluralidad de transistores MOS 60 seleccionados y el al menos un transistor MOS no seleccionado.

11. El circuito de terminación definido en la reivindicación 1, en el que:

- la circuitería de calibrador (302A; 302B) lleva a cabo el proceso de calibración en respuesta a detectar que 65 una señal de habilitación de calibración recibida ha sido activada; o

- la circuitería de control (528A; 528B) comprende además un multiplexor (305B) para hacer que las

tensiones analógicas de calibración (372, 374, 376, 378) se transfieran a las tensiones de puerta

correspondientes NMOS y PMOS, respectivamente, cuando está habilitada la terminación en troquel; o

5

- el circuito de calibrador (302A; 302B) comprende elementos de circuito internos que presentan cada uno un

comportamiento como una función de una tensión aplicada que corresponde a un comportamiento de uno de

los al menos un transistor NMOS (506, 508) y el al menos un transistor PMOS (502, 504) como una función

de las correspondientes tensiones de puerta NMOS o PMOS, en donde el proceso de calibración comprende

10 determinar las tensiones de calibración analógica (372, 374, 376, 378) como los niveles de tensión aplicada

que resultan en los elementos de circuito internos colectivamente exhibiendo una resistencia que coincide

sustancialmente con la resistencia de referencia, o

- el circuito de calibrador tiene acceso a una tabla de consulta que especifica un comportamiento de

15 resistencia del al menos un transistor NMOS (506, 508) y el al menos un transistor PMOS (502, 504) como

una función de las correspondientes tensiones de puerta NMOS o PMOS, en donde el proceso de calibración

comprende consultar la tabla de búsqueda en base a la resistencia de referencia (306) para determinar

tensiones particulares, siendo las tensiones particulares las tensiones analógicas de calibración (372, 374,

376, 378) .

20

12. Un dispositivo semiconductor (100, 200) con terminación en troquel, que comprende el circuito de terminación

(500) de acuerdo con cualquiera de las reivindicaciones 1 a 11.

Circuito deCalibración Cerrojo Circuito de Habilitación Analógico Circuito de MultiplexorCalibración Parte Interna

Patentes similares o relacionadas:

Dispositivo y procedimiento para el procesamiento de cuadros de datos en serie, del 11 de Octubre de 2018, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo para el procesamiento de cuadros de datos en serie, que comprende una unidad de convertidor en serie-paralelo , una unidad de evaluación […]

Memoria que usa un bus de nodo único de datos, direcciones y control, del 12 de Febrero de 2014, de MICROCHIP TECHNOLOGY INCORPORATED: Un sistema digital, que comprende una memoria que usa un bus de nodo único, de datos, direcciones y control, que comprende: una matriz de memoria adaptada […]

Almacenamiento de datos y estructuras apilables, del 18 de Septiembre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un sistema que comprende una pila incluyendo: un primer dispositivo de memoria ; un segundo dispositivo de memoria […]

Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N, del 21 de Agosto de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador,que comprende:

dotar a un chip […]

Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N, del 21 de Agosto de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador,que comprende:

dotar a un chip […]

Dispositivo en cascada de cadena de margarita, del 4 de Junio de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un dispositivo semiconductor (410a, ..., 410d) que comprende: memoria; circuitos de entrada de reloj configurados para recibir una señal de reloj (SCLK); circuitos de […]

Dispositivo de Cascada de Cadena Tipo Margarita, del 12 de Septiembre de 2012, de MOSAID TECHNOLOGIES INCORPORATED: Un sistema que tiene una pluralidad de dispositivos conectados en serie que incluyen por lo menosprimeros y segundos dispositivos, caracterizado porque: el […]

SISTEMA DE MEDICION EN RED CON SENSORES Y UN PUENTE., del 16 de Marzo de 2007, de VLAAMSE INSTELLING VOOR TECHNOLOGISCH ONDERZOEK (VITO): Sistema de medición configurado para la medición de los valores físicos en una red de sensores de tipo bus, comprendiendo dicha red de sensores de tipo bus por […]

CONJUNTO DE MODULO DE MEMORIA QUE UTILIZA CHIPS PARCIALMENTE DEFECTUOSOS, del 1 de Noviembre de 2007, de CELETRONIX INTERNATIONAL, LTD

CELETRONIX USA, INC.: Procedimiento para la implementación selectiva de un reforzador de reloj, comprendiendo dicho procedimiento: montar un reforzador de reloj en una placa […]

CONJUNTO DE MODULO DE MEMORIA QUE UTILIZA CHIPS PARCIALMENTE DEFECTUOSOS, del 1 de Noviembre de 2007, de CELETRONIX INTERNATIONAL, LTD

CELETRONIX USA, INC.: Procedimiento para la implementación selectiva de un reforzador de reloj, comprendiendo dicho procedimiento: montar un reforzador de reloj en una placa […]