Método para apilar circuitos integrados conectados en serie y dispositivo multichip fabricado a partir del mismo.

Dispositivo multichip que incluye un par apilado de chips de circuito integrado,

comprendiendo el dispositivo:

un chip superior (308, 5 508) que presenta:

uno o más terminales para señales de entrada (A3 a A6) para su conexión con señales de entrada externas;

uno o más terminales para señales de conexión común (A1, A2, B1, B2), estando dispuesto cada terminal para señales de conexión común simétricamente en torno a una línea central (312) del chip superior con respecto a un terminal duplicado para señales de conexión común;

uno o más terminales para señales de salida (B3 a B6) dispuestos simétricamente en torno a la línea central del chip superior con respecto a unos terminales respectivos para señales de entrada;

un chip inferior (310, 510) que tiene una disposición de terminales para señales sustancialmente idéntica a la del chip superior, estando invertida la orientación del chip inferior con respecto a la del chip superior;

una vía pasante de chips de conexión en paralelo (314, 518) que conecta un terminal para señales de conexión común del chip superior en paralelo con su terminal duplicado para señales de conexión común en el chip inferior; y

una vía pasante de chips de conexión en serie (316, 520) que conecta un terminal para señales de salida del chip superior en serie con su terminal para señales de entrada respectiva en el chip inferior.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/CA2008/002235.

Solicitante: MOSAID TECHNOLOGIES INCORPORATED.

Nacionalidad solicitante: Canadá.

Dirección: 11 Hines Road, Suite 203 Ottawa, ON K2K 2X1 CANADA.

Inventor/es: PYEON,HONG BEOM.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H01L23/50 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › para dispositivos de circuito integrado (H01L 23/482 - H01L 23/498 tienen prioridad).

- H01L23/538 H01L 23/00 […] › estando la estructura de interconexión entre una pluralidad de chips semiconductores situada en el interior o encima de sustratos aislantes.

- H01L25/065 H01L […] › H01L 25/00 Conjuntos consistentes en una pluralidad de dispositivos semiconductores o de otros dispositivos de estado sólido (dispositivos consistentes en una pluralidad de componentes de estado sólido formados en o sobre un sustrato común H01L 27/00; módulos fotovoltaicos o conjuntos de células fotovoltaicas H01L 31/042). › siendo los dispositivos de un tipo previsto en el grupo H01L 27/00.

PDF original: ES-2499392_T3.pdf

Fragmento de la descripción:

Método para apilar circuitos integrados conectados en serie y dispositivo multichip fabricado a partir del mismo. Referencia cruzada a solicitudes relacionadas

La presente solicitud reivindica la prioridad de la solicitud de patente provisional US n.° 61/15.345 presentada el 2 de diciembre de 27, la solicitud de patente provisional US n.° 61/32.23 presentada el 28 de febrero de 28, la solicitud de patente US n.° de serie 12/168.354 presentada el 7 de julio de 28, y la solicitud de patente US n.° de serie 12/236.874 presentada el 24 de septiembre de 28.

Campo de la invención

La presente invención se refiere en general a circuitos integrados, o chips. Más particularmente, la presente invención se refiere a la disposición de conexiones de chips para el apilamiento de los mismos.

Antecedentes de la invención

Esta solicitud está relacionada con la publicación de solicitud de patente de estados unidos, presentada previamente, n.° 27/76479, titulada "Múltiple Independent Serial Link Memory", presentada el 3 de diciembre de 25, cuyas enseñanzas completas se incorporan a la presente a título de referencia.

Esta solicitud está relacionada con la publicación de solicitud de patente de Estados Unidos, continuación parcial, presentada previamente, n.° 27/19833, titulada "Daisy Chain Cascading Devices", presentada el 8 de noviembre de 26, cuyas enseñanzas completas se incorporan a la presente a título de referencia.

Esta solicitud está relacionada con la solicitud de patente provisional de Estados Unidos, presentada previamente, n° de serie 61/13.36, titulada "Memory System With Point-To-Point Ring Topology", presentada el 12 de diciembre de 27, cuyas enseñanzas completas se incorporan a la presente a título de referencia.

Esta solicitud está relacionada con la solicitud de patente provisional de Estados Unidos, presentada previamente, n.° de serie 61/15.345, titulada "Method For Stacklng Serlally-Connected Integrated Circuits And Multi-Chip Device Made From Same", presentada el 2 de diciembre de 27, cuyas enseñanzas completas se incorporan a la presente a título de referencia.

La integración de múltiples chips en un único conjunto encapsulado ha constituido una tendencia principal en la industria de los semiconductores con el fin de reducir el volumen y los costes de productos de consumo. Hasta el momento, en productos reales se han introducido y usado muchos métodos de encapsulamiento multi-chip.

A medida que la densidad de los chips ha aumentado, el propio encapsulamiento de los chips ha cambiado significativamente en términos de tamaño y números de pines. En relación con los problemas de la alta densidad de los chips de memoria y los factores de forma pequeños, los MCP (Conjuntos Encapsulados Multi-Chip) son una buena solución para conseguir que cualquier sistema sea más compacto. Hasta el momento, la mayor parte del apilamiento de chips se ha realizado con la tecnología de unión con cables. No obstante, en cada chip que se va a conectar con cables de unión se requiere tanto espacio como el necesario para los terminales (pacte) de unión convencionales.

Con el fin de elaborar MCPs, se requiere un bastidor de conductores (lead-frame) más complicado. Además, cada chip se debería disponer de manera que posea una separación suficiente, lo cual da como resultado el incremento del factor de forma. La tecnología de unión con cables también puede reducir la durabilidad mecánica del MCP al quedar dispuestos los cables en ángulos extraños.

Adicionalmente, la unión con cables requiere espaciadores para cada chip. Esto da como resultado un incremento de la altura del apilamiento, lo cual hace que la manipulación y el ensamblaje del apilamiento de dispositivos integrados resulte más exigente en comparación con apllamlentos que no comprenden espaciadores. Además, la longitud de los cables de unión es mayor en un apilamiento de chips con espaciadores, lo cual conduce a un rendimiento eléctrico reducido del sistema de apilamiento de chips. Además, la resistencia térmica de un apilamiento de dispositivos integrados que tiene un espadador en los chips de dispositivo Integrado se incrementa.

Los apilamientos de dispositivos integrados convencionales tienen tendencia a producir cortocircuitos eléctricos de los cables de unión cuando se aplica material espaciador y cuando se poslclona un dispositivo integrado sobre el material espaciador. Esto hace que se reduzca la fiabilidad y el rendimiento de producción. El apilamiento convencional de dados basado en cables de unión no proporciona un encapsulamiento compacto. La longitud de los cables y la distribución de las conexiones también dan como resultado efectos de carga elevados.

Otro planteamiento consiste en usar una vía entre chips. La vía pasante de chips puede constituir un mejor

planteamiento para solucionar la cuestión del ruido por las características eléctricas.

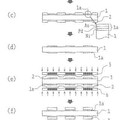

La figura 1 muestra una vista superior parcial 12 y una vista en sección transversal 14 de un apilamiento multi-chip o dispositivo multi-chip convencional 1 realizado con el uso de la tecnología de vías pasantes de chips. En la vista superior 12, se muestra una pluralidad de terminales para señales A1 a A6 y B1 a B6, que facilitan la conexión de señales internas y externas con el chip. En la vista superior no se observan las vías en sí. La vista en sección transversal 14 se toma a lo largo de la línea A-A de la vista superior. El método de vías pasantes de chips usado en la figura 1 se refiere a conexiones de entrada o salida comunes, o conexiones paralelas. Debido a esto, el único problema de fabricación real fue hasta qué profundidad se podían perforar y realizar agujeros limpios para conectar los mismos pines entre sí como una conexión común. En el caso de conexiones multi-derivación entre los mismos chips de memoria, el alineamiento de cada chip es tan importante que todos los chips se alinean sin ningún espaciador entre terminales, el cual es necesario en la conexión con cables de unión para el encapsulamiento multi- chip.

Otros planteamientos conocidos se refieren al uso de vías pasantes de chips para conexiones paralelas entre chips. Por ejemplo, la publicación de solicitud de patente de Estados Unidos n.° US 27/246257-A1 describe un circuito de memoria en el cual se conectan chips de memoria por medio de vías pasantes de silicio en una topología multi- derivación. No obstante, en este planteamiento, la vía se extiende a través de todos los chips de memoria de un apilamiento, limitando así el tipo de conectividad que se puede proporcionar.

El documento US 27/115712 A1 se refiere a un sistema, un módulo, y un aparato y método para formar un dispositivo de memoria microelectrónico. En una forma de realización, un sistema incluye un procesador y un controlador acoplado al procesador con por lo menos un módulo de memoria acoplado al controlador, incluyendo el módulo un par de dispositivos de memoria posicionados en oposición sobre superficies respectivas de un sustrato e interconectados por miembros que se extienden a través del sustrato que acoplan terminales de los dispositivos, seleccionándose los terminales para incluir un grupo de terminales que están configurados para comunicar señales funclonalmente compatibles.

El documento US 26/1176 A1 da a conocer un dispositivo de semiconductores en apilamiento que incluye una pluralidad de chips de semiconductor y un trayecto conductor que se extiende a través de por lo menos uno de los chips de semiconductor. Los chips de semiconductor están apilados conjuntamente. Los chips de semiconductor se conectan eléctricamente por el trayecto conductor, y el trayecto conductor tiene una pluralidad de conexiones pasantes que se extienden a través del chip de semiconductor correspondiente.

Por lo tanto, es deseable proporcionar un conjunto encapsulado multi-chip, o apilamiento de chips, que use vías pasantes de chips para proporcionar otras conexiones para conexiones en cadena (daisy chain) con el fin de mejorar el rendimiento de las señales.

Sumario de la invención

Es un objetivo de la presente invención eludir o mitigar por lo menos una desventaja de los dispositivos multi-chip previos.

En un primer aspecto, la presente invención proporciona un dispositivo multi-chip que incluye un par apilado de chips de circuito integrado que comprenden un chip superior y un chip inferior según se expone en la reivindicación 1. El chip superior tiene uno o más terminales para señales de entrada para su conexión con señales de entrada externas y uno o más terminales para señales de conexión común. Cada terminal para señales de conexión común está dispuesto simétricamente sobre o en torno a una... [Seguir leyendo]

Reivindicaciones:

1. Dispositivo multichip que incluye un par apilado de chips de circuito integrado, comprendiendo el dispositivo: un chip superior (38, 58) que presenta:

uno o más terminales para señales de entrada (A3 a A6) para su conexión con señales de entrada externas;

uno o más terminales para señales de conexión común (A1, A2, B1, B2), estando dispuesto cada terminal para señales de conexión común simétricamente en torno a una línea central (312) del chip superior con respecto a un terminal duplicado para señales de conexión común;

uno o más terminales para señales de salida (B3 a B6) dispuestos simétricamente en torno a la línea central del chip superior con respecto a unos terminales respectivos para señales de entrada;

un chip inferior (31, 51) que tiene una disposición de terminales para señales sustancialmente idéntica a la del chip superior, estando invertida la orientación del chip inferior con respecto a la del chip superior;

una vía pasante de chips de conexión en paralelo (314, 518) que conecta un terminal para señales de conexión común del chip superior en paralelo con su terminal duplicado para señales de conexión común en el chip inferior; y

una vía pasante de chips de conexión en serie (316, 52) que conecta un terminal para señales de salida del chip superior en serie con su terminal para señales de entrada respectiva en el chip inferior.

2. Dispositivo según la reivindicación 1, en el que dicho uno o más terminales para señales de entrada, dicho uno o más terminales para señales de conexión común y dicho uno o más terminales para señales de salida están dispuestos a lo largo de un único borde del chip superior.

3. Dispositivo según cualquiera de las reivindicaciones 1 o 2, que comprende además una pluralidad de vías pasantes de chips, de conexión en serie, que conectan terminales para señales de salida del chip superior en serie con sus terminales respectivos para señales de entrada del chip inferior.

4. Dispositivo según cualquiera de las reivindicaciones 1, 2 o 3, que comprende además una pluralidad de vías pasantes de chips, de conexión en paralelo, que conectan terminales para señales de conexión común del chip superior en paralelo con sus terminales duplicados para señales de conexión común del chip inferior.

5. Dispositivo según cualquiera de las reivindicaciones 1 a 4, en el que dicho uno o más terminales para señales de entrada están dispuestos en el mismo lado de la línea central del chip superior.

6. Dispositivo según cualquiera de las reivindicaciones 1 a 5, en el que el chip superior y el chip inferior están alineados de modo que no se produce sustancialmente ninguna desviación.

7. Dispositivo según cualquiera de las reivindicaciones 1 a 6, en el que un borde del chip superior está alineado verticalmente con un borde correspondiente del chip inferior.

8. Dispositivo según cualquiera de las reivindicaciones 1 a 7, en el que el chip superior y el chip inferior están encarados en la misma dirección entre ellos.

9. Dispositivo según la reivindicación 8, en el que un lado del chip superior que presenta unos terminales para señales seleccionados está encarado en la misma dirección que un lado del chip inferior que tiene los mismos terminales para señales seleccionados.

1. Método para apilar circuitos integrados conectados en serie, que comprende:

invertir un primer chip (31, 51) de manera que su lado superior portador de transistores quede encarado en una primera dirección para convertirse en un chip inferior;

colocar un segundo chip (38, 58) encima del primer chip invertido, siendo el segundo chip sustancialmente idéntico en cuanto a disposición y colocación de los terminales con respecto al primer chip, estando orientado el segundo chip de manera que su lado superior portador de transistores queda encarado en un segundo sentido opuesto al primer sentido;

crear orificios de vías pasantes de terminales y de chips para facilitar la conexión de terminales para señales (A1 a A6, B1 a B6) del chip superior con terminales para señales, correspondientes (A1 a A6, B1 a B6) del chip inferior, con el fin de crear por lo menos una conexión en serie que conecta un terminal para señales de salida

(B3 a B6) del chip superior en serie con su terminal respectivo para señales de entrada (A3 a A6) en el chip inferior, y por lo menos una conexión en paralelo que conecta un terminal para señales de conexión común (A1, A2, B1, B2) del chip superior en paralelo con su terminal duplicado para señales de conexión común (A1, A2, B1, B2) en el chip Inferior;

disponer una capa de aislamiento en los orificios de las vías; y

disponer un conductor en los orificios de las vías para crear conexiones pasantes de vías (314, 316; 518, 52) entre los terminales del chip superior y el chip inferior con el fin de crear un par apilado de chips de circuitos integrados,

en el que los terminales para señales de conexión común de cada chip están dispuestos simétricamente en torno

a una línea central del chip,

y en el que los terminales para señales de salida (B3 a B6) de cada chip están dispuestos simétricamente en torno a la línea central del chip con respecto a los terminales para señales de entrada (A3 a A6) del chip.

11. Método según la reivindicación 1, en el que la etapa de creación de los orificios de vías pasantes determínales y de chips comprende crear un primer orificio de vía pasante de chips y pasante de terminales para facilitar la conexión entre un terminal para señales de conexión común del chip superior en paralelo con su terminal duplicado para señales de conexión común.

12. Método según cualquiera de las reivindicaciones 1 u 11, en el que la etapa de creación de los orificios de vías pasantes de terminales y de chips comprende crear un segundo orificio de vía pasante de chips y pasante de terminales para facilitar la conexión entre un terminal para señales de salida del chip superior en serie con su terminal respectivo para señales de entrada del chip inferior.

13. Método según cualquiera de las reivindicaciones 1, 11 o 12, que comprende además: depositar una capa de aislamiento encima del par apilado de chips de circuito integrado;

formar orificios de contacto en la capa de aislamiento para permitir la conexión entre ciertos terminales para señales, adyacentes, cuando posteriormente se coloca encima otro chip;

depositar un conductor en los orificios de contacto;

aplicar por ataque químico una capa conductora para eliminar material conductor en exceso de las partes que están fuera de los orificios de contacto; y

fijar dos chips previamente combinados encima del par apilado de chips de circuito Integrado para crear un circuito multichip para un conjunto encapsulado multlchlp, siendo los dos chips previamente combinados sustancialmente idénticos al par apilado de chips de circuito integrado.

14. Método según cualquiera de las reivindicaciones 1 a 13, que comprende además:

proporcionar un controlador de memorias para controlar el acceso a la pluralidad de chips sustanclalmente idénticos;

conectar unos terminales para señales de entrada del chip superior a un lado de salida del controlador; y conectar unos terminales para señales de salida desde el chip Inferior a un lado de entrada del controlador.

Patentes similares o relacionadas:

Condensador de sustrato de encapsulado incrustado, del 19 de Febrero de 2020, de QUALCOMM INCORPORATED: Un sustrato de encapsulado , que comprende: un sustrato que comprende un primer lado; un condensador incrustado en […]

Circuito de terminación para terminación en troquel, del 6 de Noviembre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un circuito de terminación para proporcionar terminación en troquel para un terminal de undispositivo semiconductor , en […]

Revestimientos antideslustre que intensifican la unión, del 2 de Octubre de 2013, de GBC METALS, LLC: Un procedimiento para mejorar la adherencia de un objeto de cobre o aleación de cobre a un polímero,procedimiento que comprende aplicar un […]

Revestimientos antideslustre que intensifican la unión, del 2 de Octubre de 2013, de GBC METALS, LLC: Un procedimiento para mejorar la adherencia de un objeto de cobre o aleación de cobre a un polímero,procedimiento que comprende aplicar un […]

Procedimiento para la fabricación de un soporte de conexión, del 27 de Junio de 2012, de SUMITOMO METAL MINING COMPANY LIMITED: Procedimiento para fabricar un soporte de conexión, comprendiendo dicho procedimiento las etapas de: preparar una placa metálica para formar un soporte […]

Procedimiento para la fabricación de un soporte de conexión, del 27 de Junio de 2012, de SUMITOMO METAL MINING COMPANY LIMITED: Procedimiento para fabricar un soporte de conexión, comprendiendo dicho procedimiento las etapas de: preparar una placa metálica para formar un soporte […]

PROCEDIMIENTO Y DISPOSITIVO PARA RECUBRIR DE MANERA ESPECIALMENTE NO HOMOGENEA UN CUERPO EN FORMA DE PANAL., del 1 de Mayo de 2007, de LAMBERTI S.P.A.: Procedimiento para recubrir un cuerpo de soporte, especialmente un cuerpo en forma de panal por el que puede circular un fluido, con un material de recubrimiento, que […]

DISPOSICION DE CLAVIJAS DE ALIMENTACION PARA UN CIRCUITO INTEGRADO., del 16 de Junio de 2004, de N.V. PHILIPS' GLOEILAMPENFABRIEKEN: UN C.I. ESTA PROVISTO CON PUNTAS DE ALIMENTACION, QUE SE EXTIENDEN POR ENCIMA DE LA CAPSULA DEL "CHIP". LA LOCALIZACION DE LAS PUNTAS DE ALIMENTACION […]

ENSAMBLAJES DE CHIP SEMICONDUCTOR, PROCEDIMIENTO DE FABRICACION Y COMPONENTES PARA LOS MISMOS., del 16 de Mayo de 2002, de TESSERA, INC.: CONJUNTOS DE CHIPS SEMICONDUCTORES QUE INCORPORAN ELEMENTOS LAMINARES FLEXIBLES QUE TIENEN TERMINALES POR ENCIMA DE LA CARA FRONTAL O POSTERIOR DEL CHIP […]

CIRCUITO INTEGRADO CON MATRIZ DE CONEXION ANALOGICA., del 1 de Noviembre de 2006, de BAOLAB MICROSYSTEMS S.L.: Circuito integrado con matriz de conexión analógica. El circuito integrado comprende una matriz de conexión analógica que presenta una pluralidad de contactos analógicos […]