Dispositivo de recuperación de datos de reloj.

Un dispositivo (1) de recuperación de reloj / datos para recuperar una señal de reloj y datos,

en base a una señal digital de entrada, que comprende:

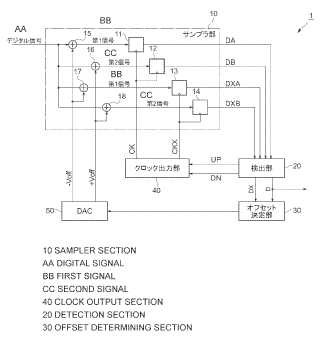

un muestreador (10) para recibir una entrada de una señal CK de reloj y una señal CKX de reloj, que tienen el mismo ciclo T, y también recibir una entrada de la señal digital;

proporcionar una primera señal aplicando un desfase, -Voff, a la señal digital, proporcionar una segunda señal aplicando un desfase, +Voff, a la señal digital, y, en cada n-ésimo periodo T(n) de este ciclo, muestrear, retener y emitir un valor digital DA(n) de la primera señal y un valor digital DB(n) de la segunda señal, en un momento tC indicado por la señal CK de reloj, y muestrear, retener y emitir un valor digital DXA(n) de la primera señal y un valor digital DXB(n) de la segunda señal en un momento tX indicado por la señal CKX de reloj, donde tC< tX y n es un entero; un detector (20) para recibir, en cada periodo T(n), una entrada del valor DA(n), el valor DB(n), el valor DXA(n) y el valor DXB(n), emitidos desde el muestreador (10), determinar un valor D(n) y un valor DX(n-1) fijando D(n) ≥ DA(n) y DX(n-1) ≥ DXA(n-1) en un caso en que un valor D(n-1) es de nivel ALTO, y fijando D(n) ≥ DB(n) y DX(n-1) ≥ DXB(n-1) en un caso en que el valor D(n-1) es de nivel BAJO, y detectar una relación de fase entre la señal CK de reloj y la señal digital, en base al valor D(n-1), el valor DX(n-1) y el valor D(n);

una parte (30) de determinación de desfase para recibir, en cada periodo T(n), una entrada del valor D(n) y el valor DX(n), determinados por el detector (20), y ajustar una magnitud del desfase, +Voff, sumada en el muestreador (10), de modo que un momento indicado por la señal CKX de reloj constituya el centro de una distribución de tiempos de transición de un valor de la primera señal, en un caso en que el valor D(n-1) sea de nivel ALTO, y un momento indicado por la señal CKX de reloj constituya el centro de una distribución de tiempos de transición de un valor de la segunda señal, en un caso en que el valor D(n-1) es de nivel BAJO; y

una parte (40) de salida de reloj para ajustar bien el ciclo T de la señal CK de reloj o bien la fase de la señal CK de reloj, en base a la relación de fase detectada por el detector (20), de modo que una diferencia de fase entre la señal CK de reloj y la señal digital disminuya, y emitir al muestreador la señal CK de reloj y la señal CKX de reloj que satisfacen la relación tX - tC ≥ T / 2.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/JP2007/067400.

Solicitante: Thine Electronics, Inc.

Nacionalidad solicitante: Japón.

Dirección: 9-1 Kanda-mitoshiro-cho, Chiyoda-ku, Tokyo 101-0053 JAPON.

Inventor/es: OZAWA,SEIICHI.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03L7/08 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › Detalles del bucle cerrado en fase.

- H03L7/081 H03L 7/00 […] › con un desfasador controlado adicional.

- H04L25/03 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 25/00 Sistemas de banda base. › Redes de formación para emisor o receptor, p. ej. redes de formación adaptables.

- H04L7/02 H04L […] › H04L 7/00 Disposiciones para sincronizar el receptor con el emisor. › Control de velocidad o de fase por medio de las señales de código recibidas, no conteniendo las señales ninguna información de sincronización especial.

PDF original: ES-2394282_T3.pdf

Fragmento de la descripción:

Dispositivo de recuperación de datos de reloj

Campo técnico La presente invención se refiere a un dispositivo para recuperar una señal de reloj y datos, en base a una señal digital de entrada.

Técnica de antecedente La onda de una señal digital emitida desde un transmisor se degrada mientras está siendo transmitida desde el transmisor a un receptor mediante un canal de transmisión, al requerir que la señal de reloj y los datos sean recuperados en el receptor. Dispositivos de recuperación de reloj / datos para llevar a cabo esta clase de recuperación, por ejemplo,

se revelan en los Documentos 1, 2 de Patente.

Los dispositivos revelados en estos documentos tienen en cuenta el hecho de que los tiempos de transición de datos fluctúan en la señal digital degradada en onda, y detectan cada bit de datos en tres temporizaciones. De las tres temporizaciones cuando se detecta cada bit de datos en este momento, una primera temporización se fija con proximidad al tiempo de inicio del periodo de estabilidad de datos del bit relevante, una segunda temporización se fija con proximidad al tiempo final del periodo de estabilidad de datos del bit relevante, y una tercera temporización se fija en un momento medio entre la primera temporización y la segunda temporización.

Luego, el dispositivo revelado en el Documento 1 de Patente recupera la señal de reloj ajustando las respectivas temporizaciones de modo que todos los datos detectados en las tres temporizaciones para cada bit coincidan, y recupera los datos en este momento detectando los datos de cada bit en la tercera temporización media.

Por el contrario, el dispositivo revelado en el Documento 2 de Patente recupera la señal de reloj ajustando cada temporización de modo que las tasas de errores de bits para cada una entre la primera temporización y la segunda temporización (es decir, las tasas en que los datos detectados en cada una de estas temporizaciones difieren de los datos detectados en la tercera temporización media) sean equivalentes entre sí y, además, estén dentro de la gama de configuración inicial, y recupera datos detectando los datos de cada bit en este momento, en la tercera temporización media.

El Documento 3 de Patente revela un circuito de recuperación de datos de reloj que tiene en cuenta las fluctuaciones en la transición de datos en base a muestras extremas y a la referencia a una pluralidad de patrones de muestra predeterminados.

[Documento 1 de Patente] Solicitud de Acceso Público de Patente Japonesa Nº H7-221800

[Documento 2 de Patente] Publicación Nacional de Versión Traducida Nº 2004-507963

[Documento 3 de Patente] Publicación de Solicitud de Patente Europea Nº EP 1 626 547 A2

Divulgación de la invención Problema que ha de resolver la invención Ahora, pues, el tiempo de transición de datos de una señal digital de entrada fluctúa como resultado de la arritmia del reloj transmisor, que es causada por fluctuaciones en el voltaje de la fuente de alimentación y otros ruidos de ese tipo en el transmisor que envió la señal digital, y también fluctúa debido a la interferencia entre símbolos causada por la mezcla de patrones de datos irregulares en la señal digital con la atenuación en el canal de transmisión. Hay casos en los cuales los dispositivos de la técnica antigua, previamente mencionados, pueden no ser capaces de recuperar la señal de reloj y los datos cuando la arritmia del reloj transmisor y la interferencia entre símbolos son altas.

Un objeto de la presente invención, que fue concebida para resolver los problemas anteriormente mencionados, es proporcionar un dispositivo de recuperación de reloj / datos que haga posible recuperar establemente una señal de reloj y datos incluso cuando la arritmia del reloj transmisor y la interferencia entre símbolos son altas.

Medios para resolver el problema Un dispositivo de recuperación de reloj / datos relacionado con la presente invención es para recuperar una señal de reloj y datos, en base a una señal digital de entrada, y comprende un muestreador, un detector, una parte de determinación de desfase y una parte de salida de reloj.

El muestreador recibe una entrada de una señal CK de reloj y una señal CKX de reloj, que tienen el mismo ciclo T, y también recibe una entrada de la señal digital, proporciona una primera señal aplicando un desfase (-Voff) a la señal digital, proporciona una segunda señal aplicando un desfase (+Voff) a la señal digital y, en cada n-ésimo periodo T (n) de este ciclo, muestrea, retiene y emite un valor digital DA (n) de la primera señal y un valor digital DB (n) de la segunda señal en un momento tC indicado por la señal CK de reloj, y muestra, retiene y emite un valor digital DXA (n) de la primera señal

y un valor digital DXB (n) de la segunda señal en un momento tX indicado por la señal CKX de reloj. Aquí, “tC < tX” y n es un entero.

El detector, en cada periodo T (n) , recibe una entrada del valor DA (n) , el valor DB (n) , el valor DXA (n) y el valor DXB (n) emitidos desde el muestreador, determina un valor D (n) y un valor DX (n-1) fijando “D (n) = DA (n) ” y “DX (n-1) = DXA (n-1) ”,

en un caso donde un valor D (n-1) es de nivel ALTO, y fijando “D (n) = DB (n) ” y “DX (n-1) = DXB (n-1) ” en un caso donde un valor D (n-1) es de nivel BAJO, y detecta una relación de fase entre la señal CK de reloj y la señal digital en base al valor D (n-1) , el valor DX (n-1) y el valor D (n) .

La parte de determinación de desfase, en cada periodo T (n) , recibe una entrada del valor D (n) y del valor DX (n)

determinados por el detector, y ajusta una magnitud del desfase (+Voff) sumada en el muestreador, de modo que un momento indicado por la señal CKX de reloj constituya el centro de una distribución de tiempos de transición de un valor de la primera señal en un caso donde el valor D (n-1) es de nivel ALTO, y un momento indicado por la señal CKX de reloj constituya el centro de una distribución de tiempos de transmisión de un valor de la segunda señal en un caso donde el valor D (n-1) es de nivel BAJO.

La parte de salida del reloj ajusta bien el ciclo T de la señal CK de reloj, o bien la fase de la señal CK de reloj, en base a la relación de fase detectada por el detector, de modo que una diferencia de fase entre la señal CK de reloj y la señal digital se reduzca, y emite al muestreador la señal CK de reloj y la señal CKX de reloj que satisfacen la relación “tX – tC = T/2”.

El dispositivo de recuperación de reloj / datos referido a la presente invención, que está configurado de esta manera, tiene un primer bucle que comprende el muestreador, el detector y la parte de salida de reloj, y también tiene un segundo bucle que comprende el muestreador, el detector y la parte de determinación de desfase. Con el procesamiento de estos dos bucles, las respectivas fases de la señal CK de reloj y la señal CKX de reloj se ajustan para coincidir con la fase de la señal digital de entrada. Además, la magnitud de un desfase (+Voff) sumada en el muestreador se ajusta a fin de coincidir con el momento máximo de la distribución de tiempos de transición de la primera señal en un caso donde un valor D (n-1) es de nivel ALTO, y se ajusta a fin de coincidir con el momento máximo de la distribución de tiempos de transición de la segunda señal en un caso donde un valor D (n-1) es de nivel BAJO. Luego, una cualquiera entre la señal CK de reloj y la señal CKX de reloj es emitida como la señal de reloj recuperada. Además, los datos de series temporales de un valor digital D (n) se emiten como los datos recuperados.

El detector comprende, preferiblemente, un circuito de detección de relaciones de fase que emite, como una señal que representa la relación de fase, una señal UP que tiene un valor significativo cuando “D (n-1) ≠ DX (n-1 = D (n) ”, y una señal DN que tiene un valor significativo cuando “D (n-1) = DX (n-1) ≠ D (n) ”.

La parte de salida de reloj, preferiblemente, ajusta bien el ciclo T de la señal CK de reloj o bien la fase de la señal CK de reloj, en base a la señal UP y la señal DN, y emite la señal CK de reloj y la señal CKX de reloj.

La parte de determinación de desfase, preferiblemente, ajusta la magnitud del desfase +Voff sumada en el muestreador,

de modo que la diferencia entre un valor de 0, 5 y la razón (cntINTERIOR / cntBORDE) entre un valor cntINTERIOR de suma acumulativa de “{D (n) ^ D (n-1) } * {D (n-2) ^ DX (n-1) }” y un valor cntBORDE de suma acumulativa de “D (n) ^ D (n-1) ” no sea mayor que un valor de referencia.... [Seguir leyendo]

Reivindicaciones:

1. Un dispositivo (1) de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador (10) para recibir una entrada de una señal CK de reloj y una señal CKX de reloj, que tienen el mismo ciclo T, y también recibir una entrada de la señal digital; proporcionar una primera señal aplicando un desfase, -Voff, a la señal digital, proporcionar una segunda señal aplicando un desfase, +Voff, a la señal digital, y, en cada n-ésimo periodo T (n) de este ciclo, muestrear, retener y emitir un valor digital DA (n) de la primera señal y un valor digital DB (n) de la segunda señal, en un momento tC indicado por la señal CK de reloj, y muestrear, retener y emitir un valor digital DXA (n) de la primera señal y un valor digital DXB (n) de la segunda señal en un momento tX indicado por la señal CKX de reloj, donde tC < tX y n es un entero;

un detector (20) para recibir, en cada periodo T (n) , una entrada del valor DA (n) , el valor DB (n) , el valor DXA (n) y el valor

DXB (n) , emitidos desde el muestreador (10) , determinar un valor D (n) y un valor DX (n-1) fijando D (n) = DA (n) y DX (n-1) = DXA (n-1) en un caso en que un valor D (n-1) es de nivel ALTO, y fijando D (n) = DB (n) y DX (n-1) = DXB (n-1) en un caso en que el valor D (n-1) es de nivel BAJO, y detectar una relación de fase entre la señal CK de reloj y la señal digital, en base al valor D (n-1) , el valor DX (n-1) y el valor D (n) ;

una parte (30) de determinación de desfase para recibir, en cada periodo T (n) , una entrada del valor D (n) y el valor DX (n) , determinados por el detector (20) , y ajustar una magnitud del desfase, +Voff, sumada en el muestreador (10) , de modo que un momento indicado por la señal CKX de reloj constituya el centro de una distribución de tiempos de transición de un valor de la primera señal, en un caso en que el valor D (n-1) sea de nivel ALTO, y un momento indicado por la señal CKX de reloj constituya el centro de una distribución de tiempos de transición de un valor de la segunda señal, en un caso en que el valor D (n-1) es de nivel BAJO; y

una parte (40) de salida de reloj para ajustar bien el ciclo T de la señal CK de reloj o bien la fase de la señal CK de reloj, en base a la relación de fase detectada por el detector (20) , de modo que una diferencia de fase entre la señal CK de reloj y la señal digital disminuya, y emitir al muestreador la señal CK de reloj y la señal CKX de reloj que satisfacen la relación tX – tC= T / 2.

2. El dispositivo (1) de recuperación de reloj / datos según la Reivindicación 1, en el cual el detector (20) comprende un circuito (24) de detección de relaciones de fase, para emitir, como señales que representan la relación de fase, una señal UP que tiene un valor significativo cuando D (n-1) ≠ DX (n-1) = D (n) , y una señal DN que tiene un valor significativo cuando D (n-1) = DX (n-1) ≠ D (n) .

3. El dispositivo (1) de recuperación de reloj / datos según la Reivindicación 2, en el cual la parte (40) de salida de reloj ajusta bien el ciclo T de la señal CK de reloj o bien la fase de la señal CK de reloj, en base a la señal UP y la señal DN, y emite la señal CK de reloj y la señal CKX de reloj.

4. El dispositivo (1) de recuperación de reloj / datos según la Reivindicación 1, en el cual la parte (30) de determinación de desfase ajusta la magnitud del desfase +Voff sumada en el muestreador (10) , de modo que la diferencia entre un valor de 0, 5 y la razón cntINTERIOR / cntBORDE de un valor de suma acumulativa cntINTERIOR de {D (n) ^ D (n-1) } * {D (n-2) ^ DX (n-1) } y un valor de suma acumulativa cntBORDE de D (n) ^ D (n-1) no sea mayor que un valor de referencia.

5. El dispositivo (1) de recuperación de reloj / datos según la Reivindicación 2, en el cual, en cada periodo T (n) , solamente en un caso en que exista un periodo en el cual la señal UP y la señal DN, respectivamente, constituyan el valor significativo dentro de los últimos 10 periodos consecutivos, T (n-9) a T (n) , incluyendo este periodo, la parte (30) de determinación de desfase suma acumulativamente {D (n) ^ D (n-1) } * {D (n-2) ^ DX (n-1) } para determinar el valor de suma 50 acumulativa cntINTERIOR, y suma acumulativamente D (n) ^ D (n-1) para determinar el valor de suma acumulativa cntBORDE; y

ajusta la magnitud del desfase +Voff sumada en el muestreador (10) de modo que la diferencia entre el valor de 0, 5 y la razón cntINTERIOR / cntBORDE no sea mayor que un valor de referencia.

6. El dispositivo (1) de recuperación de reloj / datos según la Reivindicación 4 o la Reivindicación 5, en el cual la parte (30) de determinación de desfase corrige la magnitud de desfase sumada de acuerdo a un valor D (n-2) en cada periodo T (n) .

Patentes similares o relacionadas:

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Información de control en un sistema de comunicación inalámbrica, del 15 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para enviar datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar conformación de haces […]

Asignación dinámica de recursos ACK en un sistema de comunicación inalámbrica, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: recibir una asignación semipersistente para un recurso de acuse de recibo, ACK, para un equipo de usuario, […]

Asignación dinámica de recursos ack en un sistema de comunicación inalámbrica, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: recibir una asignación semipersistente para un equipo de usuario, UE, siendo válida […]

Señal de sincronización extendida para la detección de índice de símbolos, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento de comunicación inalámbrica, que comprende: determinar una primera secuencia de señal de sincronización extendida, […]

Método y dispositivo para cuantificar y retroalimentar la información de canal y precodificar datos, del 8 de Abril de 2020, de ZTE CORPORATION: Un método para cuantificar y retroalimentar la información de canal en un sistema polarizado doble, caracterizado porque comprende: recibir una señal piloto de […]

Transmisor con equilibrio de polarización, del 1 de Abril de 2020, de Tianma Micro-Electronics Co., Ltd: Un transmisor que comprende: un generador de datos de señalización L1 (Capa 1), configurado para generar datos de señalización […]

Procedimiento y aparato para la conformación de haces de información de control en un sistema de comunicación inalámbrica, del 25 de Marzo de 2020, de QUALCOMM INCORPORATED: Un procedimiento de envío datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar […]