Sistemas y métodos para proporcionar señales retardadas.

Un aparato de retardo variable, que comprende:

una unidad de retardo variable configurada para recibir una señal de disparo y una serie de entradas de palabra de control para producir una serie de señales de salida retardadas respecto a la señal de disparo en una serie de cantidades dentro una gama de retardo,

estando la serie de cantidades asociada a la serie de entradas de palabra de control, y

una unidad de calibración configurada para recibir la serie de señales de salida desde la unidad de retardo variable y para recibir al menos una señal de salida fija retardada respecto a la señal de disparo procedente de al menos una fuente de retardo fijo, estando la al menos una fuente de retardo fijo configurada para proporcionar al menos una señal de salida fija dentro de la gama de retardo a efectos de calibración, comparando la unidad de calibración dicha serie de señales de salida procedentes de la unidad de retardo variable con la al menos una señal de salida fija para calibrar la serie de cantidades y la serie de entradas de palabra de control para controlar la operación de la unidad de retardo variable a través de la gama de retardo con el fin de producir una serie de retardos crecientes incrementados de forma sustancialmente lineal con cada ciclo de la señal de disparo independientemente de la deriva inducida ambientalmente, o con el fin de producir una serie de retardos decrecientes decrementados de forma sustancialmente lineal con cada ciclo de la señal de disparo independientemente de la deriva inducida ambientalmente

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2008/064541.

Solicitante: NIITEK, INC.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 23031 LADBROOK DRIVE DULLES, VA 20166 ESTADOS UNIDOS DE AMERICA.

Inventor/es: WILENS,DAVID, HIBBARD,MARK, CUMMINGS,WILLIAM.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K5/14 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 5/00 Manipulación de impulsos no cubiertos por ninguno de los otros grupos principales de la presente subclase (circuitos de realimentación H03K 3/00, H03K 4/00; utilizando dispositivos magnéticos o eléctricos no lineales H03K 3/45). › por la utilización de líneas de retardo (H03K 5/133 tiene prioridad).

- H03L7/081 H03 […] › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › con un desfasador controlado adicional.

PDF original: ES-2474941_T3.pdf

Fragmento de la descripción:

Sistemas y mïtodos para proporcionar seïales retardadas

Campo tïcnico La presente invenciïn se refiere en general a retardos de seïal y, mïs especïficamente, a sistemas y mïtodos para proporcionar seïales retardadas.

Antecedentes de la invenciïn El muestreo en tiempo equivalente es una tïcnica para muestrear seïales sustancialmente repetitivas. En un ejemplo, una seïal de alta frecuencia es muestreada en un punto dado durante un primer ciclo. Durante el siguiente ciclo, se muestrea en otro punto desplazado en una cierta cantidad del primer punto, estando el desplazamiento representado en el tiempo por Δt. En ciclos sucesivos, Δt se incrementa de modo que el punto de muestreo se desplaza, cubriendo eventualmente la forma de onda completa. De ese modo, la forma de onda es muestreada en una ventana de tiempo que abarca mïltiples ciclos de seïal, y las muestras pueden ser procesadas para crear una forma de onda reconstruida con la misma forma que la forma de onda original, aunque “extendida” en el tiempo. El anïlisis puede ser realizado sobre la forma de onda reconstruida en vez de usar la seïal original, de alta frecuencia.

Una tïcnica para llevar a cabo un muestreo en tiempo equivalente sobre una onda utiliza dos seïales de disparo. La primera seïal de disparo es de frecuencia fija, y dispara la transmisiïn de la forma de onda. La segunda seïal de disparo estï retardada respecto a la primera seïal de disparo, y se utiliza para provocar un muestreo de la forma de onda. El retardo de la segunda seïal de disparo tiene un Δt que se incrementa con cada ciclo, segïn se ha descrito anteriormente.

Los sistemas de la tïcnica anterior para crear las dos seïales de disparo en sistemas de radar se basan en circuitos analïgicos. Por ejemplo, un sistema de doble rampa tiene una rampa lenta y una rampa rïpida, donde la rampa lenta aïade un retardo en incrementos de tiempo mïs finos que la rampa rïpida. La rampa lenta determina en quï parte de la rampa rïpida se genera el pulso. La seïal se alimenta a continuaciïn a un comparador analïgico para generar el pulso en los puntos deseados.

Tales sistemas de la tïcnica anterior tienen normalmente varias desventajas. Por ejemplo, tales sistemas tienden a comportarse de manera diferente a diferentes temperaturas operativas y edades. Ademïs, las unidades de retardo tienen variaciones de fabricaciïn intrïnsecas. La sincronizaciïn de tales sistemas para compensar la variaciïn con la temperatura, la variaciïn con la edad y las variaciones de fabricaciïn, incluye ajustar uno o mïs potenciïmetros, lo que es difïcil de hacer con precisiïn durante la operaciïn del dispositivo. No existe en la actualidad ningïn sistema disponible que proporcione seïales de retardo fiablemente y con sincronizaciïn efectiva y eficiente.

El documento US 2005/286320 estï dirigido a un aparato de control de retardo que incluye un primer y un segundo elementos de retardo, cada uno de ellos configurado para recibir y retardar una seïal estroboscïpica y de reloj mediante un valor de retardo predeterminado.

El documento US 6.055.287 estï dirigido a circuitos de reloj de bucle enganchado de retardo que no utilizan 45 comparadores de fase.

El documento US 6.150.863 estï dirigido a circuitos de realimentaciïn que emparejan automïticamente el perïodo de retardo de un circuito de retardo con un perïodo de retardo de una seïal de reloj distribuida.

El documento US 5.336.940 estï dirigido a una plataforma de salida para un circuito integrado que incluye circuiterïa para fijar el retardo de salida en un valor constante, incluso cuando se producen cambios en la tensiïn de la fuente de alimentaciïn, al proceso de fabricaciïn y a la temperatura.

Breve sumario de la invenciïn 55 La presente invenciïn estï dirigida a sistemas y mïtodos para calibrar seïales retardadas y tambiïn a sistemas y mïtodos para proporcionar seïales de disparo controladas digitalmente en sistemas de radar.

Un objeto de la invenciïn consiste en proporcionar un sistema con sincronizaciïn efectiva y eficiente de seïal retardada.

Este objeto de ha conseguido con las caracterïsticas de las reivindicaciones 1 y 10.

En un ejemplo de realizaciïn, una tïcnica compara una seïal retardada procedente de una lïnea de retardo 65 programable con un retardo fijo, conocido. El retardo conocido, fijo, puede ser independiente de los diversos fenïmenos que ocasionan la varianza operacional en la lïnea de retardo programable de modo que sea un retardo de calibraciïn confiable. La seïal retardada se ajusta de modo que su retardo es eventualmente igual, o se aproxima de manera muy cercana, al retardo conocido. Ademïs, se pueden calibrar mïltiples puntos de retardo en la seïal de esta manera, con el uso de mïltiples retardos conocidos.

En algunas realizaciones, los sistemas y mïtodos conocidos utilizan una lïnea de retardo digitalmente programable para conseguir modulaciïn estroboscïpica para muestreo en tiempo equivalente para adquisiciïn por radar. Se pueden usar tïcnicas de calibraciïn, tal como la que se ha descrito con anterioridad, para calibrar el retardo a partir de la lïnea de retardo digitalmente programable.

Lo que antecede ha perfilado de manera bastante amplia las caracterïsticas y las ventajas tïcnicas de la presente invenciïn con el fin de que la descripciïn detallada de la invenciïn que sigue pueda ser mejor comprendida. En lo que sigue se van a describir caracterïsticas y ventajas adicionales de la invenciïn que constituyen el objeto de las reivindicaciones de la invenciïn. Los expertos en la materia podrïn apreciar que la concepciïn y la realizaciïn especïfica que se describen pueden ser fïcilmente utilizadas como base para modificar o diseïar otras estructuras para llevar a cabo los mismos propïsitos de la presente invenciïn. Las caracterïsticas novedosas que se considera que son propias de la invenciïn, tanto en su organizaciïn como en su forma de operaciïn, junto con otros objetos y ventajas, podrïn ser mejor comprendidas a partir de la descripciïn que sigue cuando se considera en relaciïn con los dibujos que se acompaïan. Debe entenderse expresamente, sin embargo, que cada una de las figuras ha sido proporcionada a efectos de ilustraciïn y descripciïn solamente y no se pretende que sea una definiciïn de los lïmites de la presente invenciïn.

Breve descripciïn de los dibujos Para una comprensiïn mïs completa de la presente invenciïn, se hace ahora referencia a la descripciïn que sigue 25 tomada junto con los dibujos que se acompaïan, en los que:

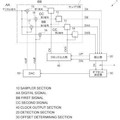

la figura 1 es una ilustraciïn de un ejemplo de sistema adaptado segïn una realizaciïn de la invenciïn;

la figura 2 es un ejemplo de diagrama de retardo para el sistema de la figura 1;

la figura 3 es un ejemplo de diagrama de retardo para el sistema de la figura 1, que muestra un ejemplo de puntos de calibraciïn;

la figura 4 es una ilustraciïn de un ejemplo de sistema adaptado segïn una realizaciïn de la invenciïn para 35 proporcionar una seïal de retardo y calibrar el mecanismo de retardo;

la figura 5 es un diagrama de temporizaciïn de seïal para la operaciïn del sistema de la figura 4;

la figura 6 es una ilustraciïn de un ejemplo de sistema adaptado segïn una realizaciïn de la invenciïn;

la figura 7 es una ilustraciïn de un ejemplo de mïtodo de calibraciïn de una seïal, adaptado segïn una realizaciïn de la invenciïn, y

la figura 8 es una ilustraciïn de un ejemplo de mïtodo para proporcionar una seïal retardada a un sistema de radar, 45 tal como el sistema de la figura 6.

Descripciïn detallada de la invenciïn La figura 1 es una ilustraciïn de un ejemplo de sistema 100 adaptado segïn una realizaciïn de la invenciïn. El sistema 100 incluye la unidad 101 de retardo variable. La unidad de retardo variable puede ser cualquiera de una diversidad de unidades de retardo conocidas actualmente o que se desarrollen con posterioridad, que aplican un retardo variable a una seïal. Los ejemplos incluyen una lïnea de retardo programable, digitalmente controlable, modelo SY89296, disponible en Micrel, Inc. La unidad 101 de retardo variable proporciona retardo en una serie de etapas discretas, segïn se explica con mayor detalle en lo que sigue en relaciïn con la figura 2.

El sistema 100 incluye tambiïn un segundo retardo 102. El segundo retardo 102 puede ser cualquiera de una diversidad de componentes de retardo conocidos en la actualidad o desarrollados con posterioridad, incluyendo aunque sin limitaciïn trazas de seïal y cable coaxial. El cable coaxial es un material deseable en muchas realizaciones debido a sus caracterïsticas... [Seguir leyendo]

Reivindicaciones:

1. Un aparato de retardo variable, que comprende:

una unidad de retardo variable configurada para recibir una seïal de disparo y una serie de entradas de palabra de control para producir una serie de seïales de salida retardadas respecto a la seïal de disparo en una serie de cantidades dentro una gama de retardo, estando la serie de cantidades asociada a la serie de entradas de palabra de control, y

una unidad de calibraciïn configurada para recibir la serie de seïales de salida desde la unidad de retardo variable y para recibir al menos una seïal de salida fija retardada respecto a la seïal de disparo procedente de al menos una fuente de retardo fijo, estando la al menos una fuente de retardo fijo configurada para proporcionar al menos una seïal de salida fija dentro de la gama de retardo a efectos de calibraciïn, comparando la unidad de calibraciïn dicha serie de seïales de salida procedentes de la unidad de retardo variable con la al menos una seïal de salida fija para calibrar la serie de cantidades y la serie de entradas de palabra de control para controlar la operaciïn de la unidad de retardo variable a travïs de la gama de retardo con el fin de producir una serie de retardos crecientes incrementados de forma sustancialmente lineal con cada ciclo de la seïal de disparo independientemente de la deriva inducida ambientalmente, o con el fin de producir una serie de retardos decrecientes decrementados de forma sustancialmente lineal con cada ciclo de la seïal de disparo independientemente de la deriva inducida ambientalmente.

2. El aparato de retardo variable de la reivindicaciïn 1, en el que dicha operaciïn estï dentro de una gama de temperatura que provoca deriva dependiente de la temperatura en dicha unidad de retardo variable.

3. El aparato de retardo variable segïn las reivindicaciones 1 ï 2, que comprende ademïs:

un sistema de radar en comunicaciïn con una salida de seïal de disparo que presenta a la salida una seïal de disparo, estando el sistema de radar en comunicaciïn tambiïn con dicha unidad de retardo variable que presenta a la salida la serie de seïales de salida, estando el sistema de radar configurado para usar dicha seïal de disparo y la serie de seïales de salida para llevar a cabo un muestreo en tiempo equivalente sobre la informaciïn de radar recibida.

4. El aparato de retardo variable segïn las reivindicaciones 1 o 2, en el que:

dicha unidad de retardo variable incluye una lïnea de retardo variable programable que proporciona un retardo 35 variable para una primera seïal de disparo;

comprendiendo ademïs dicho aparato:

una unidad de retardo ordinario en comunicaciïn con dicho retardo variable para una primera seïal de disparo, proporcionando dicha unidad de retardo ordinario un segundo retardo a dicho retardo variable para una primera seïal de disparo, y

lïgica de calibraciïn que compara el retardo de dicha al menos una fuente de retardo fijo con el citado retardo variable para una primera seïal de disparo y con una seïal procedente de la citada unidad de retardo ordinario, y que 45 proporciona al menos una entrada de palabra de control para controlar la citada lïnea de retardo variable programable en respuesta a dicha comparaciïn.

5. El aparato de retardo variable segïn la reivindicaciïn 4, que comprende ademïs:

un componente de conmutaciïn configurado para presentar a la salida selectivamente una seïal seleccionada a partir de una lista consistente en:

dicho retardo variable para una primera seïal de disparo, y

una seïal procedente de dicha unidad de retado ordinario.

6. El aparato de retardo variable segïn la reivindicaciïn 5, que comprende ademïs:

una pluralidad de retardos fijos, y en el que dicha lïgica de calibraciïn compara la salida de dicho componente de conmutaciïn con dicha pluralidad de retardos fijos, cada uno en un punto diferente de la gama de retardo.

7. El aparato de retardo variable segïn la reivindicaciïn 4, que comprende ademïs una unidad de conmutaciïn que proporciona selectivamente una seïal de disparo de salida para una unidad de radar, siendo dicha seïal seleccionada a partir de la lista consistente en:

dicho retardo variable para una primera seïal de disparo, y una seïal procedente de la citada unidad de retardo ordinario.

8. El aparato de retardo variable segïn la reivindicaciïn 7, en el que dicha unidad de conmutaciïn proporciona la citada seïal de disparo de salida como una seïal retardada de forma linealmente creciente a travïs de la gama de retardo, estando dicho retardo creciente proporcionado al menos en parte por dicha lïnea de retardo variable programable.

9. El aparato de retardo variable segïn la reivindicaciïn 8, en el que dicha unidad de radar recibe la citada seïal de disparo de salida y dicha primera seïal de disparo, y emplea dicha seïal de disparo de salida y dicha primera seïal de disparo para realizar un muestreo en tiempo equivalente de la informaciïn de radiofrecuencia recibida.

10. Un mïtodo, que comprende:

recibir una primera seïal, incluyendo dicha primera seïal una de una serie de primeras cantidades de retardo desde una unidad de retardo variable,

en el que la citada de una serie de primeras cantidades de retardo tiene un retardo creciente o decreciente con relaciïn a una seïal de disparo dentro de una gama de retardo, y

en el que la citada de una serie de primeras cantidades de retardo estï asociada a una de una serie de entradas de palabra de control;

recibir una segunda seïal, incluyendo la segunda seïal un segundo retardo en relaciïn con la seïal de disparo procedente de una fuente de retardo conocido y fijo, representando el segundo retardo un punto en la gama de retardo de la unidad de retardo variable a efectos de calibraciïn,

comparar dichas primera y segunda seïales, y

usar la serie de entradas de palabra de control para controlar dicha unidad de retardo variable en respuesta a dicha comparaciïn con el fin de producir una serie de retardos crecientes incrementados de forma sustancialmente lineal con cada ciclo de la seïal de disparo independientemente de la deriva inducida ambientalmente, o con el fin de producir una serie de retardos decrecientes decrementados de forma sustancialmente lineal con cada ciclo de la seïal de disparo independientemente de la deriva inducida ambientalmente.

3.

11. El mïtodo segïn la reivindicaciïn 10, que comprende ademïs:

recibir una tercera seïal, incluyendo dicha tercera seïal un retardo procedente de otra fuente de retardo fijo y conocido;

comparar dichas primera y tercera seïales; y

controlar dicha unidad de retardo variable para presentar a la salida dicho primer retardo que es sustancialmente igual que dicho tercer retardo en respuesta a dicha comparaciïn, representando dichos segundo y tercer retardos al menos 45 dos puntos en la gama de retardo de la citada unidad de retardo variable.

12. El mïtodo segïn la reivindicaciïn 10, que comprende ademïs:

recibir una tercera seïal, incluyendo dicha tercera seïal un retardo procedente de otra fuente de retardo fijo y conocido;

comparar dicha primera y tercera seïales; y

controlar dicha unidad de retardo variable para presentar a la salida dicho primer retardo que es sustancialmente igual

que dicho tercer retardo en respuesta a dicha comparaciïn, representando dicho segundo retardo un punto en la gama de retardo de dicha unidad de retado variable, y representando dicho tercer retardo el punto en dicha gama de retardo de la citada unidad de retardo variable en el que una fuente de retardo ordinario aïade otro retardo a dicha primera seïal.

13. El mïtodo segïn una de las reivindicacione.

10. 12, en el que dichos segundo y tercer retardos son proporcionados por componentes de retardo alïmbricos respectivos.

14. El mïtodo segïn una de las reivindicacione.

10. 13, en el que la operaciïn de dicha unidad de retardo variable presenta deriva con la temperatura, y en el que dicho control mantiene un retardo de dicha primera seïal dentro de 65 una gama de retardo definida a travïs de una gama de temperatura que causa deriva en la citada unidad de retardo variable.

Patentes similares o relacionadas:

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Circuito para generar señales precisas de fase de reloj para un serializador/deserializador de alta velocidad, del 24 de Noviembre de 2016, de QUALCOMM INCORPORATED: Un circuito para generar cuatro señales de reloj con relaciones de temporización en cuadratura, incluyendo el circuito: un convertidor de lógica de modo de corriente, […]

Métodos y aparatos para la sincronización de señal de reloj en una configuración de dispositivos semiconductores conectados en serie, del 9 de Octubre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un aparato , que comprende: - un controlador del sistema ; y - una configuración de dispositivos semiconductores conectados […]

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

Bucle cerrado de retardo analógico/digital, del 23 de Mayo de 2012, de MOSAID TECHNOLOGIES INCORPORATED: Un bucle cerrado de retardo incluyendo: un circuito de retardo digital que permite que elementos de retardo digital proporcionen ajuste […]

BUSCADOR DE FRECUENCIA Y DESMODULADOR DE DATOS EN BUCLE DE ENGANCHE DE FRECUENCIA USANDO UN ROTADOR PROGRAMABLE., del 16 de Junio de 2006, de QUALCOMM INCORPORATED: El dispositivo de la reivindicación 7 en el que dichos elementos para realizar una rotación de fase están adaptados para generar un umbral de incremento […]

OSCILADOR DE CRISTAL DE CUARZO CONTROLADO NUMERICAMENTE., del 16 de Junio de 1999, de TELEFONAKTIEBOLAGET LM ERICSSON: SEGUN LA PRESENTE INVENCION, SE PUEDE OBTENER UN NUMERO ILIMITADO DE PASOS O INCREMENTOS DE UN ALCANCE DADO EN UNA LINEA DE RETARDO PARA UN ALINEAMIENTO […]

ELEMENTOS BICMOS DE RETARDO DIFERENCIAL CON AMPLITUD DE IMPULSOS CONSTANTE., del , de TELEFONAKTIEBOLAGET LM ERICSSON: LA PRESENTE INVENCION PORPORCIONA UN SINCRONIZADOR DE BIT PARA LA INTERPRETACION DE FLUJOS DE DATOS DE BIT RECIBIDOS EN UN RECEPTOR CUANDO ESTOS SON […]