Almacenamiento de datos y estructuras apilables.

Un sistema (100) que comprende una pila incluyendo:

un primer dispositivo de memoria (200-1;

201);

un segundo dispositivo de memoria (200-2, 202);

opcionalmente, dispositivos de memoria adicionales (200-3; 200-4);

un controlador acoplado eléctricamente al primer dispositivo de memoria; donde

- cada uno de dichos dispositivos de memoria comprende contactos de entrada en serie (D0-D7, CSI, DSI) y contactos de salida en serie (Q0-7, CSO, DSO), los contactos de salida en serie estando separados de los contactos de entrada en serie y todos los dispositivos de memoria 15 teniendo una misma configuración de la disposición de entrada/salida,

- el segundo dispositivo de memoria en la pila se fija como un dispositivo de memoria sucesivo al primer dispositivo de memoria y rotacionalmente desplazado con respecto al primer dispositivo de memoria precedente en la pila para alinear los contactos de salida en serie (Q0-7, OSC, DSO) del 20 primer dispositivo de memoria con los contactos de entrada en serie correspondientes (D0-D7, CSI, DSI) del segundo dispositivo de memoria;

- cada dispositivo opcional adicional de memoria (200-3; 200-4; 202) en la pila, si lo hay, se fija como un dispositivo de memoria sucesivo a su respectivo dispositivo de memoria precedente en la pila y rotacionalmente desplazado con respecto a dicho dispositivo de memoria precedente para alinear los contactos de salida (Q0-7, OSC, DSO) de dicho dispositivo de memoria precedente con los contactos de entrada correspondientes (D0-D7, CSI, DSI) del dispositivo de memoria sucesivo;

- se proporciona un camino de acceso que facilita una configuración de conexión en serie a través del primer dispositivo de memoria y el segundo dispositivo de memoria y los dispositivos de memoria adicionales opcionales, si los hay, el camino de acceso adaptado para dar soporte a la transmisión de datos;

- el controlador está configurado para acceder a los datos desde cualquier uno particular de los dispositivos de memoria en la pila en base a un flujo de datos a lo largo del camino desde el dispositivo de memoria en particular, a través de dispositivos de memoria sucesivos en la pila, si los hay, hasta el controlador, en donde la conexión entre el último dispositivo de memoria sucesivo en la pila de nuevo al controlador permite al controlador recibir datos almacenados en el dispositivo de memoria particular en la pila;

- cada dispositivo de memoria en la pila puede ser ajustado a un modo de paso a través o un modo de acceso a memoria, el modo de paso permitiendo transmisión de datos recibida en una entrada en serie (D0-D7, CSI, DSI) de un dispositivo de memoria respectivo a lo largo del camino de acceso hasta una salida en serie (Q0-7, OSC, DSO) del dispositivo de memoria respectivo, y el modo de acceso a memoria permitiendo

i) recibir datos en el camino de acceso y almacenar los datos en los circuitos de memoria asociados con el dispositivo de memoria respectivo, y

ii) recuperar datos de los circuitos de la memoria para su transmisión por el camino hacia una salida del dispositivo de memoria respectivo.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/CA2008/002145.

Solicitante: MOSAID TECHNOLOGIES INCORPORATED.

Nacionalidad solicitante: Canadá.

Dirección: 11 Hines Road, Suite 203 Ottawa, ON K2K 2X1 CANADA.

Inventor/es: OH,HakJune, PYEON,HONG BEOM, KIM,JIN-KI.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C16/02 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 16/00 Memorias de sólo lectura programables y borrables (G11C 14/00 tiene prioridad). › programables eléctricamente.

- G11C5/02 G11C […] › G11C 5/00 Detalles de memorias cubiertos por el grupo G11C 11/00. › Disposición de elementos de almacenamiento, p. ej. bajo la forma de una matriz.

- G11C5/06 G11C 5/00 […] › Disposiciones para interconectar eléctricamente elementos de almacenamiento, p. ej. por cableado.

- G11C7/10 G11C […] › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

- H01L23/48 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › Disposiciones para conducir la corriente eléctrica hacia o desde el cuerpo de estado sólido durante su funcionamiento, p. ej. hilos de conexión o bornes.

- H01L23/52 H01L 23/00 […] › Disposiciones para conducir la corriente eléctrica en el interior del dispositivo durante su funcionamiento, de un componente a otro.

- H01L23/535 H01L 23/00 […] › que comprenden interconexiones internas, p. ej. estructuras de interconexión enterradas.

PDF original: ES-2439960_T3.pdf

Fragmento de la descripción:

Almacenamiento de datos y estructuras apilables Descripción ANTECEDENTES

La unión mediante hilo convencional (WB) es un procedimiento de hacer interconexiones con un chip semiconductor. Un cable de unión está hecho generalmente de uno de los siguientes materiales: oro, aluminio o cobre. Los diámetros de los cables suelen comenzar en alrededor de 15 micrómetros y pueden ser de hasta varios cientos de micrómetros para aplicaciones de alta potencia.

Hay dos clases principales de unión de conductores: unión mediante bola y unión mediante cuña.

La unión mediante bola generalmente se limita al uso del oro y cable de cobre, y requiere por lo general calor para hacer una unión respectiva. La unión mediante cuña puede utilizar ya sea oro o alambre de aluminio. Cuando se utiliza oro en la unión mediante cuña, se requiere calor para hacer un enlace respectivo.

En cualquiera de los tipos de unión mediante cables, el cable se une típicamente usando una combinación de calor, presión y energía ultrasónica para hacer una soldadura. La unión mediante cables se considera generalmente la tecnología más rentable y flexible de interconexión. La unión mediante cables se utiliza por lo tanto ampliamente para ensamblar la gran mayoría de los paquetes de semiconductores.

Los chips de memoria convencionales en un denominado sistema " Paquete Multi-Chip (MCP) " se interconectan a menudo usando un esquema de interconexión en paralelo. Este procedimiento de conexión "multipunto" incluye interconectar los chips de memoria de tal manera que los datos de información y direcciones y las señales de control están acoplados a los chips en una manera paralela usando buses de señal comunes. Por ejemplo, cada chip de memoria puede incluir varias entradas y salidas para dar cabida a una transferencia paralela de información de control, información de dirección y de datos a través de un conjunto interconectado de dispositivos de memoria. Los sistemas de este tipo son conocidos de US 2004/0232 559, Según la cual los chips sucesivos en una pila están desplazados rotacionalmente con respecto a la otra, y desde US 2006/0001176.

Se han desarrollado Paquetes-sobre-paquetes tridimensionales (PoPs) a en la industria de semiconductores de memoria en los esfuerzos para, por ejemplo, satisfacer la demanda de una mayor densidad de memoria y funcionalidad. De acuerdo con algunos desarrollos de ejemplo, un paquete-sobre-paquete tridimensional convencional se puede fabricar de la siguiente manera: Después de fabricar una oblea y separar la oblea en una pluralidad de chips individuales, un chip correspondiente puede estar unido y conectado eléctricamente a un sustrato. El chip puede encapsularse con una resina de moldeo para producir un paquete. El denominado paquetesobre-paquete puede ser creado mediante apilamiento de los paquetes. Estos paquete-sobre-paquete emplean un marco de plomo o un sustrato tal como, por ejemplo, una placa de cinta de circuito o una placa de circuito impreso. Se pueden emplear un procedimiento de interconexión tal como, por ejemplo, unión mediante hilo (BM) , unión automatizada mediante cinta (TAB) , o unión por inversión de chip, para establecer conexiones eléctricas entre el chip y el sustrato.

Desafortunadamente, los diferentes procedimientos conocidos de fabricación de PoPs requieren el uso de procesos de fabricación complejos. Por otra parte, estos PoPs son bastante grandes en comparación con un chip estándar, reduciendo de este modo la densidad de montaje en el aparato externo. Además, los PoPs pueden incluir tantos chips interconectados con caminos de transmisión de señal largos. Los caminos largos pueden, por ejemplo, causar retardos de la señal que se podría esperar que bajen el rendimiento del sistema.

Sin embargo, los apilamientos de chips de memoria en Paquetes Multi-Chip apilados de tres dimensiones (MCP) al nivel de oblea o de chip tienen la ventaja de tener estructuras simples, tamaños más pequeños y procesos de fabricación simples. Además, un paquete multi-chip al nivel de oblea puede evitar retardos de la señal.

Es posible clasificar los paquetes multi-chip en dos tipos. Uno de ellos es un paquete multi-chip formado mediante el apilamiento de diferentes tipos de chips, consiguiendo de esta manera multifuncionalidad. El otro es un paquete multi-chip formado por el apilamiento de los mismos tipos de chips, ampliando así la capacidad de memoria.

Una NAND de memoria flash es un tipo de memoria no volátil de uso generalizado como medio de almacenamiento para electrónica de consumo, como cámaras digitales y reproductores portátiles de música digital, por ejemplo, de uso común.

La densidad de un chip de memoria flash NAND actualmente disponible puede ser de hasta 32 Gbits (es decir, 4GBytes) , por lo que es adecuado para su uso en unidades USB Flash populares ya que el tamaño de un chip es pequeño. Sin embargo, la reciente demanda de dispositivos de electrónica de consumo con funciones de música y vídeo ha estimulado la demanda de ultra-alta capacidad para almacenar gran cantidad de datos, que no pueden ser satisfechas por el único chip de memoria flash NAND. Por lo tanto, se han interconectado entre sí varios chips de memoria flash NAND en un sistema de almacenamiento para aumentar la eficacia de la capacidad de almacenamiento disponible. En ciertos casos, pueden ser necesarias densidades de almacenamiento Flash de 250 GB o más para satisfacer las necesidades de almacenamiento de datos.

Breve descripción de los dibujos A continuación se hará referencia a modo de ejemplo a los dibujos adjuntos, de los cuales:

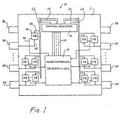

La Figura 1 es un diagrama de ejemplo de un sistema de memoria según realizaciones en este documento;

La Figura 2 es un diagrama de ejemplo de un dispositivo de memoria apilable y la correspondiente disposición de configuración de entrada/salida de acuerdo con las realizaciones en este documento;

La Figura 3 es un diagrama de ejemplo en 3 dimensiones de un sistema de memoria apilado según realizaciones en este documento;

La Figura 4 es un ejemplo de diagrama en sección transversal que ilustra un apilamiento de dispositivos de memoria interconectados según realizaciones en este documento;

La Figura 5 es un diagrama de ejemplo en 3 dimensiones de un sistema de memoria incluyendo múltiples dispositivos de memoria apilados según realizaciones en este documento;

La Figura 6 es un ejemplo de diagrama en sección transversal que ilustra un apilamiento de dispositivos de memoria interconectados según realizaciones en este documento;

La Figura 7 es un diagrama de ejemplo en 3 dimensiones de un sistema de memoria que incluye múltiples dispositivos de memoria apilados según realizaciones en este documento;

La Figura 8 es un ejemplo de diagrama en sección transversal que ilustra un apilamiento de dispositivos de memoria interconectados según realizaciones en este documento;

La Figura 9 es un diagrama de ejemplo en 3 dimensiones que ilustra una capa de conectividad según realizaciones en este documento;

La Figura 10 es un ejemplo de diagrama en sección transversal de una capa de conectividad según realizaciones en este documento;

La Figura 11 es un diagrama de ejemplo en 3 dimensiones que ilustra una capa de conectividad según realizaciones en este documento;

La Figura 12 es un diagrama de ejemplo en 3 dimensiones que ilustra una capa de conectividad según realizaciones en este documento;

La Figura 13 es un diagrama de ejemplo en 3 dimensiones de un dispositivo de memoria y la disposición de agujeros de paso y patillas de superficie según realizaciones en este documento;

La Figura 14 es un diagrama de ejemplo en 3 dimensiones que ilustra un apilamiento de dispositivos de memoria según realizaciones en este documento;

Las Figuras 15, 16, y 17 son ejemplos de diagramas de sección transversal que ilustran la conectividad asociada con una pila de dispositivos de memoria según realizaciones en este documento;

La Figura 18 es un diagrama de ejemplo que ilustra una disposición de configuración de múltiples entradas y múltiples salidas según realizaciones en este documento;

La Figura 19 es un diagrama de ejemplo en 3 dimensiones que ilustra un apilamiento de dispositivos de memoria y la conectividad correspondiente según realizaciones en este documento;

La Figura 20 es un ejemplo de diagrama en sección transversal que ilustra la conectividad en una disposición en capas de múltiples dispositivos de memoria según realizaciones en este documento; y

La Figura 21 es un ejemplo de diseño de configuración de un dispositivo de memoria apilable según realizaciones en este documento;... [Seguir leyendo]

Reivindicaciones:

1. Un sistema (100) que comprende una pila incluyendo:

un primer dispositivo de memoria (200-1; 201) ;

un segundo dispositivo de memoria (200-2, 202) ;

opcionalmente, dispositivos de memoria adicionales (200-3.

20. 4) ;

un controlador acoplado eléctricamente al primer dispositivo de memoria; donde

- cada uno de dichos dispositivos de memoria comprende contactos de entrada en serie (D0-D7, CSI, DSI) y contactos de salida en serie (Q0-7, CSO, DSO) , los contactos de salida en serie estando separados de los contactos de entrada en serie y todos los dispositivos de memoria teniendo una misma configuración de la disposición de entrada/salida,

- el segundo dispositivo de memoria en la pila se fija como un dispositivo de memoria sucesivo al primer dispositivo de memoria y rotacionalmente desplazado con respecto al primer dispositivo de memoria precedente en la pila para alinear los contactos de salida en serie (Q0-7, OSC, DSO) del primer dispositivo de memoria con los contactos de entrada en serie correspondientes (D0-D7, CSI, DSI) del segundo dispositivo de memoria;

- cada dispositivo opcional adicional de memoria (200-3.

20. 4; 202) en la pila, si lo hay, se fija como un dispositivo de memoria sucesivo a su respectivo dispositivo de memoria precedente en la pila y rotacionalmente desplazado con respecto a dicho dispositivo de memoria precedente para alinear los contactos de salida (Q0-7, OSC, DSO) de dicho dispositivo de memoria precedente con los contactos de entrada correspondientes (D0-D7, CSI, DSI) del dispositivo de memoria sucesivo;

- se proporciona un camino de acceso que facilita una configuración de conexión en serie a través del primer dispositivo de memoria y el segundo dispositivo de memoria y los dispositivos de memoria adicionales opcionales, si los hay, el camino de acceso adaptado para dar soporte a la transmisión de datos;

- el controlador está configurado para acceder a los datos desde cualquier uno particular de los dispositivos de memoria en la pila en base a un flujo de datos a lo largo del camino desde el dispositivo de memoria en particular, a través de dispositivos de memoria sucesivos en la pila, si los hay, hasta el controlador, en donde la conexión entre el último dispositivo de memoria sucesivo en la pila de nuevo al controlador permite al controlador recibir datos almacenados en el dispositivo de memoria particular en la pila;

- cada dispositivo de memoria en la pila puede ser ajustado a un modo de paso a través o un modo de acceso a memoria, el modo de paso permitiendo transmisión de datos recibida en una entrada en serie (D0-D7, CSI, DSI) de un dispositivo de memoria respectivo a lo largo del camino de acceso hasta una salida en serie (Q0-7, OSC, DSO) del dispositivo de memoria respectivo, y el modo de acceso a memoria permitiendo

i) recibir datos en el camino de acceso y almacenar los datos en los circuitos de memoria asociados con el dispositivo de memoria respectivo, y

ii) recuperar datos de los circuitos de la memoria para su transmisión por el camino hacia una salida del dispositivo de memoria respectivo.

2. El sistema según la reivindicación 1, en el que el desplazamiento de rotación de cada uno de los dispositivos de memoria (200-1 .

20. 3; 201) con respecto a su respectivo dispositivo de memoria sucesivo (200-2 a 2004; 202) en la pila, si lo hay, es sustancialmente 180 grados.

3. El sistema según la reivindicación 1, en el que cada uno de los segundos dispositivos de memoria (200-2; 202) y los dispositivos de memoria adicionales opcionales (200-3.

20. 4) , si los hay, está escalonado con respecto a su respectivo dispositivo de memoria precedente (200-1 .

20. 3; 201) en la pila para exponer salidas (201B) en un plano del respectivo dispositivo de memoria anterior para conectarlas eléctricamente a las entradas (202A) en un plano del respectivo dispositivo de memoria sucesivo (200-2 .

20. 4) .

4. El sistema según la reivindicación 1, en el que cada uno de los primeros dispositivos de memoria (200-1; 201) y el segundo dispositivo de memoria (200-2; 202) son de forma plana y tienen una parte superior e

inferior respectiva frente a frente, el primer dispositivo de memoria y el segundo dispositivo de memoria apilados uno encima del otro, en donde una parte inferior respectiva del segundo dispositivo de memoria está fijada a una parte superior del primer dispositivo de memoria de tal manera que la parte superior del primer dispositivo de memoria está orientada y la parte superior del segundo de dispositivo de memoria están orientados hacia una misma dirección a lo largo de la pila; y

en el que cada uno de los dispositivos de memoria adicionales (200-3.

20. 4) , si los hay, es de forma plana y tiene una parte superior e inferior respectiva frente a frente, el dispositivo de memoria adicional apilándose en la parte superior de un dispositivo de memoria precedente respectivo, en donde una parte inferior respectiva del dispositivo de memoria adicional se fija a una parte superior del dispositivo de memoria precedente de tal manera que la parte superior del dispositivo de memoria anterior y la parte superior del dispositivo de memoria adicional están orientados hacia una misma dirección a lo largo de la pila.

5. Un procedimiento que comprende:

recibir un primer dispositivo de memoria (200-1; 201) , un segundo dispositivo de memoria (200-2; 202) y, opcionalmente, recibir dispositivos de memoria adicionales (200-3.

20. 4) , en donde cada uno de dichos dispositivos de memoria comprende contactos de entrada en serie (D0-D7, CSI, DSI) y contactos de salida en serie (Q0-7, CSO, DSO) , los contactos de salida de serie siendo independientes de los contactos de entrada en serie, y todos los dispositivos de memoria teniendo una misma disposición de configuración de entrada/salida;

producir una pila de dispositivos de memoria en la que

- El segundo dispositivo de memoria en la pila se fija como un dispositivo de memoria sucesivo al primer dispositivo de memoria anterior y rotacionalmente desplazado con respecto al primer dispositivo de memoria en la pila para alinear las salidas de serie (Q0-7, OSC, DSO) del primer dispositivo de memoria con entradas en serie (D0-D7, CSI, DSI) del segundo dispositivo de memoria; y

- Cada dispositivo opcional adicional de memoria (200-3.

20. 4; 202) en la pila, si lo hay, se fija como un dispositivo de memoria sucesivo a su respectivo dispositivo de memoria precedente en la pila y rotacionalmente desplazado con respecto a dicho dispositivo de memoria precedente para alinear los contactos de salida (Q0-7, OSC, DSO) de dicho dispositivo de memoria precedente con los contactos de entrada correspondientes (D0-D7, CSI, DSI) del dispositivo de memoria sucesivo;

proporcionar una configuración de conexión en serie a través del primer dispositivo de memoria y el segundo dispositivo de memoria y los dispositivos de memoria adicionales opcionales, si los hay, el camino de acceso estando adaptado para soportar transmisión de datos; y

acoplar eléctricamente el primer dispositivo de memoria a un controlador, el controlador configurado para acceder a los datos desde cualquier uno particular de los dispositivos de memoria en la pila en base a un flujo de datos a lo largo del camino desde el dispositivo de memoria en particular a través de los dispositivos de memoria sucesivos en la pila, si los hay, al controlador, en donde una conexión entre un último dispositivo de memoria en la pila de nuevo al controlador permite al controlador recibir datos almacenados en el dispositivo de memoria particular en la pila;

en el que cada dispositivo de memoria en la pila puede ser ajustado a un modo de paso a través o un modo de acceso a memoria, el modo de paso permitiendo la transmisión de datos recibidos en una entrada en serie (D0-D7, CSI, DSI) de un dispositivo de memoria respectivo a lo largo del camino de acceso hasta una salida en serie (Q0-7, OSC, DSO) del dispositivo de memoria respectivo, y

el modo de acceso a memoria permitiendo i) recibir datos en el camino de acceso y almacenar los datos en los circuitos de memoria asociados con el dispositivo de memoria respectivo, y

ii) recuperar datos de los circuitos de la memoria para su transmisión por el camino hacia una salida del dispositivo de memoria respectivo.

6. El procedimiento según la reivindicación 5, en el que el primer dispositivo de memoria (200-1; 201) incluye una cara de patillas de entrada-salida (201A, 201B; D0-D7, CSI, DSI, Q0-Q7, OSC, DSO) , y cada uno de los segundos dispositivos de memoria (200 -2; 202) y los dispositivos de memoria opcionales sucesivos, si los hay, incluyen una cara de patillas de entrada-salida (202A, 202B; D0-D7, CSI, DSI, Qo-Q7, OSC, DSO) ; y

producir la pila de dispositivos de memoria incluye orientar la cara del segundo dispositivo de memoria y la de cada uno de los otros dispositivos de memoria sucesivos opcionales en la pila, si lo hay, para apuntar en una misma dirección que la cara del primer dispositivo de memoria en la pila.

7. El procedimiento según la reivindicación 5 que comprende además:

escalonar cada uno de los segundos dispositivos de memoria (200-2; 202) y los dispositivos de memoria adicionales opcionales (200-3.

20. 4) , si los hay, con respecto a su respectivo dispositivo de memoria precedente (200-1 .

20. 3; 201) en la pila para exponer salidas (201B) en un plano del respectivo dispositivo de memoria anterior para conectarlas eléctricamente a las entradas (202A) en un plano del respectivo dispositivo de memoria sucesivo (200-2 .

20. 4)

proporcionar para cada uno de los segundos dispositivos de memoria (200-2; 202) y los dispositivos de memoria sucesivos opcionales (200-3.

20. 4) , si los hay, la conectividad eléctrica entre las salidas del respectivo dispositivo de memoria anterior a las entradas del respectivo dispositivo de memoria sucesivo a través de enlaces conductores (311) .

8. El procedimiento según la reivindicación 5, en el que la pila incluye un eje vertical a lo largo del que el segundo dispositivo de memoria (200-2; 202) se apila en el primer dispositivo de memoria (200-1; 201) , y que a lo largo de cada uno de los dispositivos de memoria sucesivos (200-3.

20. 4) , si los hay, se apila en el respectivo dispositivo de memoria anterior (200-2.

20. 3) en la pila,

el procedimiento comprende además:

desplazar rotacionalmente cada uno de los segundos dispositivos de memoria alrededor de 180 grados alrededor del eje vertical para alinear las salidas (201B; Qo-Q7, OSC, DSO) del primer dispositivo de memoria con entradas (202A; Do-D7, CSI, DSI) del segundo dispositivo de memoria, y

desplazar rotacionalmente cada uno de los dispositivos de memoria sucesivos adicionales, si lo hay, alrededor de 180 grados alrededor del eje vertical para alinear las salidas (201B; Q0-Q7, OSC, DSO) del dispositivo de memoria precedente respectivo en la pila con entradas (202A; D0- D7, CSI, DSI) de dicho dispositivo de memoria sucesivo.

9. El procedimiento según la reivindicación 5, en el que los dispositivos de memoria sucesivos comprenden además un tercer dispositivo de memoria (200-3; 203) ; y

el procedimiento comprende además:

proporcionar un espaciador entre el tercer dispositivo de memoria y el segundo dispositivo de memoria para acomodar la unión de salidas (201B; Q0-Q7, OSC, DSO) desde el primer dispositivo de memoria (200-1; 201) a las entradas correspondientes (202A; D0-D7, CSI, DSI) del segundo dispositivo de memoria (200-2; 202) .

SUSTRATO

PILA DE 3CHIPS

Patentes similares o relacionadas:

Dispositivo y procedimiento para el procesamiento de cuadros de datos en serie, del 11 de Octubre de 2018, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo para el procesamiento de cuadros de datos en serie, que comprende una unidad de convertidor en serie-paralelo , una unidad de evaluación […]

Memoria que usa un bus de nodo único de datos, direcciones y control, del 12 de Febrero de 2014, de MICROCHIP TECHNOLOGY INCORPORATED: Un sistema digital, que comprende una memoria que usa un bus de nodo único, de datos, direcciones y control, que comprende: una matriz de memoria adaptada […]

Circuito de terminación para terminación en troquel, del 6 de Noviembre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un circuito de terminación para proporcionar terminación en troquel para un terminal de undispositivo semiconductor , en […]

Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N, del 21 de Agosto de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador,que comprende:

dotar a un chip […]

Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N, del 21 de Agosto de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador,que comprende:

dotar a un chip […]

Dispositivo en cascada de cadena de margarita, del 4 de Junio de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un dispositivo semiconductor (410a, ..., 410d) que comprende: memoria; circuitos de entrada de reloj configurados para recibir una señal de reloj (SCLK); circuitos de […]

Dispositivo de Cascada de Cadena Tipo Margarita, del 12 de Septiembre de 2012, de MOSAID TECHNOLOGIES INCORPORATED: Un sistema que tiene una pluralidad de dispositivos conectados en serie que incluyen por lo menosprimeros y segundos dispositivos, caracterizado porque: el […]

SISTEMA DE MEDICION EN RED CON SENSORES Y UN PUENTE., del 16 de Marzo de 2007, de VLAAMSE INSTELLING VOOR TECHNOLOGISCH ONDERZOEK (VITO): Sistema de medición configurado para la medición de los valores físicos en una red de sensores de tipo bus, comprendiendo dicha red de sensores de tipo bus por […]

CONJUNTO DE MODULO DE MEMORIA QUE UTILIZA CHIPS PARCIALMENTE DEFECTUOSOS, del 1 de Noviembre de 2007, de CELETRONIX INTERNATIONAL, LTD

CELETRONIX USA, INC.: Procedimiento para la implementación selectiva de un reforzador de reloj, comprendiendo dicho procedimiento: montar un reforzador de reloj en una placa […]

CONJUNTO DE MODULO DE MEMORIA QUE UTILIZA CHIPS PARCIALMENTE DEFECTUOSOS, del 1 de Noviembre de 2007, de CELETRONIX INTERNATIONAL, LTD

CELETRONIX USA, INC.: Procedimiento para la implementación selectiva de un reforzador de reloj, comprendiendo dicho procedimiento: montar un reforzador de reloj en una placa […]