Semiconductor de potencia no uniforme y método de fabricación.

Un dispositivo semiconductor transistor bipolar de puerta aislada comprendiendo:

una pastilla semiconductora con un área activa (102) comprendiendo un conjunto de celdas activas (104);

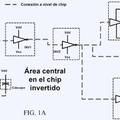

una primera parte del área activa compuesta por celdas (K) conforme con los primeros parámetros de diseño de celda seleccionados, donde los primeros parámetros de diseño de celda seleccionados determinan las dimensiones físicas de cada celda (K) de la primera parte del área activa (102), y donde la primera parte constituye la parte central del área activa (102);

una segunda parte del área activa compuesta por celdas (M) conforme con los segundos parámetros de diseño de celda seleccionados, donde los segundos parámetros de diseño de celda seleccionados determinan las dimensiones físicas de cada celda (M) en la segunda parte del área activa (102), donde los segundos parámetros de diseño de celda seleccionados difieren de los primeros parámetros de diseño de celda seleccionados, y donde las celdas (K) de la primera parte están rodeadas por las celdas (M) de la segunda parte;

una tercera parte del área activa compuesta por celdas (A) conforme con los terceros parámetros de diseño de celda seleccionados, donde los terceros parámetros de diseño de celda seleccionados determinan las dimensiones físicas de cada celda (A) en la tercera parte del área activa (102), donde los terceros parámetros de diseño de celda seleccionados difieren de los primeros parámetros de diseño de celda seleccionados, donde las terceras celdas seleccionadas (A) tienen parámetros de diseño que varían de los segundos parámetros de diseño de celda seleccionados, y donde las celdas (M) de la segunda parte están rodeadas por las celdas (A) de la tercera parte;

donde dichas celdas (K) de la primera parte, dichas celdas (M) de la segunda parte, y dichas celdas (A) de la tercera parte tienen cada una anchuras de canal distintas, donde la anchura de canal de dichas celdas (A) de la tercera parte es mayor que la anchura de canal de dichas celdas (M) de la segunda parte, donde la anchura de canal de dichas celdas (M) de la segunda parte es mayor que la anchura de canal de dichas celdas (K) de la primera parte, y donde algunas de las celdas (104) del área activa (102) están fabricadas con solo un pozo p y sin área fuente n+ .

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2002/000997.

Solicitante: IXYS CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 3540 Bassett Street Santa Clara California 95054 ESTADOS UNIDOS DE AMERICA.

Inventor/es: TSUKANOV,VLADIMIR, ZOMMER,NATHAN.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H01L27/02 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 27/00 Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00). › incluyendo componentes semiconductores especialmente adaptados para rectificación, amplificación, generación de oscilaciones, conmutación y teniendo al menos una barrera de potencial o una barrera de superficie.; incluyendo elementos de circuito pasivos integrados con al menos una barrera de potencial o una barrera de superficie.

- H01L27/108 H01L 27/00 […] › Estructuras de memorias dinámicas de acceso aleatorio.

- H01L29/06 H01L […] › H01L 29/00 Dispositivos semiconductores adaptados a la rectificación, amplificación, generación de oscilaciones o a la conmutación que tienen al menos una barrera de potencial o de superficie; Condensadores o resistencias, que tienen al menos una barrera de potencial o de superficie, p. ej. unión PN, región de empobrecimiento, o región de concentración de portadores de carga; Detalles de cuerpos semiconductores o de sus electrodos (H01L 31/00 - H01L 47/00, H01L 51/05 tienen prioridad; otros detalles de los cuerpos semiconductores o de sus electrodos H01L 23/00; consistentes en una pluralidad de componentes de estado sólido formados en o sobre un sustrato común H01L 27/00). › caracterizados por su forma; caracterizado por las formas, las dimensiones relativas o las disposiciones de las regiones semiconductoras.

- H01L29/08 H01L 29/00 […] › con regiones semiconductoras conectadas a un electrodo que transporta la corriente a rectificar, a amplificar o conmutar, formando parte este electrodo de un dispositivo semiconductor que tiene tres electrodos o más.

- H01L29/10 H01L 29/00 […] › con regiones semiconductoras conectadas a un electrodo que no transporta la corriente a rectificar, amplificar o conmutar, formando parte este electrodo de un dispositivo semiconductor que tiene tres electrodos o más.

- H01L29/739 H01L 29/00 […] › controlados por efecto de campo.

- H01L29/78 H01L 29/00 […] › estando producido el efecto de campo por una puerta aislada.

PDF original: ES-2711785_T3.pdf

Patentes similares o relacionadas:

Interruptor de alimentación de bloque con protección integrada contra descargas electrostáticas (esd) y polarización adaptativa del cuerpo, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento de fabricación de un circuito, que comprende: formar un interruptor de alimentación que comprenda múltiples etapas conectadas […]

Protección contra descargas electrostáticas para un transistor de efecto de campo sensible a iones, del 4 de Diciembre de 2019, de DNAE GROUP HOLDINGS LIMITED: Dispositivo que comprende una estructura de protección contra descargas electrostáticas , un transistor de efecto de campo sensible a iones […]

Disposición del circuito para la protección de una unidad que debe operarse desde una red de suministro contra sobretensiones, del 6 de Noviembre de 2019, de DEHN SE + Co KG: Disposición del circuito para proteger una unidad que debe operarse desde una red de suministro contra sobretensiones con una entrada que tiene una […]

Esquemas de interconexión posterior a la pasivación en la parte superior de los chips IC, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Una estructura de interconexión posterior a la pasivación, que comprende:

uno o más circuitos internos que comprenden uno o más dispositivos activos formados en […]

Esquemas de interconexión posterior a la pasivación en la parte superior de los chips IC, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Una estructura de interconexión posterior a la pasivación, que comprende:

uno o más circuitos internos que comprenden uno o más dispositivos activos formados en […]

Bloques de construcción distribuidos de circuitos de fijación r-c en el área central de la pastilla semiconductora, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Un aparato, que comprende:

una pastilla semiconductora que incluye un área central y un anillo de soporte;

circuitos de fijación […]

Bloques de construcción distribuidos de circuitos de fijación r-c en el área central de la pastilla semiconductora, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Un aparato, que comprende:

una pastilla semiconductora que incluye un área central y un anillo de soporte;

circuitos de fijación […]

Montaje de circuito para la protección de una unidad que debe operarse desde una red de suministro contra sobretensiones, del 22 de Mayo de 2019, de DEHN + SOHNE GMBH + CO. KG: Montaje de circuito para proteger una unidad que debe operarse desde una red de suministro contra sobretensiones con una entrada que tiene primera y […]

Desfasador, del 30 de Enero de 2019, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Un desfasador que comprende: una señal de entrada ; una señal de salida ; un circuito de protección contra descarga […]

PROCEDIMIENTO PARA CONTROLAR UN MOSFET DE POTENCIA, del 4 de Enero de 2011, de ROBERT BOSCH GMBH: Procedimiento para activar un MOSFET de potencia, en donde el MOSFET de potencia presenta un chip PMT (PMT) alojado en una carcasa de transistor (GH), cuya […]