Esquemas de interconexión posterior a la pasivación en la parte superior de los chips IC.

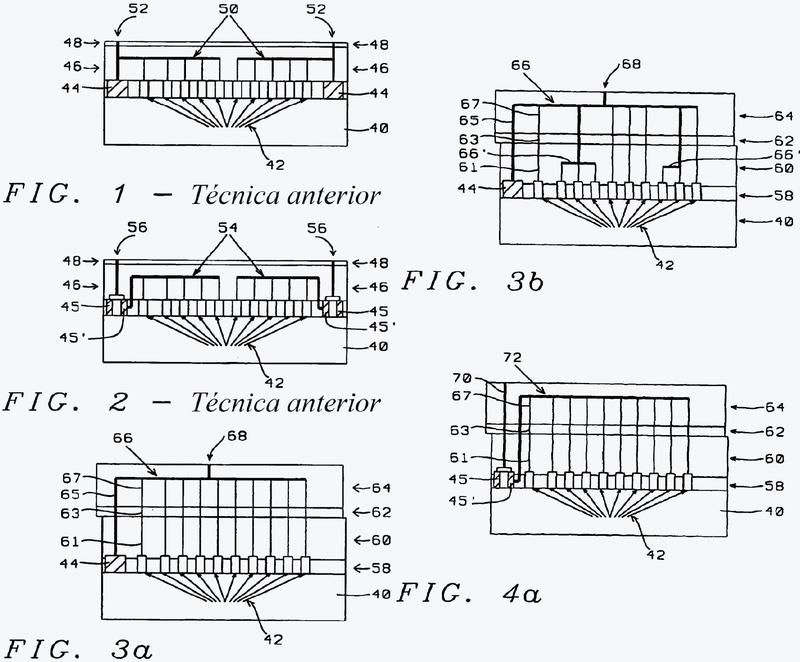

Una estructura de interconexión posterior a la pasivación, que comprende:

uno o más circuitos internos (42) que comprenden uno o más dispositivos activos formados en y sobre un sustrato semiconductor (40);

uno o más circuitos ESD (44) formados en y sobre dicho sustrato semiconductor (40);

una capa de interconexiones de línea fina (60) que comprende un sistema de metalización de línea fina, formado sobre dicho sustrato semiconductor (40) en una o más capas delgadas de dieléctrico;

una capa de pasivación (62) sobre dicha capa de interconexiones de línea fina (60);

un sistema de metalización grueso y ancho que es una red de interconexión de cables anchos y gruesos formada sobre dicha capa de pasivación, en una o más capas gruesas de dieléctrico (64),

en el que dichas capas gruesas de dieléctrico (64) son más gruesas que dichas capas delgadas de dieléctrico, en el que dicho sistema de metalización grueso y ancho se usa como una red de distribución para un estímulo eléctrico, y en el que dicho sistema de metalización grueso y ancho está conectado a dicho uno o más circuitos ESD (44), dicho uno o más circuitos internos (42), y al menos a una placa de interconexión (26, 28), en el que la una o más capas gruesas de dieléctrico son capas dieléctricas de polímero gruesas, y una parte de la línea metálica ancha y gruesa superior del sistema de metalización grueso y ancho forma la al menos una placa de interconexión (26, 28) en una capa superior de las capas gruesas de dieléctrico, y se utiliza la al menos una placa de interconexión (26, 28) como parte de la distribución en el plano horizontal.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E11002133.

Solicitante: QUALCOMM INCORPORATED.

Inventor/es: LIN,MOU-SHIUNG, LEE,JIN-YUAN.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H01L21/768 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 21/00 Procedimientos o aparatos especialmente adaptados para la fabricación o el tratamiento de dispositivos semiconductores o de dispositivos de estado sólido, o bien de sus partes constitutivas. › Fijación de interconexiones que sirvan para conducir la corriente entre componentes separados en el interior de un dispositivo.

- H01L23/522 H01L […] › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › que comprenden interconexiones externas formadas por una estructura multicapa de capas conductoras y aislantes inseparables del cuerpo semiconductor sobre el cual han sido depositadas.

- H01L23/528 H01L 23/00 […] › Configuración de la estructura de interconexión.

- H01L23/532 H01L 23/00 […] › caracterizadas por los materiales.

- H01L23/60 H01L 23/00 […] › Protección contra las cargas o las descargas electrostáticas, p. ej. pantallas Faraday.

- H01L23/62 H01L 23/00 […] › Protección contra las sobretensiones o sobrecargas, p. ej. fusibles, shunts.

- H01L27/02 H01L […] › H01L 27/00 Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00). › incluyendo componentes semiconductores especialmente adaptados para rectificación, amplificación, generación de oscilaciones, conmutación y teniendo al menos una barrera de potencial o una barrera de superficie.; incluyendo elementos de circuito pasivos integrados con al menos una barrera de potencial o una barrera de superficie.

PDF original: ES-2741876_T3.pdf

Patentes similares o relacionadas:

Sustrato de pastilla embebida con taladro posterior, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un dispositivo, que comprende: un sustrato que tiene un primer lado y un segundo lado opuesto, en el que el sustrato es un sustrato central que […]

Estructura y procedimiento para una TSV con alivio de tensión, del 17 de Junio de 2020, de QUALCOMM INCORPORATED: Una pastilla semiconductora que comprende: un sustrato que tiene una cara activa; capas conductoras acopladas a la cara activa; una vía […]

Sistema multicapas con elementos de contacto y procedimiento para la creación de un elemento de contacto para un sistema multicapas, del 2 de Mayo de 2018, de INTERPANE ENTWICKLUNGS- UND BERATUNGSGESELLSCHAFT MBH & CO. KG: Sistema de capas con elemento de contacto , que comprende un sustrato , un sistema multicapas dispuesto sobre el sustrato con al menos una capa superior […]

Dispositivo para el posicionamiento y la puesta en contacto de contactos de prueba, del 22 de Noviembre de 2017, de Pac Tech - Packaging Technologies GmbH: Dispositivo para el posicionamiento y la puesta en contacto de contactos de prueba en un soporte de contactos para producir una disposición de contactos […]

Proceso para rellenar surcos de contacto en microelectrónica, del 23 de Agosto de 2017, de MacDermid Enthone Inc: Proceso para metalizar un elemento de surco de contacto a través de silicio en un dispositivo de circuito integrado semiconductor, comprendiendo […]

Procedimiento para formar una imagen conductora sobre una superficie no conductora, del 24 de Junio de 2015, de Earthone Circuit Technologies Corporation: Procedimiento para formar una capa conductora sobre una superficie, que comprende realizar las siguientes etapas en orden: activar por lo […]

Estructura de interconexión basada en nanotubos de carbono redirigidos, del 11 de Febrero de 2015, de COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES: Dispositivo electrónico que comprende conexiones eléctricas que se extienden según al menos dos direcciones distintas, estando dichas conexiones realizadas por medio […]

Interruptor de alimentación de bloque con protección integrada contra descargas electrostáticas (esd) y polarización adaptativa del cuerpo, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento de fabricación de un circuito, que comprende: formar un interruptor de alimentación que comprenda múltiples etapas conectadas […]