PROCEDIMIENTO PARA CONTROLAR UN MOSFET DE POTENCIA.

Procedimiento para activar un MOSFET de potencia, en donde el MOSFET de potencia presenta un chip PMT (PMT) alojado en una carcasa de transistor (GH),

cuya conexión de puerta (G') está unida, a través de una resistencia (Rt), a una conexión de puerta (G) del MOSFET de potencia y en el que se vigila la temperatura de la capa de bloqueo del transistor, en donde en la carcasa del transistor (GH) está previsto un circuito de protección, que mide directamente la temperatura de la capa de bloqueo del transistor con un elemento de medición de temperatura (TM) y en el que, al alcanzarse una temperatura de la capa de bloqueo límite prefijable, se reduce la corriente de drenaje y con ello la pérdida de potencia del chip PMT (PMT), en donde el elemento de medición de temperatura (TM) está integrado en el chip PMT (PMT) o está alojado con el circuito de protección como chip adicional en la carcasa del transistor (GH), caracterizado porque la temperatura de la capa de bloqueo límite se prefija como valor nominal a través de una tensión de puerta (UGS) aplicada a la conexión de puerta (G) del MOSFET de potencia, porque el valor de medición correspondiente a la temperatura de la capa de bloqueo se compara con el valor nominal y porque la tensión de puerta (UGS') en la conexión de puerta (G') del chip PMT (PMT) está regulada a una temperatura de la capa de bloqueo constante, a través de un amplificador (V), de tal modo que el circuito de protección no desconecta la corriente de drenaje, sino sólo la reduce

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/DE1999/001378.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20 70442 STUTTGART ALEMANIA.

Inventor/es: BREITLING, WOLFRAM, FALLIANO, ROLF, WEIBLE, REINHOLD, HERSEL, WALTER.

Fecha de Publicación: .

Fecha Solicitud PCT: 7 de Mayo de 1999.

Fecha Concesión Europea: 4 de Agosto de 2010.

Clasificación Internacional de Patentes:

- H01L23/34 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › Disposiciones para la refrigeración, el calentamiento, la ventilación o la compensación de la temperatura.

Clasificación PCT:

- H01L27/02 H01L […] › H01L 27/00 Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00). › incluyendo componentes semiconductores especialmente adaptados para rectificación, amplificación, generación de oscilaciones, conmutación y teniendo al menos una barrera de potencial o una barrera de superficie.; incluyendo elementos de circuito pasivos integrados con al menos una barrera de potencial o una barrera de superficie.

- H02H5/04 H […] › H02 PRODUCCION, CONVERSION O DISTRIBUCION DE LA ENERGIA ELECTRICA. › H02H CIRCUITOS DE PROTECCION DE SEGURIDAD (indicación o señalización de condiciones de trabajo indeseables G01R, p. ej. G01R 31/00, G08B; localización de defectos a lo largo de las líneas G01R 31/08; dispositivos de protección H01H). › H02H 5/00 Circuitos de protección de seguridad para desconexión automática debida directamente a un cambio indeseable de las condiciones no eléctricas normales de trabajo con o sin reconexión (que utilizan dispositivos simuladores del aparato a proteger H02H 6/00; especialmente adaptados a máquinas o aparatos eléctricos de tipos específicos o a la protección seccional de sistemas de cables o de líneas H02H 7/00). › sensibles a una temperatura anormal.

Clasificación antigua:

- H01L27/02 H01L 27/00 […] › incluyendo componentes semiconductores especialmente adaptados para rectificación, amplificación, generación de oscilaciones, conmutación y teniendo al menos una barrera de potencial o una barrera de superficie.; incluyendo elementos de circuito pasivos integrados con al menos una barrera de potencial o una barrera de superficie.

- H02H5/04 H02H 5/00 […] › sensibles a una temperatura anormal.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Finlandia, Chipre.

Fragmento de la descripción:

Estado de la técnica

La invención se refiere a un procedimiento para activar un MOSFET de potencia con un chip PMT alojado en una carcasa de transistor, en el que se vigila la temperatura de la capa de bloqueo de transistor.

En el documento EP 0 414 499 A2 se describe un MOSFET con circuito de protección contra temperatura, que presenta un elemento sensor de temperatura de sustrato en una estructura de capas del MOSFET. Al alcanzar un límite de temperatura superior se desconecta el MOSFET y permanece en este estado hasta que se ha enfriado una unidad sensora de temperatura.

El documento US 5,457,419 muestra un MOSFET con un circuito de protección diseñado con dos etapas, en el que al alcanzarse un nivel de temperatura baja prefijada se reduce la corriente a través de la ruta drenaje-fuente del MOSFET, con lo que se obtiene un aumento de temperatura ralentizado, y se desconecta al alcanzarse un mayor nivel de temperatura del MOSFET.

Al utilizarse un MOSFETde potencia surge el problema de que, dependiendo de la pérdida de potencia que se produce en el chip PMT, se produce un aumento excesivo de temperatura de la capa de bloqueo de transistor con relación a la temperatura ambiente. Debido a que la máxima temperatura de capa de bloqueo admisible está limitada en el caso de semiconductores, es necesario asegurar en cada caso aplicativo que esta máxima temperatura de capa de bloqueo admisible no se supere.

Se conocen diferentes soluciones que dependen de la clase de aplicación del MOSFET de potencia. De este modo, por ejemplo en reguladores de sopladores, se fijan casi siempre varios MOSFETs de potencia conectados en paralelo para disipar calor sobre un cuerpo de refrigeración. El calor que se produce a causa de la pérdida de potencia en el chip PMT se dirige desde la capa de bloqueo de transistor al cuerpo de refrigeración y se entrega al entorno. A partir de la temperatura del cuerpo de refrigeración y de la pérdida de potencia momentánea se establece la temperatura de capa de bloqueo y, mediante un circuito de protección adicional, se limita la máxima pérdida de potencia.

Esta solución tiene diferentes inconvenientes. De este modo aparece, dependiendo de la pérdida de potencia que se produce en el chip PMT entre el punto de medición y la capa de bloqueo de transistor, una diferencia de temperatura más o menos grande. A causa de la masa del cuerpo de refrigeración se produce una desajuste de tiempo entre la temperatura de la capa de bloqueo y el punto de medición.

En el caso de un montaje defectuoso, por ejemplo suciedad entre el terminal de refrigeración del transistor y el cuerpo de refrigeración, del MOSFET de potencia sobre el cuerpo de refrigeración, la temperatura de la capa de bloqueo establecida es menor que la temperatura de la capa de bloqueo real, de tal modo que existe el riesgo de destrucción del MOSFET de potencia. Para impedir esto es necesario sobredimensionar el propio chip PMT y el circuito de protección.

También se ha intentado ya medir la temperatura de la capa de bloqueo directamente sobre la capa de bloqueo del transistor y reaccionar directamente a esta temperatura medida. Con ello está prefijado en el circuito de protección un umbral de temperatura, en el que se desconecta la corriente de drenaje del MOSFET de potencia. Con ello la desconexión de la corriente de drenaje puede realizarse de inmediato (OMNIFET) o retrasada en el tiempo (HITFET), para impedir una sobrecarga y una destrucción del MOSFET de potencia.

La tarea de la invención consiste en crear un procedimiento para activar un MOSFET de potencia de la clase citada al comienzo, MOSFET de potencia que, sin sobredimensionar el chip PMT y el circuito de protección esté protegido contra sobrecarga y destrucción sin limitar su comportamiento de conmutación.

Esta tarea es resuelta, en el caso del procedimiento conforme a la invención para activar un MOSFET de potencia, con un chip PMT alojado en una carcasa de transistor, cuya conexión de puerta está unida, a través de una resistencia, a una conexión de puerta del MOSFET de potencia y en el que se vigila la temperatura de la capa de bloqueo del transistor, en donde en la carcasa del transistor está previsto un circuito de protección, que mide directamente la temperatura de la capa de bloqueo del transistor con un elemento de medición de temperatura y en el que, al alcanzarse una temperatura de la capa de bloqueo límite prefijable, se reduce la corriente de drenaje y con ello la pérdida de potencia del chip PMT, en donde el elemento de medición de temperatura está integrado en el chip PMT o está alojado con el circuito de protección como chip adicional en la carcasa del transistor, por medio de que la temperatura de la capa de bloqueo límite se prefija como valor nominal a través de una tensión de puerta aplicada a la conexión de puerta del MOSFET de potencia, porque el valor de medición correspondiente a la temperatura de la capa de bloqueo se compara con el valor nominal y porque la tensión de puerta en la conexión de puerta del chip PMT está regulada a una temperatura de la capa de bloqueo constante, a través de un amplificador, de tal modo que el circuito de protección no desconecta la corriente de drenaje, sino sólo la reduce.

Con este circuito de protección se obtiene una temperatura de la capa de bloqueo constante que puede alcanzarse como máximo, que se corresponde con la temperatura de la capa de bloqueo límite y que es independiente de la tensión de puerta, aplicada al MOSFET de potencia, y de la tensión umbral del chip PMT. Siempre que la temperatura de conmutación de bloqueo que se ajusta en el chip PMT sea menor que la temperatura de la capa de bloqueo límite, el circuito de protección no tendrá ninguna influencia en el comportamiento de conmutación del MOSFET MOS.

Debido a que al alcanzarse la temperatura de la capa de bloqueo límite no se desconecta la corriente de drenaje, puede prescindirse del proceso de reconexión en el caso del procedimiento conforme a la invención. Por ello puede prescindirse de la complejidad externa de los circuitos conocidos para ello necesaria. En las aplicaciones en las que el chip PMT intenta volver a conectarse automáticamente aparecen procesos oscilatorios, que conducen a ruidos de instalación o, en el caso de otros casos aplicativos según lo dispuesto, a perturbaciones electromagnéticas. Esto se evita también en el caso del procedimiento conforme a la invención.

Aparte de esto el procedimiento conforme a la invención tiene la ventaja de que, en caso de fallo, la temperatura de la capa de bloqueo se limita a un valor constante. La potencia no se desconecta sino que vuelve a regularse, lo que permite en determinadas aplicaciones un funcionamiento de emergencia o un funcionamiento según lo dispuesto. Además de esto pueden conectarse directamente en paralelo varios MOSFETs de potencia de la nueva clase sin una complejidad de circuito adicional, en el caso de aplicaciones lineales y/o sincronizadas.

El elemento de medición de temperatura interno puede ser un elemento de temperatura que funcione sobre base de silicio, que entregue una señal de salida proporcional a la temperatura de la capa de bloqueo del transistor (corriente, tensión, resistencia). Puede ser una resistencia NTC o PTC.

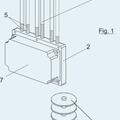

La invención se explica con más detalle con base en el ejemplo de ejecución representado en el dibujo. Aquí muestra la figura 1 un MOSFET de potencia, en el que el valor nominal (Soll) se deriva de la tensión de puerta.

En el caso del MOSFET de potencia representado en la figura 1 están previstas tres conexiones G, D y S en la carcasa de transistor GH, en donde las conexiones D y S están unidas directamente a la conexión de drenaje y a la conexión de fuente del chip PMT. La conexión G conduce, a través de una resistencia Rt, a la conexión de puerta G del chip PMT, en donde existe la posibilidad de prefijar la temperatura nominal de la capa de bloqueo a través de la tensión UGS en la conexión de puerta del MOSFET de potencia. La temperatura nominal es una función de la tensión UGS, es decir, a través de la tensión UGS puede prefijarse una temperatura de la capa de bloqueo límite. Esto significa que en el caso de aplicaciones lineales el grado de activación del chip PMT está enlazado con la temperatura nominal.

El elemento de medición de temperatura interno TM puede ser una resistencia NTC o PTC, o bien un elemento de temperatura que funcione sobre base de silicio. Entre las conexiones se obtiene una seña proporcional...

Reivindicaciones:

1. Procedimiento para activar un MOSFET de potencia, en donde el MOSFET de potencia presenta un chip PMT (PMT) alojado en una carcasa de transistor (GH), cuya conexión de puerta (G) está unida, a través de una resistencia (Rt), a una conexión de puerta (G) del MOSFET de potencia y en el que se vigila la temperatura de la capa de bloqueo del transistor, en donde en la carcasa del transistor (GH) está previsto un circuito de protección, que mide directamente la temperatura de la capa de bloqueo del transistor con un elemento de medición de temperatura (TM) y en el que, al alcanzarse una temperatura de la capa de bloqueo límite prefijable, se reduce la corriente de drenaje y con ello la pérdida de potencia del chip PMT (PMT), en donde el elemento de medición de temperatura (TM) está integrado en el chip PMT (PMT) o está alojado con el circuito de protección como chip adicional en la carcasa del transistor (GH), caracterizado porque la temperatura de la capa de bloqueo límite se prefija como valor nominal a través de una tensión de puerta (UGS) aplicada a la conexión de puerta (G) del MOSFET de potencia, porque el valor de medición correspondiente a la temperatura de la capa de bloqueo se compara con el valor nominal y porque la tensión de puerta (UGS) en la conexión de puerta (G) del chip PMT (PMT) está regulada a una temperatura de la capa de bloqueo constante, a través de un amplificador (V), de tal modo que el circuito de protección no desconecta la corriente de drenaje, sino sólo la reduce.

2. Procedimiento según la reivindicación 1, caracterizado porque como elemento de medición de temperatura (TM) se utiliza un elemento de temperatura que funciona sobre base de silicio, que entrega una señal de salida proporcional a la temperatura de la capa de bloqueo del transistor en dependencia de la temperatura aplicada, en especial corriente, tensión, resistencia.

3. Procedimiento según la reivindicación 1, caracterizado porque como elemento de medición de temperatura (TM) se utiliza una resistencia NTC o PTC.

4. Procedimiento según una de las reivindicaciones anteriores, caracterizado porque el elemento de medición de temperatura (TM) está fijado el chip PMT (PMT).

Sigue una hoja de dibujos.

Patentes similares o relacionadas:

Unidad de radio remota y equipo de comunicación, del 19 de Noviembre de 2018, de HUAWEI TECHNOLOGIES CO., LTD.: Una unidad de radio remota, que comprende un cuerpo de unidad y múltiples aletas de disipación de calor que se disponen en una superficie del cuerpo, […]

Dispositivo y procedimiento de control de temperatura y dispositivo electrónico, del 6 de Junio de 2018, de ZTE CORPORATION: Un dispositivo de control de temperatura, configurado para mantener una temperatura de funcionamiento de un componente de un dispositivo electrónico, que comprende: […]

Disipador de calor para el enfriamiento de módulos semiconductores de potencia, del 11 de Abril de 2018, de VESTAS WIND SYSTEMS A/S: Disipador de calor para enfriar al menos un módulo semiconductor de potencia con una placa base , comprendiendo el disipador de calor: una cubeta […]

Sistema para el control de temperatura de componentes o subgrupos electrónicos u optoelectrónicos, del 17 de Enero de 2018, de GLATT SYSTEMTECHNIK GMBH: Sistema para el control de temperatura de componentes o subgrupos electrónicos u optoelectrónicos, en el que un fluido de control de temperatura fluye para el control […]

Aparato de refrigeración, del 8 de Marzo de 2017, de DAIKIN INDUSTRIES, LTD.: Aparato de refrigeración que comprende: un circuito eléctrico que incluye un dispositivo de potencia ; una camisa de refrigerante que está conectada térmicamente […]

Dispositivo con un módulo electrónico de potencia para suministrar a un consumidor eléctrico de un aparato electrodoméstico una tensión de alimentación eléctrica, aparato electrodoméstico y procedimiento para la fabricación de tal dispositivo, del 28 de Septiembre de 2016, de BSH HAUSGERÁTE GMBH: Dispositivo para la alimentación de un consumidor eléctrico de un aparato electrodoméstico con tensión de alimentación eléctrica, que comprende un módulo electrónico […]

DISPOSITIVO DE REFRIGERACIÓN PARA UN CONVERTIDOR DE POTENCIA, del 20 de Enero de 2016, de YE, Zheng: 1. Dispositivo de refrigeración para un convertidor de potencia que comprende:

- una placa de un material térmicamente conductivo;

- al menos un conducto , que […]

DISPOSITIVO DE REFRIGERACIÓN PARA UN CONVERTIDOR DE POTENCIA, del 20 de Enero de 2016, de YE, Zheng: 1. Dispositivo de refrigeración para un convertidor de potencia que comprende:

- una placa de un material térmicamente conductivo;

- al menos un conducto , que […]

Procedimientos y dispositivos de solicitación a esfuerzo de un circuito integrado, del 3 de Junio de 2015, de Airbus Group SAS: Dispositivo de solicitación a esfuerzo de un circuito integrado que incluye una pastilla electrónica montada dentro de una envolvente , […]