Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N.

Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador,

que comprende:

dotar a un chip (11) de IC dentro de dicho paquete de IC con un núcleo (12) de microcontrolador que pre-senta un bus de datos de n-bits, una memoria acoplada con dicho núcleo (12) de microcontrolador y un pluralidadde bloques (26) funcionales acoplados con dicho núcleo (12) de microcontrolador;

dotar a dicho paquete de IC de una pluralidad de clavijas (34; 36; 38) eléctricamente acopladas a dicho chip(11) de IC, en el que un número total de clavijas (34; 36; 38) de dicho paquete de IC es inferior o igual a n;caracterizado por,

la provisión de al menos una de dicha pluralidad de clavijas (34; 36; 38) como una clavija multifunción eléctricamenteacoplada con al menos dos bloques (26) funcionales de dicha pluralidad de bloques (26) funcionales, en el que elnúcleo (12) de microcontrolador es operable para habilitar solo uno de dichos al menos dos bloques (26) funcionalespara soportar una función para dicha clavija multifunción, en el que un primer bloque (26) funcional es una unidad depuerto de E / S bidireccional y un segundo bloque (26) funcional proporciona una función de programación en serie.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E05001413.

Solicitante: MICROCHIP TECHNOLOGY INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 2355 WEST CHANDLER BOULEVARD CHANDLER, ARIZONA 85224-6199 ESTADOS UNIDOS DE AMERICA.

Inventor/es: FINK,SCOTT, HULL,RICHARD, BINGHAM,GREGORY, ELLISON,SCOTT.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F13/40 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › Estructura del bus.

- G06F15/78 G06F […] › G06F 15/00 Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general. › que comprenden una sola unidad central.

- G11C5/06 G […] › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 5/00 Detalles de memorias cubiertos por el grupo G11C 11/00. › Disposiciones para interconectar eléctricamente elementos de almacenamiento, p. ej. por cableado.

PDF original: ES-2432358_T3.pdf

Fragmento de la descripción:

Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N

Antecedentes de la invención 1. Campo de la invención La presente invención se refiere al campo de los microcontroladores y al de los procedimientos aplicados a ellos y, más concretamente, a un microcontrolador que presenta una arquitectura de n-bits (esto es, una anchura de bus de datos) con un número de clavijas tipo Entrada / Salida (E / S) inferior a n y a un procedimiento aplicado a aquél.

2. Descripción de la técnica relacionada Los microcontroladores son ampliamente conocidos y utilizados en muy diferentes aplicaciones. Una arquitectura típica utilizada hoy en día en los microcontroladores es la arquitectura de 8-bits (esto es, la anchura del bus de datos del microcontrolador es una anchura de 8 bits) . Un problema en este y otros tamaños de microcontroladores es que para soportar una arquitectura de n-bits, se requieren más de n clavijas para ser conectadas al microcontrolador. Mediante la reducción del número de clavijas requeridas para soportar un n-bit o más concretamente, un controlador de 8-bits, el coste global de la utilización del dispositivo se reduce, y se conserva el espacio limitado. Por tanto, existía la necesidad de proporcionar un microcontrolador que ofreciera una arquitectura de n-bits con un número de clavijas inferior o igual a n y a un procedimiento para su aplicación.

La publicación de K.AXER: “Una EEPROM con un Bus de 12C para Electrónica de Consumidor” Conferencia de Circuitos de Estados Sólidos [“An EEPROM with 12C Bus for Consumer Electronics” Solid States Circuits Conference], 1984, ESSCIRC “84”, décima conferencia, septiembre de 2004 (09-2004) , páginas 153 a 156, divulga un paquete de Circuito Integrado que comprende una unidad de función de control de IC acoplada a un bus de 8-bits en el que el número total de clavijas de dicho paquete de Circuito Integrado acoplado a dicha unidad de control de IC es igual a 8.

El documento US-A-742 215 divulga una tarjeta de IC que incorpora 8 clavijas de contacto que incorpora el mismo número de clavijas que su anchura del bus de datos interno. El documento ilustra una clavija multifunción conectada a dos bloques funcionales, esto es, una función de entrada y una función de salida.

Sumario de la invención El procedimiento de la invención se define en la reivindicación independiente. Otras mejoras están caracterizadas en las reivindicaciones dependientes.

Breve descripción de las formas de realización preferentes Los expuestos y otros objetos, características distintivas y ventajas de la invención se pondrán de manifiesto a partir de la subsecuente, más concreta, descripción de las formas de realización preferentes de la invención, como se ilustra en el dibujo que se acompaña.

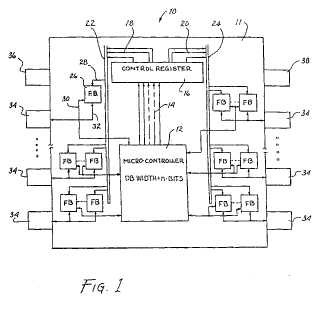

Breve descripción del dibujo La FIG. 1 es una vista de un diagrama de bloques simplificado del paquete microcontrolador de IC que incorpora un bus de datos de n-bits y n-clavijas.

Descripción de las formas de realización preferentes Se divulga un paquete de Circuito Integrado (IC) que comprende, en combinación, un chip de IC con un microcontrolador en su interior que presenta un bus de datos de n-bits, y hasta n clavijas eléctricamente acopladas al microcontrolador. El paquete de IC comprende también un medio de registro de control acoplado al microcontrolador para recibir señales de habilitación e inhabilitación. Unos medios de configuración de la función de clavija están también incluidos acoplados al medio de registro de control para determinar una función para una clavija correspondiente de las n clavijas. El medio de configuración de la función de clavija comprende al menos un medio de bloque funcional acoplado al medio de registro de control para determinar una función para una clavija correspondiente. El medio de configuración de función de clavija puede comprender una pluralidad de medios de bloque funcional cada uno acoplado al medio de registro de control y a una correspondiente clavija de las n clavijas para determinar una función diferente para la clavija correspondiente de las n clavijas. El medio de registro de control proporciona unos medios de línea de control independientes para cada uno de los medios de bloque funcional para transferir a cada uno de los medios de bloque funcional una de las señales de habilitación y de inhabilitación. Solo uno de los medios de bloque funcionales por clavija es habilitado una vez cada uno mediante la señal de habilitación para configurar una clavija correspondiente para una función asociada con los medios de bloque funcional habilitados. Cada medio de bloque funcional está acoplado a una clavija correspondiente de las n clavijas y al microcontrolador para transferir

datos entre la clavija correspondiente y el microcontrolador cuando es habilitado un bloque concreto de los bloques funcionales. Así mismo, las n clavijas incluyen un número de clavijas tipo Entrada / Salida (E / S) inferior a n.

Con referencia a la FIG. 1, el paquete de IC o paquete de la presente invención se muestra y se designa globalmente mediante la referencia numeral 10. El paquete 10 de IC comprende un chip 11 de IC con un núcleo de microcontrolador o simplemente el microcontrolador 12 dispuesto en su interior que presenta un Bus de Datos (DB) de n-bits y hasta n clavijas 34 a 38 eléctricamente acopladas al microcontrolador 12. El modo de fabricación de los paquetes 10 de IC, de los chips 11, y de los microcontroladores 12 son bien conocidos por los expertos en la materia. El microcontrolador 12 presenta, en general, un bus de datos amplio de n-bits pero más concretamente aquí, una arquitectura de 8-bits o una arquitectura de bus de datos. Nótese que el bus de datos propiamente dicho no se muestra con detalle para simplificar el dibujo.

El paquete 10 de IC comprende también un registro 16 de control acoplado al microcontrolador 12 por medio de un bus 14 de señales de control para recibir señales de habilitación e inhabilitación del microcontrolador 12. Los registros de control son bien conocidos por los expertos en la materia. El registro 16 de control puede ser cualquier elemento que pueda contener un estado conocido (esto es, carga, corriente, o tensión) como por ejemplo SRAM, DRAM, EPROM, EEPROM, ROM, Lógica Combinatoria, PROM, o similares. El registro 16 de control proporciona la capacidad de memoria suficiente para almacenar y transferir las señales de habilitación e inhabilitación enviadas desde el microcontrolador 12 a los bloques 26 funcionales lo que se describirá más adelante. El protocolo de comunicaciones para el envío de las señales de habilitación e inhabilitación desde el microcontrolador 12 hasta los bloques 26 funcionales por medio del registro 16 de control es bien conocido por los expertos en la materia. Las señales de habilitación e inhabilitación son encaminadas desde el registro 16 de control hasta los bloques 26 funcionales apropiados por medio de los buses 18 a 24. Desde los buses 22 y 24, cada bloque 26 funcional está acoplado por medio de unos conectores 28 para recibir la señal de habilitación o inhabilitación enviada desde el registro 16 de control. Nótese también que cada bloque 26 funcional presenta una conexión 32 con una clavija 34 respectiva para transferir datos hacia o desde la clavija 34. Así mismo, cada bloque 26 funcional presenta una conexión 30 con el microcontrolador 12 para transferir hacia o recibir del microcontrolador 12 los datos apropiados.

Nótese que las clavijas 36 y 38 no presentan ningún bloque funcional 26 acoplado a ellas. Ello se debe a que estas clavijas 36 y 38 son suministro de alimentación y de tierra para el paquete 10 y, por tanto, no requieren ningún bloque funcional. Nótese que las líneas de alimentación y de tierra procedentes de las clavijas 36 y 38 no se muestran para simplificar el dibujo. Las clavijas representan o bien solo clavijas de entrada o de tipo E / S, ambos tipos sobradamente conocidos en la técnica. Cuál entre la clavija 34 es solo de entrada y cuál es de tipo E /S depende de la aplicación del usuario. Nótese que la segunda clavija 34 de la esquina izquierda superior del paquete 10 solo incorpora un bloque 26 funcional acoplado a ella. De esta manera, esta clavija 34 concreta presenta solo una función asociada con ella. Nótese que esta representación de función única se muestra solo con la finalidad de demostrar cuál sería el aspecto de una clavija 34 de función única. De esta manera, cualquiera de las clavijas 34 podrían ser clavijas de función única, o una clavija 34 de función múltiple. Así mismo, nótese que las demás clavijas 34 se muestran con dos bloques 26 funcionales... [Seguir leyendo]

Reivindicaciones:

1. Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador, que comprende:

dotar a un chip (11) de IC dentro de dicho paquete de IC con un núcleo (12) de microcontrolador que presenta un bus de datos de n-bits, una memoria acoplada con dicho núcleo (12) de microcontrolador y un pluralidad de bloques (26) funcionales acoplados con dicho núcleo (12) de microcontrolador;

dotar a dicho paquete de IC de una pluralidad de clavijas (34; 36; 38) eléctricamente acopladas a dicho chip

(11) de IC, en el que un número total de clavijas (34; 36; 38) de dicho paquete de IC es inferior o igual a n;

caracterizado por,

la provisión de al menos una de dicha pluralidad de clavijas (34; 36; 38) como una clavija multifunción eléctricamente acoplada con al menos dos bloques (26) funcionales de dicha pluralidad de bloques (26) funcionales, en el que el núcleo (12) de microcontrolador es operable para habilitar solo uno de dichos al menos dos bloques (26) funcionales para soportar una función para dicha clavija multifunción, en el que un primer bloque (26) funcional es una unidad de puerto de E / S bidireccional y un segundo bloque (26) funcional proporciona una función de programación en serie.

2. El procedimiento de acuerdo con la reivindicación 1, en el que la al menos una de dicha pluralidad de clavijas (36) es una clavija de tensión de alimentación y una de dicha pluralidad de clavijas (38) es una clavija de masa a tierra.

3. El procedimiento de acuerdo con la reivindicación 1, en el que los al menos dos bloques (26) funcionales acoplados con dicho microcontrolador (12) comprenden cada uno una entrada y / o salida (32) de señal acoplada con al menos una clavija (34) multifunción y una entrada (28) de habilitación para habilitar o inhabilitar la función de dicho bloque (26) funcional.

4. El procedimiento de acuerdo con la reivindicación 3, que comprende también: el acoplamiento de un registro (16) de control con dicho núcleo (12) de microcontrolador y con dichas entradas (28) de habilitación de dichos bloques (26) funcionales.

5. El procedimiento de acuerdo con una de las reivindicaciones precedentes 1 a 4, que comprende también: dotar a dicho chip de IC de un bus (14) de señal acoplado con dicho registro (16) de control y con dicho núcleo (12) de microcontrolador para enviar señales desde dicho microcontrolador (12) hasta dicho registro (16) de control dependiendo de cuáles de dichas unidades (26) funcionales necesitan ser habilitadas y cuáles de dichas unidades (26) funciones necesita ser inhabilitadas.

6. El procedimiento de acuerdo con una de las reivindicaciones precedentes, en el que dicha pluralidad de clavijas se extienden desde los lados de dicho paquete de IC.

7. El procedimiento de acuerdo con una de las reivindicaciones precedentes 1 a 6, en el que dicha memoria es una SRAM, DRAM, EPROM, EEPROM, ROM, PROM o un dispositivo lógico.

8. El procedimiento de acuerdo con una de las reivindicaciones precedentes, en el que uno de dichos bloques (26) funcionales proporciona una función de clavija de datos de programación en serie.

9. El procedimiento de acuerdo con una de las reivindicaciones precedentes, en el que uno de dichos bloques (26) funcionales proporciona una función de reloj de programación en serie.

10. El procedimiento de acuerdo con una de las reivindicaciones precedentes, en el que la al menos una clavija multifunción está eléctricamente acoplada a más de dos bloques (26) funcionales.

11. Un procedimiento de acuerdo con una de las reivindicaciones precedentes, en el que para operar el paquete de IC, el procedimiento comprende también la etapa de:

la ejecución de una instrucción predefinida, tras lo cual son enviadas unas señales de control apropiadas hasta un registro de control que habilita o inhabilita el apropiado bloque funcional acoplado con dicha al menos una clavija multifunción.

12. El procedimiento de acuerdo con la reivindicación 11, en el que dicha etapa se lleva a cabo para todas las clavijas multifunción de dicho paquete de IC.

Patentes similares o relacionadas:

Dispositivo y procedimiento para el procesamiento de cuadros de datos en serie, del 11 de Octubre de 2018, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo para el procesamiento de cuadros de datos en serie, que comprende una unidad de convertidor en serie-paralelo , una unidad de evaluación […]

Memoria que usa un bus de nodo único de datos, direcciones y control, del 12 de Febrero de 2014, de MICROCHIP TECHNOLOGY INCORPORATED: Un sistema digital, que comprende una memoria que usa un bus de nodo único, de datos, direcciones y control, que comprende: una matriz de memoria adaptada […]

Circuito de terminación para terminación en troquel, del 6 de Noviembre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un circuito de terminación para proporcionar terminación en troquel para un terminal de undispositivo semiconductor , en […]

Almacenamiento de datos y estructuras apilables, del 18 de Septiembre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un sistema que comprende una pila incluyendo: un primer dispositivo de memoria ; un segundo dispositivo de memoria […]

Dispositivo en cascada de cadena de margarita, del 4 de Junio de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un dispositivo semiconductor (410a, ..., 410d) que comprende: memoria; circuitos de entrada de reloj configurados para recibir una señal de reloj (SCLK); circuitos de […]

Dispositivo de Cascada de Cadena Tipo Margarita, del 12 de Septiembre de 2012, de MOSAID TECHNOLOGIES INCORPORATED: Un sistema que tiene una pluralidad de dispositivos conectados en serie que incluyen por lo menosprimeros y segundos dispositivos, caracterizado porque: el […]

SISTEMA DE MEDICION EN RED CON SENSORES Y UN PUENTE., del 16 de Marzo de 2007, de VLAAMSE INSTELLING VOOR TECHNOLOGISCH ONDERZOEK (VITO): Sistema de medición configurado para la medición de los valores físicos en una red de sensores de tipo bus, comprendiendo dicha red de sensores de tipo bus por […]

CONJUNTO DE MODULO DE MEMORIA QUE UTILIZA CHIPS PARCIALMENTE DEFECTUOSOS, del 1 de Noviembre de 2007, de CELETRONIX INTERNATIONAL, LTD

CELETRONIX USA, INC.: Procedimiento para la implementación selectiva de un reforzador de reloj, comprendiendo dicho procedimiento: montar un reforzador de reloj en una placa […]

CONJUNTO DE MODULO DE MEMORIA QUE UTILIZA CHIPS PARCIALMENTE DEFECTUOSOS, del 1 de Noviembre de 2007, de CELETRONIX INTERNATIONAL, LTD

CELETRONIX USA, INC.: Procedimiento para la implementación selectiva de un reforzador de reloj, comprendiendo dicho procedimiento: montar un reforzador de reloj en una placa […]