Esquema de control de sistema de memoria Flash.

Método para programación en un sistema de memoria Flash que tiene una pluralidad de dispositivos de memoria Flash,

comprendiendo el método:

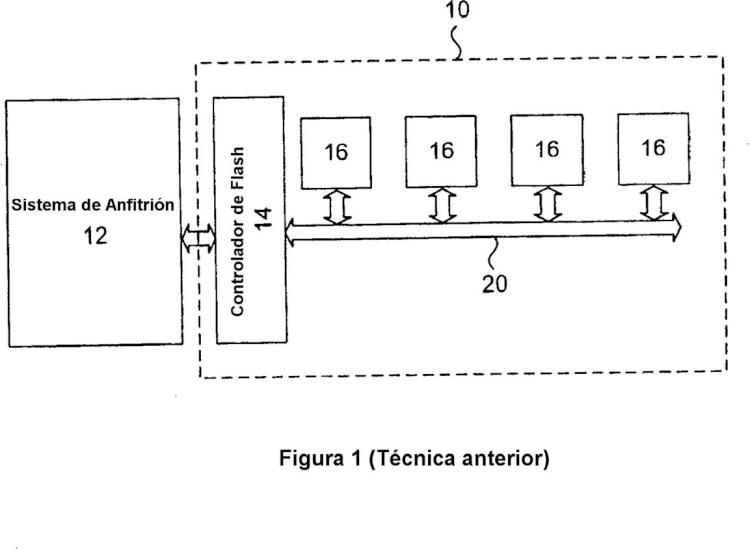

recibir (402) un archivo de datos que tiene una pluralidad de páginas;

si la totalidad de la pluralidad de páginas del archivo de datos puede caber en un único bloque de uno de entre la pluralidad de dispositivos de memoria Flash, programar la totalidad de la pluralidad de páginas del archivo de datos en el bloque único de uno de entre la pluralidad de dispositivos de memoria Flash;

si no, si la totalidad de la pluralidad de páginas del archivo de datos puede caber en una pluralidad de bloques incluyendo un bloque en cada uno de entre la pluralidad de dispositivos de memoria, programar con intercalación (410) la totalidad de la pluralidad de páginas del archivo de datos por la pluralidad de bloques incluyendo un bloque en cada uno de entre la pluralidad de dispositivos de memoria; y

si no, programar con intercalación un subconjunto de la pluralidad de páginas del archivo de datos en una pluralidad de bloques incluyendo un bloque en cada uno de entre la pluralidad de dispositivos de memoria y eliminar (414) del archivo de datos el subconjunto de la pluralidad de páginas del archivo de datos.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E10171414.

Solicitante: MOSAID TECHNOLOGIES INCORPORATED.

Nacionalidad solicitante: Canadá.

Dirección: 11 Hines Road, Suite 203 Ottawa, ON K2K 2X1 CANADA.

Inventor/es: KIM,JIN-KI.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C11/4193 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 11/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento eléctricos o magnéticos particulares; Elementos de almacenamiento correspondientes (G11C 14/00 - G11C 21/00 tienen prioridad). › Circuitos auxiliares específicos para tipos particulares de dispositivos semiconductores de almacenamiento, p. ej. para el direccionamiento, el accionamiento, la lectura, la sincronización, la alimentación, la propagación de señal (G11C 11/4063, G11C 11/413 tienen prioridad).

- G11C16/00 G11C […] › Memorias de sólo lectura programables y borrables (G11C 14/00 tiene prioridad).

- G11C7/10 G11C […] › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

PDF original: ES-2498096_T3.pdf

Fragmento de la descripción:

Esquema de control de sistema de memoria Flash.

Referencia cruzada a solicitudes relacionadas

La presente solicitud reivindica la prioridad de la solicitud de patente provisional US n.° 60/788.083, presentada el 31 de marzo de 2006.

Campo de la invención

La presente invención se refiere en general a memorias Flash. Más particularmente, la presente invención se refiere a un sistema de memoria Flash de múltiples dispositivos para aplicaciones de almacenamiento de gran capacidad.

Antecedentes de la invención

La memoria Flash es un tipo de memoria no volátil usado comúnmente y de manera extendida como medios de almacenamiento de gran capacidad para electrónica de consumo, tal como, por ejemplo, cámaras digitales y reproductores portátiles digitales de música. La densidad de un chip de memoria Flash disponible en la actualidad puede ser de hasta 32 Gbits (4 GB), lo cual resulta adecuado para su uso en unidades de almacenamiento Flash USB populares puesto que el tamaño de un chip Flash es pequeño.

La llegada de cámaras digitales de 8 megapíxeles y de dispositivos portátiles digitales de entretenimiento con capacidades musicales y de vídeo ha estimulado la demanda de capacidades ultra-altas para almacenar las grandes cantidades de datos a las que no puede llegar el dispositivo de memoria Flash individual. Por lo tanto, múltiples dispositivos de memoria Flash se combinan entre sí formando un sistema de memoria para incrementar de manera eficaz la capacidad de almacenamiento disponible. Por ejemplo, para tales aplicaciones puede que se requieran densidades de almacenamiento Flash de 20 GB.

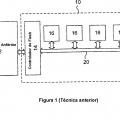

La Figura 1 es un diagrama de bloques de un sistema de memoria Flash 10 de la técnica anterior en el que se ha integrado un sistema de anfitrión 12. El sistema de memoria Flash 10 incluye un controlador de memorias Flash 14 en comunicación con el sistema de anfitrión 12, y múltiples dispositivos de memoria no volátil 16. El sistema de anfitrión incluirá un dispositivo de procesado, tal como un microcontrolador, microprocesador, o un sistema de ordenador. El sistema de memoria Flash 10 de la Figura 1 está configurado para incluir un canal 20, donde dispositivos de memoria 16 se conectan en paralelo al canal 20. Aquellos expertos en la materia entenderán que el sistema de memoria 10 tendrá conectados al mismo, un número cualquiera de dispositivos de memoria.

El canal 20 incluye un conjunto de buses comunes, los cuales incluyen líneas de datos y de control que están conectadas a todos sus dispositivos de memoria correspondientes. Aunque no se muestra, cada dispositivo de memoria se habilita/deshabilita con una señal respectiva de selección de chip proporcionada por el controlador de memorias Flash 14. El controlador de Flash 14 es responsable de emitir órdenes y datos, por medio del canal, a un dispositivo de memoria seleccionado sobre la base del funcionamiento del sistema de anfitrión 12. Datos leídos de los dispositivos de memoria se transfieren, por medio del canal de vuelta al controlador de memorias Flash 14 y al sistema de anfitrión 12. Al sistema de memoria Flash 10 se le hace referencia en general como configuración multi- drop, en la cual los dispositivos de memoria 16 están conectados en paralelo con respecto al canal 20.

En el sistema de memoria Flash 10, los dispositivos de memoria no volátil 16 son idénticos entre sí, y típicamente se ¡mplementan como dispositivos de memoria Flash NAND. Aquellos expertos en la materia entenderán que la memoria Flash está organizada en bancos, y cada banco está organizado en bloques para facilitar el borrado de bloques. Los dispositivos de memoria Flash NAND con mayor disponibilidad comercial están configurados para tener dos bancos de memoria. Antes de ofrecer una descripción del funcionamiento del sistema de memoria Flash 10, se expone una breve visión general de un núcleo de memoria con un solo dispositivo de memoria Flash NAND.

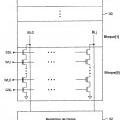

La Figura 2 es un diagrama de bloques general de un banco de una memoria Flash NAND conocida. El blanco 30 está organizado en k+1 bloques. Cada bloque está compuesto por cadenas de celdas de memoria NAND, presentando hasta i+1 celdas de memoria Flash conectadas en serie entre sí. Por consiguiente, las líneas de palabra WL0 a WLI están conectadas a las puertas de cada celda de memoria Flash de la cadena de celdas de memoria. Un dispositivo de selección de cadenas conectado a la señal SSL (línea de selección de cadenas) conecta selectivamente la cadena de celdas de memoria a una línea de bit, mientras que un dispositivo de selección de tierra conectado a la señal GSL (línea de selección de tierra) conecta selectivamente la cadena de celdas de memoria a una línea de fuente, tal como VSS. El dispositivo de selección de cadenas y el dispositivo de selección de tierra son transistores de n canales. Hay j+1 líneas de bit comunes para todos los bloques del banco 30, y cada línea de bit está conectada a una cadena de celdas de memoria NAND en cada uno de los bloques [0] a [kj. Cada señal de línea de palabra (WL0 a WLI), SSL y GSL está conectada al mismo dispositivo de transistor correspondiente en cada cadena de celdas de memoria NAND del bloque. Tal como deberían conocer aquellos expertos en la materia, a los

datos almacenados en las celdas de memoria Flash a lo largo de una línea de palabra se les hace referencia como página de datos.

Conectado a cada línea de bit fuera del banco 30 se encuentra un registro de datos 32 para almacenar una página de datos de escritura a programar en una página de celdas de memoria Flash. El registro de datos 32 Incluye también circuitos de detección para detectar datos leídos de una página de celdas de memoria Flash. Durante operaciones de programación, los registros de datos llevan a cabo operaciones de verificación de programas para garantizar que los datos se han programado correctamente en las celdas de memoria Flash conectadas a la línea de palabra seleccionada. La programación dentro de un bloque se inicia típicamente en la página correspondiente a WL0, y prosigue secuenclalmente hasta WLi para llenar el bloque actual. A continuación, la programación continúa con la WL0 de un bloque nuevo. Dentro de un dispositivo, los bloques se programan de manera secuencial.

Volviendo al sistema de memoria Flash 10 de la Figura 1, existen cuestiones específicas que tendrán un Impacto negativo en el rendimiento del sistema. Algunas son físicas mientras que otras son arquitectónicas.

La configuración del sistema de memoria Flash 10 impone limitaciones físicas sobre el rendimiento. Con el alto número de señales paralelas que se extienden por el sistema, la integridad de señal correspondiente a las señales que transportan se verá deteriorada por la interferencia cruzada, el desfase de la señal, y el ruido de conmutación simultánea (SSN). El consumo de energía en una configuración de este tipo se convierte en un problema en la medida en la que cada pista de señal entre el controlador de flash y los dispositivos de memoria flash se carga y descarga frecuentemente para la señalización. Con frecuencias cada vez mayores del reloj del sistema, el consumo de energía también se incrementará.

Desde un punto de vista arquitectónico, las operaciones de programación ocuparán demasiado tiempo. Una de las funciones principales del controlador de Flash 14 es gestionar la escritura de datos en los dispositivos de memoria del sistema. En el contexto de las memorias Flash, a la escritura de datos se le hace referencia más comúnmente como programación de datos. Existen dos cuestiones significativas relacionadas con la programación Flash. En primer lugar, la programación Flash es lenta con respecto a memorias volátiles, tales como la DRAM y SRAM, y otras memorias no volátiles, tales como las unidades de disco duro. La programación de datos en celdas de memoria Flash requiere voltajes altos y una secuencia de programación escalonada para obtener una distribución ajustada de voltajes de umbral programados. En un dispositivo de memoria Flash NAND que tiene dos bancos de memoria, se programan simultáneamente dos páginas de datos, una para cada banco. Puesto que existe solamente un registro de datos por cada banco, las operaciones de programación adicionales deben esperar hasta que las páginas actuales hayan sido programadas satisfactoriamente. Por lo tanto, la programación de grandes cantidades de datos en los dispositivos Flash 16 puede requerir una cantidad significativa de tiempo.

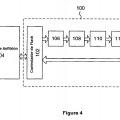

Una segunda cuestión en relación con el sistema de memoria Flash 10 convencional es la estructura lineal de archivos de los datos de programación. La Figura 3 es una ilustración de la estructura convencional de archivos para un sistema... [Seguir leyendo]

Reivindicaciones:

1. Método para programación en un sistema de memoria Flash que tiene una pluralidad de dispositivos de memoria Flash, comprendiendo el método:

recibir (402) un archivo de datos que tiene una pluralidad de páginas;

si la totalidad de la pluralidad de páginas del archivo de datos puede caber en un único bloque de uno de entre la pluralidad de dispositivos de memoria Flash, programar la totalidad de la pluralidad de páginas del archivo de datos en el bloque único de uno de entre la pluralidad de dispositivos de memoria Flash;

si no, si la totalidad de la pluralidad de páginas del archivo de datos puede caber en una pluralidad de bloques incluyendo un bloque en cada uno de entre la pluralidad de dispositivos de memoria, programar con intercalación (410) la totalidad de la pluralidad de páginas del archivo de datos por la pluralidad de bloques incluyendo un bloque en cada uno de entre la pluralidad de dispositivos de memoria; y

si no, programar con intercalación un subconjunto de la pluralidad de páginas del archivo de datos en una pluralidad de bloques incluyendo un bloque en cada uno de entre la pluralidad de dispositivos de memoria y eliminar (414) del archivo de datos el subconjunto de la pluralidad de páginas del archivo de datos.

2. Método según la reivindicación 1, que comprende además repetir la programación con intercalación del subconjunto de la pluralidad de páginas del archivo de datos en la pluralidad de bloques incluyendo un bloque en cada uno de entre la pluralidad de dispositivos de memoria y eliminar del archivo de datos el subconjunto de la pluralidad de páginas del archivo de datos.

3. Método según la reivindicación 1, que comprende además seleccionar el bloque único de uno de entre la pluralidad de dispositivos de memoria Flash según el número más alto de ciclos restantes de programación/borrado que quedan para el dispositivo de memoria.

4. Método según la reivindicación 1, que comprende además seleccionar el bloque único de uno de entre la pluralidad de dispositivos de memoria Flash según el último dispositivo de memoria programado.

5. Método según la reivindicación 1, en el que la programación con intercalación comprende proporcionar secuencialmente órdenes de programación a cada uno de entre la pluralidad de dispositivos de memoria.

Patentes similares o relacionadas:

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Método de procesado de datos, aparato de almacenamiento, disco de estado sólido y sistema de almacenamiento, del 28 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesado de datos, aplicado a un sistema de almacenamiento, en donde el sistema de almacenamiento comprende un anfitrión, un controlador y un […]

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Circuitos de líneas de bits globales de Memoria Estática de Acceso Aleatorio (SRAM) para reducir los fallos de energía durante los accesos de lectura de memoria, y procedimientos y sistemas relacionados, del 17 de Abril de 2019, de QUALCOMM INCORPORATED: Un circuito de línea de bits global de memoria estática de acceso aleatorio, SRAM, para una pluralidad de células de bits de SRAM, que […]

Dispositivo de memoria híbrida con una única interfaz, del 23 de Enero de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento que comprende: recibir, en un controlador , órdenes, direcciones y datos en un dispositivo de memoria mediante una interfaz definida asociada […]

Dispositivo y procedimiento para el procesamiento de cuadros de datos en serie, del 11 de Octubre de 2018, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo para el procesamiento de cuadros de datos en serie, que comprende una unidad de convertidor en serie-paralelo , una unidad de evaluación […]

Arquitectura central en serie de memoria no volátil, del 3 de Septiembre de 2014, de Conversant Intellectual Property Management Inc: Sistema de memoria que comprende: banco de memoria para suministrar datos de lectura de flujo de bits en serie en respuesta a una operación […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]