Dispositivo para la detección de bordes y mejora de calidad en una imagen.

Dispositivo para la detección de bordes y mejora de calidad en una imagen que comprende una agrupación de celdas elementales de procesamiento idénticas e interconectadas localmente.

Cada celda de procesamiento se caracteriza a su vez por un comparador que lleva a cabo en paralelo la comparación de cada par de pixeles vecinos. La tensión umbral que establece la diferencia de tensión entre pixeles considerados parte de un borde se determina mediante un ajuste temporal de una señal de control. Este ajuste, junto con el de la señal de control de filtrado, también de carácter temporal, son los únicos necesarios para configurar el procesamiento deseado. No se requieren señales analógicas externas de control por lo que se facilita la programación del hardware por el dispositivo que se utilice y se reduce el número de convertidores digital/analógico del sistema final.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201200474.

Solicitante: UNIVERSIDAD DE SEVILLA.

Nacionalidad solicitante: España.

Inventor/es: RODRIGUEZ VAZQUEZ,ANGEL, CARMONA GALÁN,Ricardo, FERNÁNDEZ BERNI,Jorge.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06T7/60 FISICA. › G06 CALCULO; CONTEO. › G06T TRATAMIENTO O GENERACIÓN DE DATOS DE IMAGEN, EN GENERAL. › G06T 7/00 Análisis de imagen. › Análisis de los atributos geométricos.

- H01L27/085 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 27/00 Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00). › comprendiendo únicamente componentes de efecto de campo.

Fragmento de la descripción:

DISPOSITIVO PARA LA DETECCiÓN DE BORDES Y MEJORA DE CALIDAD EN UNA

IMAGENEl campo técnico de la invención es el de la microelectrónica. Su marco de aplicación es el de los dispositivos electrónicos de muy bajo consumo de potencia que desempeñan tareas de visión artificial, es decir, captura de imágenes, análisis de las mismas y actuación en caso de que los resultados de dicho análisis así lo requieran.

ESTADO DE LA TÉCNICA ANTERIOR

La detección de bordes y la mejora de la calidad en una imagen pueden ser llevadas a cabo de diferentes maneras. Una opción es el empleo de sistemas digitales de cómputo de propósito general. Estos sistemas pueden ser programados para procesar imágenes. A modo de ejemplo, un escenario típico sería el desarrollo de software para análisis de imágenes sobre un PC. Este software ejecutaría una serie de instrucciones haciendo uso del correspondiente microprocesador hasta conseguir el resultado deseado. La principal ventaja de este enfoque es la flexibilidad para abordar cualquier tipo de tarea gracias al carácter generalista del hardware subyacente. Sin embargo, esta ventaja se torna en inconveniente cuando las especificaciones de una aplicación concreta exigen sólo un conjunto restringido de las funcionalidades proporcionadas por este tipo de sistemas pero con un consumo de potencia mucho menor y niveles de rendimiento, en el sentido del número de operaciones por segundo, similares, o incluso superiores.

La naturaleza no específica del hardware es precisamente lo que impide en la mayoría de las ocasiones cumplir dichos requerimientos. Se plantean en el estado de la técnica alternativas puramente digitales a este problema. Una primera opción es utilizar procesadores digitales de señal optimizados para la ejecución de determinadas operaciones muy útiles para el procesado de imágenes, como por ejemplo la convolución. Otra opción sería la implementación de primitivas de procesamiento en circuitos integrados reconfigurables como FPGAs (Field-Programmable Gate Arrays) o CPLDs (Complex Programmable Logic Devices) . También se puede plantear el diseño de circuitería digital específica para una determinada aplicación e integrarla en un chip. De las mencionadas, la última opción es la que permite obtener las mayores cotas de rendimiento y de eficiencia energética.

Asimismo se conocen del estado de la técnica documentos que describen el uso de circuitería de señal mixta (analógica y digital) para el procesamiento de imágenes como en la patente US2003/0108221. También se describe el uso de circuitería de señal mixta en las publicaciones J. Dubois, D. Ginhac, M. Paindavoine, y B. Heyrman, tiA 10000 FPS CMOS sensor with massively parallel image processing, " IEEE J. Solid-State Circuits, vol. 43, no. 3, pp. 706-717, 2008; P. Dudek, "SCAMP-3: A vision chip with SIMD current-mode analogue processor array, " Focal-plane Sensor-Processor Chips, publicado por Springer, 2011; Femández Bemi, R. Carmona Galán y Luis Carranza González, "FLlP-Q: A QCIF resolution focal-plane array for low-power image processing, " IEEE J. Solid-State Circuits, vol. 46, no. 3, pp. 669-680, 2011. La mayoría de estos documentos están basados en la arquitectura de procesamiento descrita en la patente EP 1580814 que se caracteriza por una agrupación bidimensional de procesadores elementales interconectados que trabajan de manera concurrente y conjunta para implementar una determinada operación sobre una imagen.

En el documento J. Poikonen, M. Laiho, and A. Paasio, "Anisotropic filtering with a resistive fuse network on the MIPA4k processor array, " in IEEE Intemational Workshop on Cellular Nanoscale Networks and Their Applications, 2010 se hace uso de la física inherente a una

red de condensadores interconectados mediante resistencias para llevar a cabo un filtrado selectivo de una imagen, consiguiendo así eliminar ruido espacial sin afectar su contraste. Ese filtrado selectivo viene determinado por una circuitería de comparación que permite localizar los bordes de la imagen. Así, entre aquellos pixeles etiquetados como pertenecientes a un borde no se realiza filtrado alguno mientras que sobre el resto sí. Además de la mencionada mejora de calidad, la circuitería de comparación también hace posible la obtención de una imagen binaria donde se resaltan esos pixeles considerados como bordes en la imagen original.

EXPLICACiÓN DE LA INVENCiÓN

La presente invención tiene aplicación en dispositivos electrónicos de muy bajo consumo de potencia diseñados para realizar tareas de visión artificial. En concreto, el dispositivo de la invención permite la detección de bordes y la mejora de la calidad de la imagen. El dispositivo, además, permite el desarrollo de dispositivos autónomos de visión con un bajo consumo de potencia. Esta invención hace posible un alargamiento significativo de la vida útil de estos dispositivos en escenarios en los que es necesaria la máxima autonomía posible como ocurre en la monitorización de espacios naturales, la robótica, ayuda a la navegación aérea no tripulada, etc.

El dispositivo de la presente invención emplea tensiones para la representación de los pixeles, no se utilizan corrientes como ocurre en el documento J. Poikonen, M. Laiho, and A. Paasio, "Anisotropic filtering with a resistive fuse network on the MIPA4k processor array, " in IEEE International Workshop on Cellular Nanoscale Networks and Their Applications, 2010

del estado de la técnica. La comparación entre pixeles vecinos que lleva a determinar la existencia o no de un borde se realiza también en modo tensión, no en modo corriente como en dicho documento del estado de la técnica.

La clave de la invención es el comparador que lleva a cabo en paralelo la comparación de cada par de pixeles vecinos. Por una parte, la tensión umbral que establece la diferencia de tensión entre pixeles considerados parte de un borde se determina mediante un ajuste temporal de una señal de control. Este ajuste, junto con el de la señal de control de filtrado, también de carácter temporal, son los únicos necesarios para configurar el procesamiento deseado. No se requieren señales analógicas externas de control por lo que se facilita la programación del hardware por el dispositivo que se utilice y se reduce el número de convertidores digital/analógico del sistema final. Además, debido al hecho de trabajar en modo tensión y a la forma de implementación que se propone, la eficiencia energética del comparador de la presente invención es mucho mayor que la obtenida por otras implementaciones conocidas del estado de la técnica.

La utilización de circuitería de señal mixta permite explotar al maxlmo la física de los transistores a la hora de procesar las señales eléctricas que representan los valores de los pixeles de una imagen, posibilitando la consecución de mejores cifras de rendimiento y consumo de potencia que una implementación digital equivalente. La circuitería novedosa de la invención permite conseguir un consumo de potencia mucho menor que cualquier otro dispositivo hasta el momento.

Asimismo, es objeto de la presente invención un método para la detección hardware de bordes y mejora de calidad en una imagen, implementado en el dispositivo descrito anteriormente y que comprende las etapas de asociar el valor de cada píxel de la imagen con el valor de tensión analógica almacenado en un condensador interconectado mediante al menos dos transistores MOS a los condensadores de su vecindad inmediata en la fila inferior y la columna de la derecha, de tal forma que la tensión en cada uno de los condensadores vecinos representa a su vez el pixel correspondiente a esa posición espacial dentro de la distribución; y comparar el valor local del píxel de manera programable con los píxeles vecinos mediante unos comparadores de tensión con salida digital; y donde el resultado de la comparación con cada vecino es combinado respectivamente con una señal global de filtrado activa por nivel lógico 'O' a través de una puerta digital OR cuyas salidas controlan el terminal de puerta del transistor que interconecta las celdas elementales; y donde la salida de los comparadores de tensión se combina mediante otra puerta digital OR cuya salida representa una imagen binaria donde aquellos píxeles con nivel lógico '1' determinan la localización de los bordes de la imagen.

A lo largo de la descripción y las reivindicaciones la palabra "comprende" y sus variantes no pretenden excluir otras características técnicas, aditivos, componentes o pasos. Para los expertos en la materia, otros objetos, ventajas y características de la invención se desprenderán en parte de la descripción y en parte de la práctica de la invención....

Reivindicaciones:

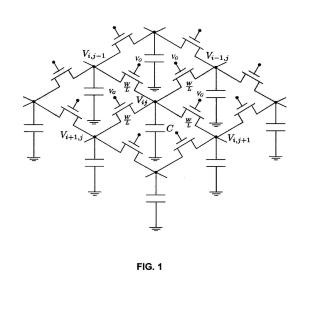

1. Dispositivo para la detección de bordes y mejora de calidad en una imagen que comprende un hardware de señal mixta y que comprende una pluralidad de celdas elementales de procesamiento en paralelo idénticas e interconectadas localmente y que se caracteriza porque

-cada pixel de la imagen está representado analógicamente por el valor de tensión de un condensador (1) , estando dicho condensador (1) interconectado mediante al menos dos transistores MOS (2, 3) a los condensadores (1) de su vecindad inmediata, que representan a los pixeles contiguos, que están en la fila inferior y en la columna de la derecha;

-la celda elemental comprende además unos comparadores de tensión (4, 5) con salida digital que permiten la comparación del valor local de un pixel con el valor local de sus pixeles vecinos teniendo como entradas el valor del pixel a estudio y el valor del pixel contiguo;

-el dispositivo comprende al menos dos puertas digitales OR (6, 7) que combinan la salida de cada comparador de tensión (4, 5) con una señal global de filtrado activa por nivel lógico 'O', estando las salidas de las puertas digitales OR (6, 7) conectadas con el terminal de puerta de los transistores MOS (2, 3) ;

-y la celda elemental comprende una tercera puerta digital OR (8) que tiene como entradas las salidas de los comparadores de tensión (4, 5) Y cuya salida representa una imagen binaria que tiene valor lógico '1' para los pixeles que son bordes en la imagen original y que tiene valor lógico 'O' para los restantes pixeles.

2. Dispositivo según la reivindicación 1 en donde los comparadores (4, 5) comprenden un par diferencial (9, 10, 11) cuya entrada viene determinada por las tensiones de los pixeles a comparar y cuya corriente de salida se convierte a tensión mediante la descarga programable por tiempo de condensadores (12) pre-cargados a una cierta tensión, donde este intervalo de tiempo de descarga determina la tensión umbral del comparador; y donde tanto la precarga de los condensadores (12) como su descarga se controlan mediante una única señal que determina el estado abierto o cerrado de los respectivos interruptores (13, 14) .

3. Dispositivo de acuerdo con la reivindicación 2 en donde la conversión analógico-digital del resultado de la comparación se realiza mediante una puerta digital XOR (15) cuyas entradas corresponden a las tensiones finales de los condensadores (12) tras su pre-carga y posterior descarga durante un intervalo de tiempo programable.

4. Dispositivo de acuerdo con cualquiera de las reivindicaciones 2 a 3 en donde la salida de la puerta digital XOR es almacenada en un elemento de memoria (16) hasta que se lleva a cabo la siguiente comparación.

5. Dispositivo de acuerdo con cualquiera de las reivindicaciones 2 a 4 en donde el instante de almacenamiento viene también fijado por la señal de control de los interruptores (13, 14) .

6. Método para la detección hardware de bordes y mejora de calidad en una imagen, implementado en el dispositivo de cualquiera de las reivindicaciones 1 a 5 que comprende las etapas de: (i) asociar el valor de cada píxel de la imagen con el valor de tensión analógica en un condensador (1) interconectado mediante al menos dos transistores MOS (2, 3) a los condensadores (1) de su vecindad inmediata en la fila inferior y la columna a la derecha, de tal forma que la tensión en cada uno de los condensadores vecinos representa a su vez el pixel correspondiente a esa posición espacial dentro de la distribución; (ii) comparar el valor local del píxel de manera programable con los píxeles vecinos mediante unos comparadores de tensión (4, 5) con salida digital; y donde el resultado de la comparación con cada vecino es combinado respectivamente con una señal global de filtrado activa por nivel lógico 'O' a través de una puerta digital OR (6, 7) cuyas salidas controlan el terminal de puerta del transistor que interconecta los transistores MOS (2, 3) de las celdas; y donde la salida de los comparadores de tensión (4, 5) se combina mediante una segunda puerta digital OR cuya salida representa una imagen binaria donde aquellos píxeles con nivel lógico '1' determinan la localización de los bordes en la imagen original.

7. Método de acuerdo con la reivindicación 6 en donde la comparación comprende una etapa de conversión a tensión de la corriente de salida del par diferencial (9, 10, 11) de los comparadores mediante la descarga programable por tiempo de unos condensadores (12) pre-cargados a una cierta tensión, donde este intervalo de tiempo de descarga determina la tensión umbral del comparador; y donde tanto la precarga de los condensadores (12) como su descarga se controlan mediante una única señal de control que determina el estado abierto o cerrado de los respectivos interruptores (13, 14) .

8. Método de acuerdo con la reivindicación 7 en donde la conversión analógico-digital del resultado de la comparación se realiza mediante una puerta digital XOR (15) cuya entradas corresponden a las tensiones finales de los condensadores (12) tras su pre-carga y posterior descarga durante un intervalo de tiempo programable.

9. Método de acuerdo con cualquiera de las reivindicaciones 7 a 8 en donde la salida de la puerta digital XOR es almacenada en un elemento de memoria (16) hasta que se lleva a cabo la siguiente comparación.

10. Método de acuerdo con cualquiera de las reivindicaciones 7 a 9 en donde el instante de almacenamiento viene también fijado por la señal de control de los interruptores (13, 14) .

FIG.1

Ve .l

Vi~, J"+1

(1)

Ve-1 (2)

I

Vi+1, j -=

FIG.2

(7)

Vi, j+1

I

FIG.3

VDD

... ---sD Q Vout ctrl---o ~~

(16)

ctrl ctrl

FIG.4

DIFE..EN

• Vi, j+l

I

FIG.5a

1.5V

, .. -----tD

Vout

ctrl ctrl

0.15 0.15 L--ctrl

ctrl... J

G.i3 0.13 r---

~ ~

o.6V--l

FIG.5b

Patentes similares o relacionadas:

Sistema de generación de marcador y método, del 29 de Julio de 2020, de NEC CORPORATION: Un sistema de generación de marcador que comprende:

medios de entrada de imagen de vídeo para proporcionar como entrada una imagen de vídeo;

[…]

Sistema de generación de marcador y método, del 29 de Julio de 2020, de NEC CORPORATION: Un sistema de generación de marcador que comprende:

medios de entrada de imagen de vídeo para proporcionar como entrada una imagen de vídeo;

[…]

SISTEMA Y MÉTODO DE IDENTIFICACIÓN DE PARTÍCULAS EN MICROSCOPÍA DE TRANSMISIÓN, del 16 de Abril de 2020, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): La presente invención se refiere a un sistema automático, programable y adaptafivo de bajo coste que permite llevar a cabo el flujo de trabajo completo de un sistema bio- indicador […]

SISTEMA Y MÉTODO DE IDENTIFICACIÓN DE PARTÍCULAS EN MICROSCOPÍA DE TRANSMISIÓN, del 14 de Abril de 2020, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): Sistema y método de identificación de partículas en microscopía de transmisión La presente invención se refiere a un sistema automático, programable y adaptativo […]

Sistema y método para clasificar unidades foliculares, del 25 de Septiembre de 2019, de Restoration Robotics, Inc: Método de clasificación para procedimientos de trasplante capilar de una unidad folicular (FU) individual basándose en un número de cabellos en la FU individual, que comprende:

[…]

Sistema y método para clasificar unidades foliculares, del 25 de Septiembre de 2019, de Restoration Robotics, Inc: Método de clasificación para procedimientos de trasplante capilar de una unidad folicular (FU) individual basándose en un número de cabellos en la FU individual, que comprende:

[…]

Aparato, sistema y método para ayudar a proporcionar un diagnóstico de una condición médica de un cerebro de mamífero, así como un medio legible por computadora que comprende un programa para llevar a cabo el método, del 4 de Septiembre de 2019, de ERASMUS UNIVERSITY MEDICAL CENTER ROTTERDAM: Un aparato para ayudar a proporcionar un diagnóstico de una condición médica de un cerebro de mamífero, el cerebro tiene una primera y una segunda parte, el aparato incluye […]

Metrología en vivo de un objeto durante la fabricación u otras operaciones, del 21 de Agosto de 2019, de THE BOEING COMPANY: Un método para metrología en vivo de un objeto, que comprende: realizar una operación de escaneado mediante una pluralidad de sensores para […]

Método y sistema para estimar la masa de una reserva, del 26 de Junio de 2019, de Intertek Group Plc: Un método para estimar la masa de material de una reserva, en donde el método incluye:

obtener un perfil de la superficie superior de dicha reserva; en donde […]

Método y sistema para estimar la masa de una reserva, del 26 de Junio de 2019, de Intertek Group Plc: Un método para estimar la masa de material de una reserva, en donde el método incluye:

obtener un perfil de la superficie superior de dicha reserva; en donde […]

Métodos de predicción de blastocistos embrionarios in vitro, del 21 de Junio de 2019, de ARES TRADING S.A.: Un método para seleccionar uno o más embriones humanos fertilizados in vitro que es probable que alcancen el estadio de blastocisto, que comprende: […]