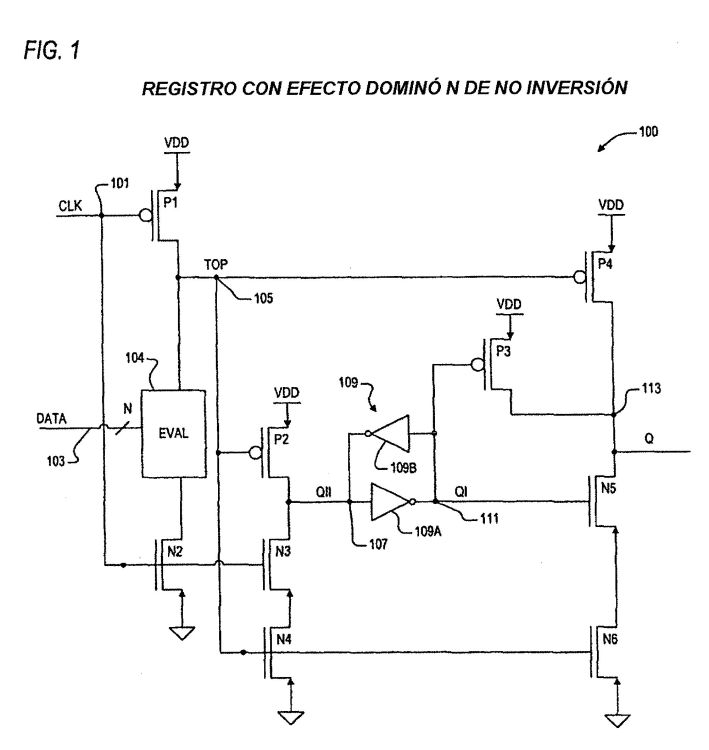

REGISTRO DE EFECTO DOMINO N CON TRAYECTO ACELERADO SIN DESCARGA.

Un registro con efecto dominó de no inversión (800), que comprende:

una etapa con efecto dominó para evaluar una función lógica basada en al menos una señal de datos de entrada (DATA) y una señal de reloj por impulsos (PLSCLK), retrasando dicha señal de reloj por impulsos (PLSCLK) una señal de reloj simétrica (PH1CLK), en el que dicha etapa con efecto dominó precarga un nodo precargado (TOP) alto cuando dicha señal de reloj simétrica (PH1CLK) está baja y abre una ventana de evaluación cuando dicha señal de reloj por impulsos (PLSCLK) va alta, y tira de dicho nodo precargado (TOP) hacia abajo si lo evalúa, y mantiene dicho nodo precargado (TOP) alto si no lo evalúa; una etapa de escritura, acoplada a dicha etapa con efecto dominó y en respuesta a dichas señales de reloj por impulsos (PLSCLK) y simétricas (PH1CLK), que tiran de un primer nodo de salida preliminar (QII) hacia arriba si dicho nodo precargado (TOP) va bajo, y que tira de dicho primer nodo de salida preliminar (QII) hacia abajo cuando dichos nodo precargado (TOP) y señal de reloj simétrica (PH1CLK) están altos; un inversor (401) que tiene una entrada acoplada a dicho primer nodo de salida preliminar (QII) y una salida acoplada a un segundo nodo de salida preliminar (QI); un trayecto mantenedor alto (P3, P4), que mantiene dicho primer nodo de salida preliminar (QII) alto cuando está habilitado, en el que dicho trayecto mantenedor más alto está habilitado cuando dicha señal de reloj simétrica (PH1CLK) y dicho segundo nodo de salida preliminar (QI) están ambos bajos y el cual en caso contrario está inhabilitado; un trayecto mantenedor bajo (N4, N5), que mantiene dicho primer nodo de salida preliminar (QII) bajo cuando está habilitado, en el que dicho trayecto mantenedor bajo está habilitado cuando dicho segundo nodo de salida preliminar (QI) y dicho nodo precargado (TOP) están ambos altos y que en caso contrario está inhabilitado; y una etapa de salida, que proporciona una señal de salida (Q) basada en estados de dicho nodo precargado (TOP) y en dicho segundo nodo de salida preliminar (QI).

Tipo: Resumen de patente/invención.

Solicitante: VIA TECHNOLOGIES, INC..

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: 8 F, NO. 535 CHUNG-CHENG ROAD,HSIN-TIEN CITY TAIPEI HSIEN 23.

Inventor/es: QURESHI,IMRAN, BERTRAM,RAYMOND A.

Fecha de Publicación: .

Fecha Solicitud PCT: 20 de Julio de 2006.

Fecha Concesión Europea: 14 de Enero de 2009.

Clasificación PCT:

- H03K19/096 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › Circuitos síncronos, es decir, circuitos que utilizan señales de reloj.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Patentes similares o relacionadas:

Registro dinámico de canal N acelerado, del 21 de Marzo de 2012, de VIA TECHNOLOGIES, INC.: Registro dinámico, de canal N, no inversor, que comprende:

una etapa dominó, para evaluar una función lógica en base a al menos una señal de datos de entrada y una […]

Registro dinámico de canal N acelerado, del 21 de Marzo de 2012, de VIA TECHNOLOGIES, INC.: Registro dinámico, de canal N, no inversor, que comprende:

una etapa dominó, para evaluar una función lógica en base a al menos una señal de datos de entrada y una […]

FAMILIA DE CIRCUITOS LOGICOS PARALELOS DE ENTRADA LOGICA COMPLEMENTARIA (CLIP)., del 16 de Noviembre de 1995, de THUNDERBIRD TECHNOLOGIES, INC.: UNA FAMILIA DE CIRCUITOS LOGICOS PARALELOS DE ENTRADA LOGICA COMPLEMENTARIA (CLIP), DE BAJA CAPACITANCIA Y ALTA VELOCIDAD QUE INCLUYE UNA […]

CONTROL DEL PICO DE CORRIENTE EN CMOS DINAMICAS., del 1 de Octubre de 1993, de AMERICAN TELEPHONE AND TELEGRAPH COMPANY: UN CIRCUITO INTEGRADO QUE TIENE UN GRAN NUMERO DE ETAPAS CON PUERTAS LOGICAS PARA TRASMISION SE HA ENCONTRADO QUE SUFRE UNA GRAN PICO DE CORRIENTE AL CONECTARSE. ESTO ES […]

CIRCUITO DE ENGANCHE DE SALIDA DOMINÓ N, del 23 de Diciembre de 2011, de VIA TECHNOLOGIES, INC.: Un circuito de enganche dominó N que comprende: una etapa dominó (P1, N2, 301) acoplada a una señal (CLK) de reloj aproximadamente simétrica, y para evaluar una función […]

REGISTRO DE TIPO DOMINÓ P, del 25 de Mayo de 2011, de VIA TECHNOLOGIES, INC.: Registro de tipo dominó P, que comprende: una etapa dominó, acoplada a una señal de impulsos de reloj, y destinada a evaluar una función lógica según […]

REGISTRO DE TIPO DOMINÓ P, del 25 de Mayo de 2011, de VIA TECHNOLOGIES, INC.: Registro de tipo dominó P, que comprende: una etapa dominó, acoplada a una señal de impulsos de reloj, y destinada a evaluar una función lógica según […]