MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS.

Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles (1202),

configurada para almacenar registros de parches asociados que se emplean para parchear circuitos de estado de la máquina o microcódigo en el microprocesador o almacenar entidades de datos de control asociadas que se emplean para programar circuitos de control en el microprocesador uno o más bancos de fusibles (1202) de configuración codificados para indicar si cada uno de dicha pluralidad de bancos de fusibles se programa con uno de dichos registros de parches asociados o con una de dichas entidades de datos de control asociadas; y un controlador de grupo (1201), acoplado a dicha pluralidad de bancos de fusibles, configurado para leer dicha pluralidad de bancos de fusibles, y configurado para proporcionar dichos registros de parches asociados a un cargador de parches (311, 511, 711, 1011) o dichas entidades de datos de control asociadas a los circuitos de control en el microprocesador, en donde dicho cargador de parches proporciona parches que corresponden a dichos registros de parches asociados, como se prescribió, a los mecanismos de parches objetivo designados en el microprocesador; en donde dicho cargador de parches proporciona dichos parches a dichos mecanismos de parches objetivo designados siguiendo la transición de una señal de restablecimiento del microprocesador y antes de la ejecución de las instrucciones almacenadas en una ROM del BIOS (333, 533, 733, 1033)

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E07253294.

Solicitante: VIA TECHNOLOGIES, INC..

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: 8F, NO.535, CHUNG-CHENG ROAD HSIN-TIEN CITY TAIPEI 231 TAIWAN.

Inventor/es: PARKS,TERRY, GLENN,HENRY G.

Fecha de Publicación: .

Fecha Solicitud PCT: 21 de Agosto de 2007.

Fecha Concesión Europea: 11 de Agosto de 2010.

Clasificación Internacional de Patentes:

- G06F9/318T

Clasificación PCT:

- G06F9/318 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › con extensión o modificación de operaciones.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

ANTECEDENTES DE LA INVENCIÓN

CAMPO DE LA INVENCIÓN

Esta invención se refiere en general al campo de la microelectrónica, y más particularmente a un aparato y método para realizar parches de microcódigo en un microprocesador. 5

DESCRIPCIÓN DE LA TÉCNICA RELACIONADA

Hoy en día los microprocesadores se diseñan para ejecutar muchas instrucciones por ciclo de reloj y proporcionar muchas características para maximizar el número de instrucciones que se ejecutan durante un ciclo de reloj dado. Un ciclo de reloj se considera generalmente que es aquel intervalo de tiempo que se asigna para 10 cada una de las etapas del conducto en el microprocesador para realizar el trabajo de procesamiento que se requiere para enviar los resultados a la siguiente etapa del conducto. Y los microprocesadores de hoy en día comprenden muchas etapas del conducto, un número de las cuales se configura en paralelo, para permitir tareas de procesamiento simultáneas o concurrentes, que permiten de esta manera que 15 instrucciones múltiples sean ejecutadas en paralelo. Se proporciona una señal de reloj central a cada una de las etapas del conducto para sincronizar la ejecución de instrucciones en cada una de las etapas. La señal de reloj central a menudo es un múltiplo en frecuencia de una señal de reloj de canal principal que se proporciona desde un circuito generador de reloj externo. 20

Como apreciará un experto en la técnica, las principales etapas de un microprocesador de conducto actual se pueden dividir en aquéllas asociadas con traer las instrucciones (es decir, la lógica de la etapa de traer) de la memoria, traducir las instrucciones (es decir, la lógica de la etapa de traducción) en secuencias asociadas de las microinstrucciones que son únicas (es decir, “nativas a”) el microprocesador 25 específico, ejecutar (es decir, la lógica de la etapa de ejecución) las secuencias asociadas de las microinstrucciones, y escribir (por ejemplo, escribir la lógica de la etapa de atrás) los resultados de las ejecuciones para ubicaciones designadas.

Las etapas de traducir y traer anteriormente mencionadas se describen dentro del contexto de un ordenador de conjunto de instrucciones complejas (CISC) de hoy 30 en día que emplea macroinstrucciones, tales como se exhiben por la arquitectura del conjunto de instrucciones (ISA) x86 ubicua. Una macroinstrucción única se emplea para especificar un número de operaciones de los componentes físicos del nivel inferior, y de esta manera se comprende bien en la técnica que una macroinstrucción que se ha traído de la memoria (por ejemplo, la memoria externa del sistema o 35 memoria de almacenamiento temporal) primero se debe convertir en una secuencia

correspondiente de microinstrucciones (también conocidas como “instrucciones nativas”) que cada una especifica una o más de las operaciones del nivel inferior. A continuación de esta conversión, las microinstrucciones se despachan a varias unidades de la etapa de ejecución para la ejecución, a menudo en paralelo, por las cuales se generan los resultados o se realizan las operaciones del nivel inferior 5 especificadas.

Consecuentemente, se ha dedicado a la técnica significativa atención para desarrollar mecanismos muy rápidos y eficientes para convertir las macroinstrucciones en secuencias de microinstrucciones asociadas y para despachar óptimamente las microinstrucciones a los recursos de la etapa de ejecución. Existen una pluralidad de 10 planteamientos diferentes para realizar las operaciones de conversión, pero la mayoría de los planteamientos se pueden caracterizar típicamente por una combinación de la conversión directa (es decir “traducción”) por los componentes físicos y almacenamiento indexado en una memoria solo de lectura (ROM). Los recursos directos de traducción a menudo se conocen como traductores, descodificadores, 15 lógica de traducción, y similares, y los recursos de almacenamiento indexado se conocen como ROM del microcódigo o ROM de la microinstrucción.

Por ejemplo, una macroinstrucción dada que especifica una operación muy simple puede experimentar solamente traducción directa por un traductor, y se convertirá quizás en una o dos microinstrucciones asociadas, mientras que otra 20 macroinstrucción que especifica una operación muy compleja (por ejemplo, una función trigonométrica) se puede traducir en una microinstrucción única que especifica una dirección en la ROM del microcódigo (es decir, un “punto de entrada a la ROM del microcódigo) donde está almacenada una secuencia que consta de cientos de microinstrucciones secuenciales, y donde cada una de las microinstrucciones en la 25 secuencia manda una operación de nivel inferior que se requiere para realizar la operación compleja.

Como apreciará un experto en la técnica, son las secuencias complejas de microinstrucciones que se almacenan en la ROM del microcódigo las que son más propensas al error. Como los nuevos microprocesadores están diseñados y 30 fabricados, es competencia de los arquitectos de sistemas proporcionar técnicas que permitan que estos errores sean detectados y corregidos de una manera que minimice el impacto global del cambio. Las técnicas para detectar estos errores antes de situar una pieza en producción masiva quizás sacrificarían el flujo de instrucciones y la velocidad de una pieza dada para un amplio grado de flexibilidad en el entorno de 35 laboratorio o depuración. Por ejemplo, a menudo es ventajoso proporcionar los

mecanismos para simular y probar los efectos de los cambios del microcódigo en el laboratorio en un nuevo diseño antes de hacer estos cambios en silicio. Alternativamente, la corrección de errores de microcódigo en una pieza fabricada trataría de priorizar la velocidad y el flujo de la pieza sobre la flexibilidad en términos de opciones proporcionadas para hacer las correcciones. Además, si se detectan los 5 errores de microcódigo a continuación del envío de las piezas, también es deseable proporcionar técnicas para distribuir las correcciones a los usuarios finales de una forma que los usuarios finales puedan implementar las correcciones en campo. Tales correcciones se llaman comúnmente parches, parches de microcódigo, ECs en campo (es decir, “cambios de ingeniería”), y otros términos similares. 10

Un planteamiento deseable para parches de microcódigo efectivos es sustituir simplemente, o reemplazar, una instrucción de microcódigo dada con una o más instrucciones de microcódigo sustitutas. Por consiguiente, cuando se accede a la instrucción de microcódigo dada en la ROM del microcódigo, se detecta y se sustituyen entonces sus instrucciones de microcódigo de sustitución correspondientes 15 por lo tanto. En teoría, este planteamiento es sencillo. Pero en la práctica, proporcionar los mecanismos para los parches de microcódigo es muy complejo debido a un requerimiento de que el flujo de un pieza no se afecte de manera desventajosa en su entorno de funcionamiento.

En la patente U.S. 6.438.664, McGrath y otros se tratan las ventajas y las 20 desventajas de numerosos planteamientos de parches de microcódigo para incluir traer el microcódigo de sustitución desde la memoria externa en el instante cuando se encuentra el microcódigo infractor y traerlo antes de encontrar el microcódigo infractor. Cuando se trae antes de encontrar el microcódigo infractor, el microcódigo de sustitución se almacena en una ubicación volátil y se sustituye cuando se requiere por 25 el microcódigo infractor. McGrath y otros proporcionan adicionalmente una cantidad de memoria de acceso aleatorio (RAM) en un procesador para implementar los parches del microcódigo. La RAM se carga con parches desde la memoria externa durante el funcionamiento del procesador y cuando se accede a una línea de microcódigo desde la ROM del microcódigo para el que se habilita un parche, el parche se trae entonces 30 desde la RAM y se ejecuta en lugar de la línea del microcódigo. McGrath enseña varios registros de coincidencia dentro de los que se almacenan las direcciones de la ROM del microcódigo que ha asociado parches en la RAM. Cuando se encuentra una dirección de coincidencia, entonces se pasa el control a la RAM para la sustitución. McGrath y otros además señalan que mientras que este planteamiento es ventajoso, 35 es también limitativo ya que el control de conmutación desde la ROM del microcódigo

a la RAM causa una burbuja de dos ciclos en el conducto. Es decir, los parches del microcódigo de acuerdo con la técnica expuesta por McGrath y otros se proporcionan a costa del rendimiento...

Reivindicaciones:

1. Un aparato de parches en un microprocesador, que comprende:

una pluralidad de bancos de fusibles (1202), configurada para almacenar registros de parches asociados que se emplean para parchear circuitos de estado de la máquina o microcódigo en el microprocesador o almacenar entidades de datos de 5 control asociadas que se emplean para programar circuitos de control en el microprocesador

uno o más bancos de fusibles (1202) de configuración codificados para indicar si cada uno de dicha pluralidad de bancos de fusibles se programa con uno de dichos registros de parches asociados o con una de dichas entidades de datos de control 10 asociadas; y

un controlador de grupo (1201), acoplado a dicha pluralidad de bancos de fusibles, configurado para leer dicha pluralidad de bancos de fusibles, y configurado para proporcionar dichos registros de parches asociados a un cargador de parches (311, 511, 711, 1011) o dichas entidades de datos de control asociadas a los circuitos 15 de control en el microprocesador, en donde dicho cargador de parches proporciona parches que corresponden a dichos registros de parches asociados, como se prescribió, a los mecanismos de parches objetivo designados en el microprocesador;

en donde dicho cargador de parches proporciona dichos parches a dichos mecanismos de parches objetivo designados siguiendo la transición de una señal de 20 restablecimiento del microprocesador y antes de la ejecución de las instrucciones almacenadas en una ROM del BIOS (333, 533, 733, 1033).

2. El aparato de parches según se narra en la reivindicación 1, en donde cada uno de dichos uno o más bancos de fusibles de configuración comprende una pluralidad de fusible (1203), y en donde el estado de cada uno de dicha pluralidad de 25 fusibles designa uno correspondiente de dicha pluralidad de bancos de fusibles que tiene un registro de parches o que tiene una entidad de datos de control programada allí dentro.

3. El aparato de parches según se narra en la reivindicación 1, en donde cada uno de dicha pluralidad de bancos de fusibles comprende 64 fusibles, y en donde cada 30 uno de dichos 64 fusibles corresponde a un bit en un registro de parches.

4. El aparato de parches según se narra en la reivindicación 1, en donde dicha pluralidad de bancos de fusibles se programa durante la fabricación del microprocesador.

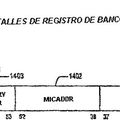

5. El aparato de parches según se narra en la reivindicación 1, en donde cada 35 uno de dichos registros de parches asociados comprende:

un campo de datos de parche (1401), para prescribir uno correspondiente de dichos parches;

un campo de direcciones de microcódigo (1402), para prescribir una dirección en el espacio de direcciones de microcódigo;

un campo de direcciones de grupo de parches (1403), para prescribir una 5 dirección en un grupo de parches; y

un campo de objetivo de parches (1406), para especificar uno de dichos mecanismos de parches designados en el microprocesador.

6. El aparato de parches según se narra en la reivindicación 1, en donde algunos de dichos parches cada uno comprende los datos de estado para el parcheo 10 de dichos circuitos de estado de la máquina dentro del microprocesador.

7. El aparato de parches según se narra en la reivindicación 1, en donde uno de dichos mecanismos de parches designados comprende un grupo de parches (312, 512, 712, 1012) dentro de una etapa de traducción del microprocesador.

8. El aparato de parches según se narra en la reivindicación 1, en donde uno 15 de dichos mecanismos de parches designados comprende una RAM de parches (551, 751, 1051) dentro de una etapa de traducción del microprocesador, dicha RAM de parches que incluye las direcciones dentro del espacio de direcciones de la ROM del microcódigo.

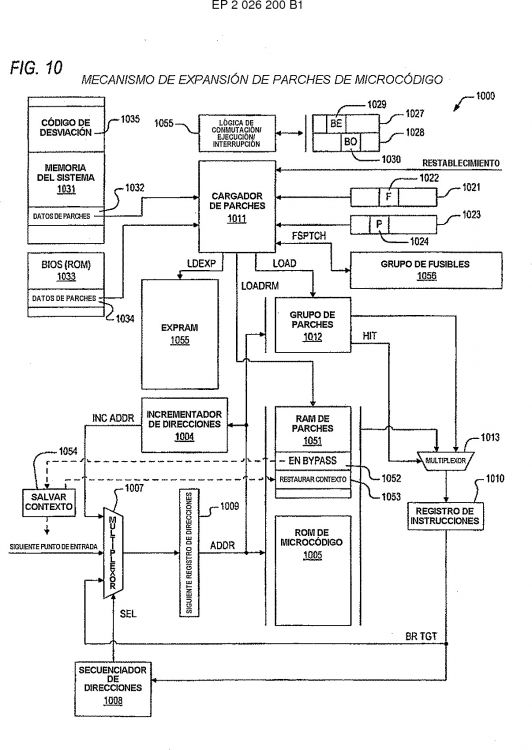

9. El aparato de parches según se narra en la reivindicación 1, en donde uno 20 de dichos mecanismos de parches designados comprende:

una RAM de expansión (1055), acoplada a una RAM de parches, configurada para almacenar dichos parches, en donde un primer uno o más de dichos parches van a ser ejecutados por el microprocesador en lugar de una correspondiente una o más microinstrucciones, y en donde un segundo uno o más de dichos parches se emplea 25 para parchear un correspondiente uno o más de dichos circuitos de estado de la máquina.

10. Un método para proporcionar selectivamente parches o datos de control durante la fabricación de un microprocesador, que comprende:

programar una pluralidad de bancos de fusibles (1202) durante la fabricación 30 del microprocesador para almacenar los registros de parches asociados que se emplean para parchear el microcódigo o los circuitos en el microprocesador, o para almacenar las entidades de datos de control asociadas que se emplean para programar los circuitos de control en el microprocesador;

codificar uno o más bancos de fusibles de configuración durante la fabricación 35 del microprocesador para indicar si cada uno de la pluralidad de bancos de fusibles se

programa con uno de los registros de parches asociados o con una de las entidades de datos de control asociadas;

seguir la transición de una señal de restablecimiento del microprocesador y antes de la ejecución de las instrucciones almacenadas en una ROM del BIOS (333, 533, 733, 1033), leer la pluralidad de bancos de fusibles y el uno o más bancos de 5 fusibles de configuración; y

proporcionar los parches que corresponden a los registros de parches asociados, como se prescribió, para los mecanismos de parche objetivo designados en el microprocesador, y programar los circuitos de control.

11. El método según se narra en la reivindicación 10, en donde cada uno del 10 uno o más bancos de fusibles de configuración comprende una pluralidad de fusibles (1203), y en donde el estado de cada uno de la pluralidad de fusibles designa uno correspondiente de la pluralidad de bancos de fusibles como que tiene un registro de parche o como que tiene una entidad de datos de control programados allí dentro.

12. El método según se narra en la reivindicación 10, en donde cada uno de la 15 pluralidad de bancos de fusibles comprende 64 fusibles, y en donde cada uno de los 64 fusibles corresponde a un bit en un registro de parches.

13. El método según se narra en la reivindicación 10, que además comprende:

especificar un grupo de parches (312, 512, 712, 1012) dentro de una etapa de traducción del microprocesador como uno de los mecanismos de parches designados. 20

14. El método según se narra en la reivindicación 10, que además comprende:

especificar una RAM de parches (551, 751, 1051) dentro de una etapa de traducción del microprocesador como uno de los mecanismos de parches designados, en donde la RAM de parches incluye las direcciones dentro del espacio de direcciones de la ROM del microcódigo. 25

15. El método según se narra en la reivindicación 10, que además comprende:

especificar una RAM de expansión (1055) como uno de los mecanismos de parches designados, en donde la RAM de expansión se configura para almacenar los parches, y en donde un primer uno o más de los parches va a ser ejecutado por el microprocesador en lugar de una correspondiente una o más microinstrucciones, y en 30 donde un segundo uno o más de los parches se emplea para parchear un correspondiente uno o más de los circuitos.

Patentes similares o relacionadas:

MECANISMO EN UN MICROPROCESADOR PARA EJECUTAR INSTRUCCIONES NATIVAS DIRECTAMENTE DESDE LA MEMORIA, del 13 de Enero de 2011, de IP-FIRST LLC: Un aparato en un microprocesador para ejecutar las instrucciones nativas que se proporcionan directamente al microprocesador a través de un canal principal […]

MECANISMO DE EXPANSIÓN DE PARCHE DE MICROCÓDIGO, del 15 de Diciembre de 2010, de VIA TECHNOLOGIES, INC.: Mecanismo de expansión de parches de microcódigo en un microprocesador, que comprende: una RAM de parches, configurada para almacenar […]

MECANISMO DE EXPANSIÓN DE PARCHE DE MICROCÓDIGO, del 15 de Diciembre de 2010, de VIA TECHNOLOGIES, INC.: Mecanismo de expansión de parches de microcódigo en un microprocesador, que comprende: una RAM de parches, configurada para almacenar […]

Microprocesador o microcontrolador potenciado, del 27 de Febrero de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un dispositivo de microprocesador de n bits que comprende: una unidad central de procesamiento de n bits (CPU); una pluralidad de registros […]

MICROPROCESADOR CON SELECCIÓN AUTOMÁTICA DE PARALELISMO SIMD, del 9 de Junio de 2011, de QUALCOMM INCORPORATED: Un procedimiento para controlar el paralelismo de operaciones en un procesador de datos en paralelo, que comprende: monitorizar una o más condiciones […]

SISTEMA DE PROCESAMIENTO DE DATOS CON EJECUCION CONDICIONAL DE INSTRUCCIONES COMPUESTAS EXTENDIDAS., del 16 de Diciembre de 2004, de MOTOROLA, INC.: Un sistema para dar órdenes a un procesador de datos, el sistema incluye una raíz de instrucción que tiene un campo de selección de operación para seleccionar […]

SISTEMA INFORMATICO., del , de COMMUNICATE LTD.: EN UN SISTEMA DE ORDENADOR CON UN PROCESADOR RISC QUE UTILIZA INSTRUCCIONES DE 32 BITS, CIERTAS INSTRUCCIONES SE ALMACENAN EN FORMA COMPRIMIDA DE 16 BITS Y SE EXPANDEN […]

MICROPROCESADOR QUE UTILIZA UN CAMPO DE INSTRUCCION PARA ESPECIFICAR FUNCIONALIDAD EXTENDIDA, del 1 de Junio de 1999, de ADVANCED MICRO DEVICES INC.: SE DESCRIBE UN MICROPROCESADOR QUE EXPANDE LA FUNCIONALIDAD O RENDIMIENTO DE UNA ARQUITECTURA IMPLEMENTADA DE MANERA TRANSPARENTE O NO TRANSPARENTE. EL […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 23 de Octubre de 2009, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 23 de Octubre de 2009, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción […]