MECANISMO DE EXPANSIÓN DE PARCHE DE MICROCÓDIGO.

Mecanismo (1000; 1100) de expansión de parches de microcódigo en un microprocesador,

que comprende: una RAM (1051; 1151) de parches, configurada para almacenar una primera pluralidad de instrucciones (1164) de parche, en la que dicha primera pluralidad de instrucciones de parche debe ser ejecutada por el microprocesador en lugar de una o más micro-instrucciones que están almacenadas en una ROM (1005; 1105) de microcódigo, caracterizado por una RAM (1055; 1155) de expansión, acoplada a dicha RAM de parches, configurada para almacenar una segunda pluralidad de instrucciones (1164, 1165, 1166) de parche, en la que el número de dicha segunda pluralidad de instrucciones de parche es mayor que el número de dicha primera pluralidad de instrucciones de parche, y en la que dicha segunda pluralidad de instrucciones de parche debe ser ejecutada por el microprocesador en lugar de una o más de entre las segundas micro-instrucciones que están almacenadas en dicha ROM de microcódigo; y un controlador (1162), acoplado a dicha RAM de parches y dicha RAM de expansión, configurado para ejecutar una micro-instrucción (1167) de EXPRAM que direcciona que la una o más de dicha segunda pluralidad de instrucciones de parche sean cargadas en dicha RAM de parches, y configurado para cargar dicha una o más de dicha segunda pluralidad de instrucciones de parche en dicha RAM de parches

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E07253293.

Solicitante: VIA TECHNOLOGIES, INC..

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: 8F, NO.535, CHUNG-CHENG ROAD HSIN-TIEN CITY TAIPEI 231 TAIWAN.

Inventor/es: PARKS,TERRY, HENRY,G. GLENN.

Fecha de Publicación: .

Fecha Solicitud PCT: 21 de Agosto de 2007.

Fecha Concesión Europea: 14 de Julio de 2010.

Clasificación Internacional de Patentes:

- G06F9/26N2

- G06F9/318T

Clasificación PCT:

- G06F9/26 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Formación de la dirección de la microinstrucción siguiente (G06F 9/28 tiene prioridad).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Mecanismo de expansión de parche de microcódigo.

Campo de la invención

Esta invención se refiere, en general, al campo de la microelectrónica, y más particularmente, a un aparato y a un procedimiento para realizar parches de microcódigo en un microprocesador.

Descripción de la técnica relacionada

Los microprocesadores actuales están diseñados para ejecutar muchas instrucciones por ciclo de reloj y proporcionan muchas características para maximizar el número de instrucciones que se ejecutan durante cualquier ciclo de reloj determinado. Un ciclo de reloj se considera, generalmente, como el intervalo de tiempo que se asigna para cada una de las etapas segmentadas en el microprocesador para realizar el trabajo de procesamiento necesario para pasar los resultados a la siguiente etapa segmentada. Y los microprocesadores actuales comprenden muchas etapas segmentadas, un número de las cuales están configuradas en paralelo, para permitir tareas de procesamiento simultáneas o concurrentes, permitiendo, de esta manera, que se ejecuten múltiples instrucciones en paralelo. Una señal reloj de núcleo es proporcionada a cada una de las etapas segmentadas con el fin de sincronizar la ejecución de instrucciones en cada una de las etapas. La señal reloj de núcleo es, frecuentemente, un múltiplo de la frecuencia de una señal de reloj de bus, la cual es proporcionada desde un circuito generador de reloj externo.

Tal como apreciará una persona con conocimientos en la técnica, las etapas principales de un microprocesador segmentado actual pueden dividirse en las asociadas con la lectura de instrucciones (es decir, lógica de etapa de lectura) desde una memoria, la traducción de las instrucciones (es decir, lógica de etapa de traducción) en secuencias asociadas de micro-instrucciones, que son únicas al microprocesador específico (es decir, "nativas del mismo"), la ejecución (es decir, lógica de etapa de ejecución) de las secuencias asociadas de micro-instrucciones, y la escritura (por ejemplo, lógica de etapa de reescritura) de los resultados de las ejecuciones a posiciones designadas.

Las etapas de lectura y traducción, indicadas anteriormente, se describen dentro del contexto de un ordenador de conjunto de instrucciones complejas (CISC) actual, que emplea macro-instrucciones, tales como las exhibidas por la arquitectura de conjunto de instrucciones x86 (ISA), omnipresente. Se emplea una única macro-instrucción para especificar un número de operaciones de hardware de nivel inferior, y, de esta manera, es bien comprendido en la materia que una macro-instrucción que ha sido leída desde memoria (por ejemplo, una memoria de sistema externa o memoria caché) debe ser convertida primero a una secuencia correspondiente de micro-instrucciones (conocidas también como "instrucciones nativas") que especifican, cada una, una o más operaciones del nivel inferior. Después de esta conversión, las micro-instrucciones son enviadas a varias unidades de la etapa de ejecución para su ejecución, frecuentemente en paralelo, donde los resultados son generados o las operaciones de nivel inferior especificadas son realizadas.

Consecuentemente, se ha dedicado una atención considerable en la técnica al desarrollo de mecanismos muy rápidos y eficientes para convertir las macro-instrucciones en las secuencias de micro-instrucciones asociadas y para enviar, de manera óptima, la micro-instrucciones a los recursos de la etapa de ejecución. Un número de enfoques diferentes existen para realizar las operaciones de conversión, pero la mayoría de los enfoques pueden caracterizarse, típicamente, por una combinación de conversión directa (es decir, "traducción") por hardware y almacenamiento indexado en una memoria de solo lectura (ROM). Los recursos de traducción directa son referidos, frecuentemente, como traductores, decodificadores, lógica de traducción, y similares, y los recursos de almacenamiento indexado son referidos como ROM de microcódigo y ROM de micro-instrucciones.

Por ejemplo, una macro-instrucción determinada, que especifica una operación muy simple, puede ser sometida solo a una traducción directa por medio de un traductor, y será convertida en quizás una o dos micro-instrucciones asociadas, mientras que otra macro-instrucción, que especifica una operación muy compleja, (por ejemplo, una función trigonométrica) puede ser traducida en una única micro-instrucción que especifica una dirección en la ROM de microcódigo (es decir, un "punto de entrada en la ROM de microcódigo"), donde está almacenada una secuencia que comprende cientos de micro-instrucciones secuenciales, y donde cada una de las micro-instrucciones en la secuencia determina una operación de nivel inferior que es requerida para realizar la operación compleja.

Tal como apreciará una persona con conocimientos en la técnica, son las secuencias complejas de micro-instrucciones las que están almacenadas en la ROM de microcódigo, las que son más propensas a errores. Conforme se diseñan y fabrican nuevos microprocesadores, es de la incumbencia de los arquitectos de sistemas proporcionar técnicas que permitan que estos errores sean detectados y corregidos en una manera que minimice el impacto global del cambio. Las técnicas para detectar estos errores previamente a la colocación de una parte en producción en masa sacrificarían, quizás, la capacidad de procesamiento de instrucciones y la velocidad de una parte determinada por un amplio grado de flexibilidad en el entorno de laboratorio o de depuración. Por ejemplo, es frecuentemente ventajoso proporcionar mecanismos para simular y ensayar los efectos de cambios de microcódigos en el laboratorio sobre un nuevo diseño previamente a plasmar estos cambios en silicio. Como alternativa, la corrección de errores de microcódigo en una parte fabricada buscaría priorizar la velocidad y la capacidad de procesamiento de la parte sobre la flexibilidad, en términos de opciones proporcionadas para realizar las correcciones. Además, si los errores de microcódigo son detectados tras el envío de las partes, es deseable, también, proporcionar técnicas para distribuir las correcciones a los usuarios finales en una manera en la que los usuarios puedan implementar las correcciones in situ. Dichas correcciones se denominan comúnmente parches, parches de microcódigo, ECs de campo (es decir, "cambios de ingeniería") y otros términos similares.

Un enfoque deseable para efectuar los parches de microcódigo es simplemente sustituir o reemplazar una instrucción de microcódigo determinada con una o más instrucciones de microcódigo sustitutas. Por consiguiente, cuando la instrucción de microcódigo determinada es accedida en la ROM de microcódigo, es detectada y sus instrucciones de microcódigo de reemplazo correspondientes son sustituidas, a continuación, por la misma. En teoría, este enfoque es directo. Pero en la práctica, la provisión de mecanismos para los parches de microcódigo es muy compleja debido a un requerimiento de que la capacidad de procesamiento de una parte no se vea afectada, de manera desventajosa, en su entorno de funcionamiento.

En la patente US 6.438.664, McGrath et al., exponen la ventajas y las desventajas de numerosos enfoques de parches de microcódigo para incluir la lectura del microcódigo de reemplazo desde una memoria externa en el momento en el que el microcódigo causante del conflicto es encontrado y la lectura antes de encontrar el microcódigo causante del conflicto. Cuando es leído antes de encontrar el microcódigo causante del conflicto, el microcódigo de reemplazo es almacenado en una posición volátil y es sustituido por el microcódigo causante del conflicto cuando se requiera. McGrath et al., proporcionan adicionalmente, una cantidad de memoria de acceso aleatorio (RAM) en un procesador para implementar parches de microcódigo. La RAM es cargada con parches desde una memoria externa durante el funcionamiento del microprocesador y cuando se accede a una línea de microcódigo desde la ROM de microcódigo, para la cual hay un parche habilitado, a continuación, el parche es leído desde la RAM y es ejecutado en vez de la línea de microcódigo. McGrath divulga varios registros de coincidencia dentro de los cuales están almacenadas las direcciones de la ROM de microcódigo que tienen parches asociados en RAM. Cuando se encuentra una dirección coincidente, el control es pasado, a continuación, a la RAM para una sustitución. MacGrath et al., indican además que aunque este enfoque es ventajoso, es también limitativo en el sentido que la...

Reivindicaciones:

1. Mecanismo (1000; 1100) de expansión de parches de microcódigo en un microprocesador, que comprende:

una RAM (1051; 1151) de parches, configurada para almacenar una primera pluralidad de instrucciones (1164) de parche, en la que dicha primera pluralidad de instrucciones de parche debe ser ejecutada por el microprocesador en lugar de una o más micro-instrucciones que están almacenadas en una ROM (1005; 1105) de microcódigo, caracterizado por

una RAM (1055; 1155) de expansión, acoplada a dicha RAM de parches, configurada para almacenar una segunda pluralidad de instrucciones (1164, 1165, 1166) de parche, en la que el número de dicha segunda pluralidad de instrucciones de parche es mayor que el número de dicha primera pluralidad de instrucciones de parche, y en la que dicha segunda pluralidad de instrucciones de parche debe ser ejecutada por el microprocesador en lugar de una o más de entre las segundas micro-instrucciones que están almacenadas en dicha ROM de microcódigo; y

un controlador (1162), acoplado a dicha RAM de parches y dicha RAM de expansión, configurado para ejecutar una micro-instrucción (1167) de EXPRAM que direcciona que la una o más de dicha segunda pluralidad de instrucciones de parche sean cargadas en dicha RAM de parches, y configurado para cargar dicha una o más de dicha segunda pluralidad de instrucciones de parche en dicha RAM de parches.

2. Mecanismo según se ha indicado en la reivindicación 1, en el que dicha micro-instrucción (1167) de EXPRAM es proporcionada por dicha ROM (1105) de microcódigo para su ejecución.

3. Mecanismo según se ha indicado en la reivindicación 1, en el que dicha micro-instrucción (1167) de EXPRAM es proporcionada por dicha RAM (1151) de parches para su ejecución.

4. Mecanismo según se ha indicado en la reivindicación 1, en el que dicha instrucción de EXPRAM direcciona que dicha una o más de dicha segunda pluralidad de instrucciones de parche sean intercambiadas con una o más de dicha pluralidad de instrucciones de parche correspondientes.

5. Mecanismo según se ha indicado en la reivindicación 1, en el que cada una de entre dicha una o más micro-instrucciones comprende una o más instrucciones específicas de máquina.

6. Mecanismo según se ha indicado en la reivindicación 1, en el que cada una de entre dicha una o más micro-instrucciones comprende y codifica una pluralidad de instrucciones específicas de máquina.

7. Mecanismo según se ha indicado en la reivindicación 1, que comprende además:

un cargador (1011) de parches; acoplado operativamente a una memoria (1031) de sistema y a una BIOS ROM (1033), configurado para recuperar dichas primera y segunda pluralidad de instrucciones de parche desde dicha memoria de sistema, y configurado para cargar dicha primera pluralidad de instrucciones de parche en dicha RAM de parches y dicha segunda pluralidad de instrucciones de parche en dicha RAM de expansión.

8. Mecanismo según se ha indicado en la reivindicación 7, en el que dicho cargador de parches carga dichas primera y segunda pluralidad de instrucciones de parche después de una transición de una señal de reinicialización de microprocesador y previamente a la ejecución de las instrucciones almacenadas en dicha BIOS ROM, y en el que dichas primera y segunda pluralidad de instrucciones de parche están almacenadas en dicha BIOS ROM.

9. Mecanismo según se ha indicado en la reivindicación 7, en el que dicho cargador de parches carga dichas primera y segunda pluralidad de instrucciones de parche en base a la ejecución de instrucciones privilegiadas del sistema operativo que son ejecutadas en base al estado de un bit de parches dentro de un registro específico de máquina.

10. Mecanismo según se ha indicado en la reivindicación 1, en el que dicha RAM de expansión está configurada también para almacenar datos (1168) correspondientes al estado del microprocesador.

11. Mecanismo según se ha indicado en la reivindicación 1, en el que dicha RAM de expansión comprende un banco de 4K de RAM dentro de una caché integrada, y en el que dicho banco de 4K puede ser accedido solo mediante la ejecución de microcódigo por el microprocesador.

12. Procedimiento para expandir la capacidad de un mecanismo (1000; 1100) de parches de microcódigo en un microprocesador, que comprende:

proporcionar un primer parche (1164) de microcódigo en una RAM (1051; 1151) de parches dentro de un espacio de direcciones de microcódigo, y, subsiguientemente, ejecutar el primer parche de microcódigo en lugar de una primera micro-instrucción almacenada en la ROM (1005; 1105) de microcódigo, caracterizado porque

en respuesta a la ejecución de una instrucción (1167) de EXPRAM, se transfiere un segundo parche (1165, 1166) de microcódigo desde una RAM (1155) de expansión a la RAM de parches, en el que la RAM de expansión está configurada para almacenar un mayor número de instrucciones de parche que la RAM de parches; y

ejecutar el segundo parche de microcódigo en lugar de una segunda micro-instrucción almacenada en la ROM de microcódigo.

13. Procedimiento según se ha indicado en la reivindicación 12, en el que dicha trasferencia comprende intercambiar el primer parche de microcódigo con el segundo parche de microcódigo.

14. Procedimiento según se ha indicado en la reivindicación 12, en el que la primera micro-instrucción comprende una o más instrucciones específicas de máquina.

15. Procedimiento según se ha indicado en la reivindicación 12, en el que la primera micro-instrucción comprende una codificación de una pluralidad de instrucciones específicas de máquina.

16. Procedimiento según se ha indicado en la reivindicación 12, que comprende además:

recuperar el primer parche de microcódigo y el segundo parche de microcódigo desde una memoria (1031) de sistema y cargar el primer parche de microcódigo en la RAM de parches y cargar el segundo parche de microcódigo en la RAM de expansión.

17. Procedimiento según se ha indicado en la reivindicación 12, que comprende además:

después de una transición de una señal de reinicialización de microprocesador y previamente a la ejecución de las instrucciones almacenadas en BIOS ROM (1033), recuperar el primer parche de microcódigo y el segundo parche de microcódigo desde la BIOS ROM y cargar el primer parche de microcódigo en la RAM de parches y cargar el segundo parche de microcódigo en la RAM de expansión.

Patentes similares o relacionadas:

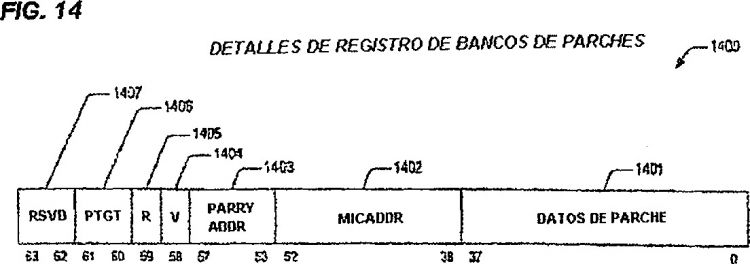

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

MECANISMO EN UN MICROPROCESADOR PARA EJECUTAR INSTRUCCIONES NATIVAS DIRECTAMENTE DESDE LA MEMORIA, del 13 de Enero de 2011, de IP-FIRST LLC: Un aparato en un microprocesador para ejecutar las instrucciones nativas que se proporcionan directamente al microprocesador a través de un canal principal […]

MÉTODO Y DISPOSITIVO PARA LA ACTUALIZACIÓN EFICIENTE DE DATOS EN DISPOSITIVOS ELECTRÓNICOS, del 21 de Mayo de 2015, de UNIVERSIDAD DE CANTABRIA: Método y dispositivo para la actualización eficiente de datos en dispositivos electrónicos que resuelve de manera simple, los problemas que presentan […]

MÉTODO Y DISPOSITIVO PARA LA ACTUALIZACIÓN EFICIENTE DE DATOS EN DISPOSITIVOS ELECTRÓNICOS, del 21 de Mayo de 2015, de UNIVERSIDAD DE CANTABRIA: Método y dispositivo para la actualización eficiente de datos en dispositivos electrónicos que resuelve de manera simple, los problemas que presentan […]

SISTEMA PARA CONTROL DE PROCESADOR., del 1 de Noviembre de 2002, de NOKIA MOBILE PHONES LTD.: UN APARATO CONTROLADO POR ORDENADOR INCLUYE UN CONTADOR DE PROGRAMA PARA MANIFESTAR LOS VALORES DE COMPUTO DEL PROGRAMA Y UN PROCESADOR PARA EJECUTAR UN PROGRAMA PREALMACENADO […]

SISTEMA DE CONTROL DE LECTURA DE MICROCODIGO., del 1 de Marzo de 1995, de FUJITSU LIMITED: SISTEMA DE CONTROL DE LECTURA DE MICROCODIGO EN EQUIPO DE PROCESAMIENTO DE INFORMACION EN EL QUE UNA INSTRUCCION DE MAQUINA SE DIVIDE EN MICROCODIGOS COMO VARIAS […]

UN SISTEMA MICROPROGRAMABLE, del 1 de Noviembre de 1987, de HONEYWELL INFORMATION SYSTEMS INC.: SISTEMA ELECTRONICO DEL PROCESO DE DATOS. INCLUYE: UN MICROPROCESADOR CON UN REGISTRADOR DE DATOS , UN DESCODIFICADOR DE OPERACIONES Y UNA LOGICA DE […]

PERFECCIONAMIENTOS EN UNA INSTALACION DE TRATAMIENTO DE DATOS, del 1 de Diciembre de 1982, de ATARI,INC.: INSTALACION DE TRATAMIENTO DE DATOS. CONSTA DE UN ELEMENTO DE ALMACENAMIENTO PROVISIONAL CON CIRCUITOS DE ENTRADA ACOPLADOS CON UN CIERTO NUMERO DE LINEAS DE SEÑALES DE INTERCONEXION […]