REGISTRO DINÁMICO CON CANAL P ACELERADO.

Un registro dinámico no inversor (1000; 1100), caracterizado por:

una etapa dominó (1002, N1, P1), configurada para evaluar una función lógica basada en al menos una señal de datos de entrada (DATAB) y una señal de reloj pulsatoria (PLSCLKB), en la que dicha etapa dominó descarga previamente un nodo (1005) descargado previamente bajo cuando dicha señal de reloj pulsatoria es alta y abre una ventana de evaluación cuando dicha señal de reloj pulsatoria adopta un valor bajo, y lleva dicho nodo (1005) a un valor alto descargado previamente si dicha etapa de dominó evalúa, y mantiene dicho nodo descargado previo bajo si dicha etapa de dominó falla al evaluar; un multiplexador (U7), acoplado a dicha etapa dominó, configurada para responder a dicha señal de reloj pulsatoria y dicho nodo descargado previo, que lleva un nodo de realimentación (1011) a un valor alto si dicho nodo (1005) descargado previamente adopta un valor alto durante dicha ventana de evaluación, y que lleva dicho nodo (1011) de realimentación a un valor bajo si dicho nodo (1005) descargado previamente está bajo durante dicha ventana de evaluación, y que recibe una señal de realimentación retrasada (1009) que tiene el mismo estado que dicho nodo de realimentación (1011), pero retrasado en el tiempo, en el que dicha señal de realimentación retrasada (1009) es seleccionada cuando dicha señal de reloj pulsatoria adopta un valor alto; y una etapa de salida (1013), acoplada a dicho nodo (1005) descargado previamente y dicho nodo de realimentación (1011), configurado para proporcionar una señal de salida (QB) basada en estados de dichos nodos descargados previamente y dichos nodos de realimentación (1005, 1011).

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E06254819.

Solicitante: VIA TECHNOLOGIES, INC..

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: 8F, 535 CHUNG-CHENG ROAD HSIN-TIEN, TAIPEI 231, TAIWAN R.O.C. TAIWAN.

Inventor/es: BERTRAM,RAYMOND A, Lundberg,James R.

Fecha de Publicación: .

Fecha Solicitud PCT: 15 de Septiembre de 2006.

Clasificación PCT:

- G11C19/00 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › Memorias digitales en las que la información es movida por escalones, p. ej. registros de desplazamiento.

- H03K19/00 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión.

- H03K3/00 H03K […] › Circuitos para la generación de impulsos eléctricos; Circuitos monoestables, biestables o multiestables (H03K 4/00 tiene prioridad; para generadores de funciones digitales en ordenadores G06F 1/02).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

PDF original: ES-2366916_T3.pdf

Fragmento de la descripción:

ANTECEDENTES DEL INVENTO

CAMPO DEL INVENTO El presente invento se refiere a funciones lógicas y de registros dinámicas, y más particularmente a un registro de salida dominó P con una carga acelerada y trayectos sin carga para registrar las salidas de circuitos lógicos complejos donde la velocidad y el tamaño son factores importantes.

DESCRIPCIÓN DE LA TÉCNICA RELACIONADA Los circuitos integrados usan un número notable de registros, particularmente los que tienen una arquitectura segmentada síncrona. El registro lógico es empleado para retener las salidas de dispositivos y circuitos durante un periodo de tiempo de manera que estas salidas puedan ser recibidas por otros dispositivos y circuitos. En un sistema temporizado, tal como un microprocesador segmentado, los registros son utilizados para enganchar y retener las salidas de una etapa segmentada dada durante un periodo de un ciclo de reloj de manera que los circuitos de entrada en una etapa subsiguiente puedan recibir las salidas durante ese período mientras la etapa segmentada dada está generando al mismo tiempo nuevas salidas.

En el pasado, ha sido la práctica común preceder y hacer seguir a circuitos de evaluación lógica complejos, tales como multiplexadores de múltiples entradas (multiplexadores), codificadores multi-bits, etc., con registros para contener las entradas a los circuitos de evaluación y las salidas desde los mismos. Generalmente, estos registros tienen requisitos de configuración y tiempo de retención asociados, los cuales restringen los circuitos de evaluación en la etapa precedente. Además, los registros tienen características de tiempo de datos para salida correspondientes, que restringen los circuitos de evaluación en la etapa subsiguiente. La "velocidad" de un registro es juzgada típicamente en términos de su tiempo de datos para salida, es decir, la suma de su tiempo de configuración y tiempo de reloj para salida.

Preceder y seguir un circuito de evaluación lógica con circuitos de registro tradicionales introduce retrasos en un sistema segmentado cuyo efecto acumulativo da como resultado velocidades de funcionamiento significativamente más lentas. Más específicamente, una fuente notable de estos retrasos son los requisitos de tiempo de datos para salida que deben ser satisfechos por circuitos de evaluación lógica con el fin de asegurar salidas registradas estables. Se desea reducir estos retrasos para proporcionar tiempo adicional en cada etapa y aumentar por ello la velocidad total del sistema segmentado.

La publicación de Solicitud de Patente Norteamericana nº 2005/0127952A1, titulada "Registro Dominó No Inversor", está dirigida a los problemas descritos antes. En la exposición anterior, se ha descrito un registro dominó no inversor que combinaba funciones de evaluación lógica con sus registros correspondientes para conseguir un tiempo de reloj para salida más rápido que las aproximaciones convencionales sin comprometer la estabilidad de su salida. Las transiciones de la señal de salida del registro dominó no inversor expuestas en él fueron mostradas como muy rápidas en respuesta a transiciones de la señal de reloj en contraste con respuestas de transición más lentas de registros dominó de inversión convencional. El registro dominó no inversor anterior, fue también flexible con respecto a la configuración de la evaluación lógica, que podría ser proporcionada como lógica de canal N, lógica de canal P, o una combinación de ambas.

En la publicación de Solicitud de Patente Norteamericana nº 2006/0038589A1, titulada "Registro Dominó P”, se ha expuesto una versión de canal P del registro dominó no inversor.

Tanto las versiones de canal N como las de canal P del registro dominó no inversor proporcionan ventajas de velocidad significativas cuando las entradas de datos hacen que el registro no inversor descargue un nodo precargado o cargue un nodo descargado en él cuando es temporizado. Pero los actuales inventores han observado un deseo de disminuir el tiempo de reloj para salida tanto para las versiones de canal P como para las de canal N del registro dominó no inversor cuando las entradas de datos son tales que el nodo precargado no descarga o el nodo previamente descargado no carga cuando es temporizado.

Consiguientemente, se desea proporcionar registros dominó N y dominó P mejorados con trayectos acelerados que proporcionan todos los beneficios de los registros dominó no inversor anteriores, y que son además flexibles con respecto a la etapa dominó, y que son además óptimos para utilizar en un entorno de fuga elevada o de ruido elevado.

SUMARIO DEL INVENTO

En una realización, se proporciona un registro dinámico no inversor. El registro dinámico no inversor incluye una etapa dominó, un multiplexador, y una etapa de salida. La etapa dominó está configurada para evaluar una función lógica basada en al menos una señal de datos de entrada y una señal de reloj pulsatoria, en que la etapa dominó descarga previamente un nodo previamente descargado bajo cuando la señal de reloj pulsatoria es alta y abre una ventana de evaluación cuando la señal de reloj pulsatoria adopta un valor bajo, y lleva a un valor alto el nodo previamente descargado si la etapa dominó evalúa, y conserva el nodo previamente descargado bajo si la etapa de dominó falla al evaluar. El multiplexador está acoplado a la etapa dominó. El multiplexador responde a la señal de reloj pulsatoria y al nodo previamente descargado. El multiplexador lleva a un valor alto un nodo de realimentación si el nodo previamente descargado adopta un valor alto durante la ventana de evaluación, y lleva el nodo de realimentación a un valor bajo si el nodo previamente descargado está bajo durante la ventana de evaluación. El multiplexador recibe una señal de realimentación retrasada que tiene el mismo estado que el nodo de realimentación, pero retrasado en el tiempo, en el que la señal de realimentación retrasada es seleccionada cuando la señal de reloj pulsatoria adopta un valor alto. La etapa de salida está acoplada al nodo previamente descargado y al nodo de realimentación. La etapa de salida proporciona una señal de salida basada en los estados de los nodos, previamente descargado y de realimentación.

En otra realización, se proporciona un método de registrar una función lógica y generar una salida no invertida. El método incluye descargar previamente un primer nodo bajo mientras una señal de reloj pulsatoria está alta; evaluar una función lógica para controlar el estado del primer nodo cuando la señal de reloj pulsatoria adopta un valor bajo, comprendiendo dicha evaluación: llevar un primer nodo a un valor alto cuando la función lógica evalúa y conservar el primer nodo bajo cuando la función lógica falla al evaluar; en primer lugar controlar el estado de un segundo nodo con un primer estado retrasado del primer nodo cuando la señal de reloj pulsatoria adopta un valor bajo, comprendiendo dicho primer control: en primer lugar seleccionar el primer estado retrasado del primer nodo como una salida de un multiplexador, en el que la salida está acoplada al segundo nodo; en segundo lugar controlar el estado del segundo nodo con un segundo estado retrasado del segundo nodo cuando la señal de reloj pulsatoria adopta un valor alto; y determinar el estado de un nodo de salida basado en los estados del primer y segundo nodos.

Los beneficios, características y ventajas del presente invento resultarán mejor comprendidos con relación a la siguiente descripción, y a los dibujos adjuntos en los que:

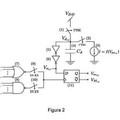

La fig. 1 es un diagrama esquemático de un registro dominó N no inversor puesto en práctica de acuerdo con una exposición anterior que está incorporada como referencia; La fig. 2 es un diagrama de tiempo que ilustra el funcionamiento del registro dominó N no inversor de las figs. 1, 3-4, y 5; La fig. 3 es un diagrama esquemático de un registro dominó N no inversor puesto en práctica de acuerdo con una realización alternativa del registro de la fig. 1; La fig. 4 es un diagrama esquemático de otro registro dominó N no inversor que exhibe una etapa de almacenamiento mejorado; La fig. 5 es un diagrama esquemático de un registro dominó N no inversor que emplea la etapa de almacenamiento mejorado y puesto en práctica de acuerdo con una realización alternativa del registro de la fig. 4; La fig. 6 es un diagrama de tiempo que ilustra el funcionamiento de los registros dominó N no inversor de la figs. 1, 3-4, y 5 de acuerdo con una realización de reloj pulsatorio que es preferida para minimizar... [Seguir leyendo]

Reivindicaciones:

1. Un registro dinámico no inversor (1000; 1100), caracterizado por:

una etapa dominó (1002, N1, P1), configurada para evaluar una función lógica basada en al menos una señal de datos de entrada (DATAB) y una señal de reloj pulsatoria (PLSCLKB), en la que dicha etapa dominó descarga previamente un nodo (1005) descargado previamente bajo cuando dicha señal de reloj pulsatoria es alta y abre una ventana de evaluación cuando dicha señal de reloj pulsatoria adopta un valor bajo, y lleva dicho nodo (1005) a un valor alto descargado previamente si dicha etapa de dominó evalúa, y mantiene dicho nodo descargado previo bajo si dicha etapa de dominó falla al evaluar; un multiplexador (U7), acoplado a dicha etapa dominó, configurada para responder a dicha señal de reloj pulsatoria y dicho nodo descargado previo, que lleva un nodo de realimentación (1011) a un valor alto si dicho nodo (1005) descargado previamente adopta un valor alto durante dicha ventana de evaluación, y que lleva dicho nodo (1011) de realimentación a un valor bajo si dicho nodo (1005) descargado previamente está bajo durante dicha ventana de evaluación, y que recibe una señal de realimentación retrasada (1009) que tiene el mismo estado que dicho nodo de realimentación (1011), pero retrasado en el tiempo, en el que dicha señal de realimentación retrasada (1009) es seleccionada cuando dicha señal de reloj pulsatoria adopta un valor alto; y una etapa de salida (1013), acoplada a dicho nodo (1005) descargado previamente y dicho nodo de realimentación (1011), configurado para proporcionar una señal de salida (QB) basada en estados de dichos nodos descargados previamente y dichos nodos de realimentación (1005, 1011).

2. El registro dinámico no inversor según la reivindicación 1, en el que dicha etapa dominó comprende:

un dispositivo (N1) de canal N que tiene una puerta que recibe dicha señal de reloj pulsatoria, y un drenaje y fuente acoplados entre tierra y dicho nodo (1005) descargado previamente; un dispositivo (P1) de canal P que tiene una puerta que recibe dicha señal de reloj pulsatoria, un drenaje acoplado a dicho nodo (1005) descargado previamente, y una fuente; y lógica de evaluación (1002) acoplada entre una fuente de tensión (VDD) y dicha fuente de dicho dispositivo (P1) de canal P.

3. Un registro dinámico no inversor según la reivindicación 2, en el que dicha lógica de evaluación (1002) comprende una lógica de semiconductor de óxido metálico complementaria.

4. El registro dinámico no inversor según la reivindicación 1, que comprende además: una primera lógica de retardo (U2, U4), acoplada a dicho nodo (1005) descargado previamente y una primera entrada (I1) de dicho multiplexador (U7), configurada para generar una primera señal retrasada (TP1) que tiene el mismo estado que dicho nodo (1005) descargado previamente, pero retrasado en el tiempo.

5. El registro dinámico no inversor según la reivindicación 4, que comprende además:

una segunda lógica de retardo (U5, U6), acoplada a dicho nodo de realimentación (1011) y una segunda entrada (I2) de dicho multiplexador (U7), configurada para generar dicha señal de realimentación retrasada (FB1).

6. El registro dinámico no inversor según la reivindicación 1, en el que dicha señal de reloj pulsatoria (PLSCLKB) es acoplada a una primera entrada seleccionada (S1) de dicho multiplexador (U7), y en el que una versión invertida de dicha señal de reloj pulsatoria (PLSCLK) es acoplada a una segunda entrada seleccionada (S2) de dicho multiplexador.

7. El registro dinámico no inversor según la reivindicación 1, en el que dicha etapa de salida (1013) comprende una puerta NOR.

8. El registro dinámico no inversor según la reivindicación 1, en el que dicha etapa dominó, dicho multiplexador, y dicha etapa de salida son fabricados usando un proceso de silicio sobre aislante de 90 nanómetros a escala.

9. Un método para registrar una función lógica y generar una salida no invertida, caracterizado por las operaciones de:

descargar previamente un primer nodo bajo mientras una señal de reloj pulsatoria es alta; evaluar una función lógica para controlar el estado del primer nodo cuando la señal de reloj pulsatoria adopta un valor bajo, comprendiendo dicha evaluación:

llevar el primer nodo a un valor alto cuando la función lógica evalúa y mantiene el primer nodo bajo cuando la función lógica falla al evaluar;

controlar en primer lugar el estado de un segundo nodo con un primer estado retrasado del primer nodo cuando la señal de reloj pulsatoria adopta un valor bajo, comprendiendo dicho primer controlador:

5 seleccionar en primer lugar el primer estado retrasado del primer nodo como una salida de un multiplexador, en el que la salida está acoplada al segundo nodo;

en segundo lugar controlar el estado del segundo nodo con un segundo estado retrasado del segundo nodo 10 cuando la señal de reloj pulsatoria asciende; y determinar el estado de un nodo de salida en base a los estados del primer y segundo nodos.

10. El método según la reivindicación 9, en el que dicho segundo control comprende: en segundo lugar seleccionar el segundo estado retrasado del segundo nodo como la salida del multiplexador.

11. El método según la reivindicación 9, en el que dicha determinación del estado de un nodo de salida comprende

lógicamente combinar los estados del primer y segundo nodos con una función NOR. 20

Patentes similares o relacionadas:

Sistema y procedimiento de control de distribución de energía de un circuito integrado, del 6 de Mayo de 2020, de QUALCOMM INCORPORATED: Un circuito integrado de administración de energía que comprende: un primer pin para suministrar energía a un primer dominio de energía de un dispositivo […]

Aplicación de un lenguaje cuaternario para ordenador, del 14 de Febrero de 2017, de PORRAS VILA,F. JAVIER: La aplicación de un lenguaje cuaternario para ordenador, es un sistema básico de hardware que cada letra del teclado de un ordenador, multiplicará por cuatro para significar […]

Un labio de cuchara para una excavadora, del 7 de Septiembre de 2016, de ESCO CORPORATION: Un labio de cuchara que comprende: Una cara interior posicionada dentro de una cavidad de recogida de tierra de una cuchara de excavadora; Una cara […]

Conjunto de desgaste para el borde de excavación de una excavadora, del 8 de Junio de 2016, de ESCO CORPORATION: Un elemento de desgaste para acoplarse a lo largo del labio de una cuchara, comprendiendo el elemento de desgaste : Un extremo de trabajo frontal ; […]

Dispositivo para interconexionar una línea de bus bidireccional de tipo I2C, del 21 de Enero de 2015, de INDESIT COMPANY S.P.A.: Dispositivo para la interconexión a una línea de bus bidireccional de tipo IIC, que comprende: - una primera patilla (IIC_uC) adaptada para ser conectada […]

Dispositivo para la detección Hardware de extremos locales en una imagen, del 12 de Mayo de 2014, de UNIVERSIDAD DE SEVILLA: Dispositivo y método para la detección hardware de extremos locales en una imagen que comprende una pluralidad de celdas elementales de procesamiento de señal mixta interconectadas […]

Dispositivo para la detección Hardware de extremos locales en una imagen, del 12 de Mayo de 2014, de UNIVERSIDAD DE SEVILLA: Dispositivo y método para la detección hardware de extremos locales en una imagen que comprende una pluralidad de celdas elementales de procesamiento de señal mixta interconectadas […]

Conjunto de desgaste para el borde de excavación de una excavadora, del 1 de Octubre de 2013, de ESCO CORPORATION: Un conjunto de desgaste para unión a un labio de excavación de una excavadora en donde el labio incluye un borde de excavación frontal […]

DISPOSITIVO LOGICO MAGNETICO QUE TIENE PUNTOS CUANTICOS MAGNETICOS., del 16 de Noviembre de 2006, de CAMBRIDGE UNIVERSITY TECHNICAL SERVICES LIMITED: Un dispositivo lógico formado al menos de una cadena de puntos de material magnético, teniendo cada punto una anchura de entre 10 nm y 200 nm y estando separado […]