Registro dinámico de canal N acelerado.

Registro dinámico, de canal N, no inversor, que comprende:

una etapa dominó,

para evaluar una función lógica en base a al menos una señal de datos de entrada y una señal de reloj a impulsos, en el que dicha etapa dominó precarga un nodo precargado a alto cuando dicha señal de reloj a impulsos está baja y abre una ventana de evaluación cuando dicha señal de reloj a impulsos sube, y baja dicho nodo precargado si evalúa, y mantiene dicho nodo precargado alto si no evalúa;

un mux, acoplado a la etapa dominó, que responde a dicha señal de reloj a impulsos y a dicho nodo precargado, que baja un nodo de retroalimentación si dicho nodo precargado baja durante dicha la ventana de evaluación, y que sube dicho nodo de retroalimentación si dicho nodo precargado está alto durante dicha ventana de evaluación, y que recibe una señal de retroalimentación retrasada que tiene el mismo estado que dicho nodo de retroalimentación, pero retrasado en el tiempo, en el que la señal de retroalimentación retrasada es seleccionada cuando dicha señal de reloj a impulsos baja; y

una etapa de salida, acoplada a dicho nodo precargado y dicho nodo de retroalimentación, que proporciona una señal de salida en base a los estados de dicho nodo precargado y dicho nodo de retroalimentación.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E06254807.

Solicitante: VIA TECHNOLOGIES, INC..

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: 8F, No. 535, Chung-Cheng Road Hsin-Tien City Taipei Hsien 231 TAIWAN.

Inventor/es: BERTRAM,RAYMOND A, Lundberg,James R.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K19/096 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › Circuitos síncronos, es decir, circuitos que utilizan señales de reloj.

PDF original: ES-2377031_T3.pdf

Fragmento de la descripción:

Registro dinámico de canal N acelerado.

Esta solicitud está relacionada con las siguientes solicitudes de patente US, cada una con un cesionario común e inventores comunes.

NÚMERO DE SERIE FECHA DE PRESENTACIÓN TÍTULO 10/640369 (CNTR.2200) 13/08/2003 NON-INVERTING DOMINO REGISTER 11/023145 (CNTR.2200-CP1) 27/12/2004 NON-INVERTING DOMINO REGISTER 11/251517 (CNTR.2241) 14/10/2005 N-DOMINIO OUTPUT LATCH (US2006/0033534) 11/251399 (CNTR.2242) 14/10/2005 P-DOMINO OUTPUT LATCH 11/424756 (CNTR-2287) 16/06/2006 N-DOMINO REGISTER WITH ACCELERATED NON-DISCHARGE PATH 11/424762 (CNTR. 2298) 16/06/2006 P-DOMINO REGISTER WITH ACCELERATED NON-CHARGE PATH 11/251384 (CNTR. 2299) 14/10//2005 P-DOMINO REGISTER (CNTR. 2324) 11/08/2006 ACCELERATED P-CHANNEL DYNAMIC REGISTERANTECEDENTES DE LA INVENCIÓN

CAMPO DE LA INVENCIÓN

La presente invención se refiere a funciones de registro y lógica dinámica, y más particularmente a un registro de salida, de tipo dominó N, con caminos acelerados de descarga y no descarga, para registrar las salidas de circuitos lógicos complejos, en los que la velocidad y el tamaño son factores importantes.

DESCRIPCIÓN DE LA TÉCNICA RELACIONADA

Los circuitos integrados usan un número considerable de registros, particularmente, los que tienen una arquitectura canalizada síncrona. La lógica de registro se emplea para mantener las salidas de los dispositivos y circuitos durante un periodo de tiempo, de manera que estas salidas puedan ser recibidas por otros dispositivos y circuitos. En un sistema sincronizado, tal como un microprocesador canalizado, los registros se usan para enclavar y mantener las salidas de una etapa de canalización determinada durante un periodo de un ciclo de reloj, de manera que los circuitos de entrada en una etapa subsiguiente puedan recibir las salidas durante ese periodo, mientras que la etapa de canalización determinada está generando, al mismo tiempo, nuevas salidas.

En el pasado, era una práctica común colocar registros, antes y después de los circuitos de evaluación de lógica compleja, tales como multiplexores de múltiples entradas (muxes) , codificadores de multibit, etc., para mantener las entradas y las salidas de los circuitos de la evaluación. Generalmente, estos registros tienen unos requisitos de tiempo de mantenimiento y establecimiento asociados, los cuales imponen restricciones sobre los circuitos de evaluación en la etapa precedente. Además, los registros tienen características de tiempo dato-a-salida correspondientes, que imponen restricciones sobre los circuitos de evaluación en las etapas subsiguientes. La "velocidad" de un registro suele ser juzgada, típicamente, en términos de su tiempo dato-a-salida, es decir, la suma de su tiempo de establecimiento y su tiempo de reloj-a-salida.

La colocación de circuitos de registro tradicionales antes y después de un circuito de evaluación lógico introduce retrasos en un sistema canalizado, cuyo efecto acumulativo resulta en velocidades de operación considerablemente más lentas. Más específicamente, una fuente notable de estos retrasos son los requisitos de tiempo de dato-a-salida que deben ser satisfechos por los circuitos de evaluación lógica, con el fin de garantizar salidas registradas estables.

Se desea reducir estos retrasos para proporcionar tiempo adicional en cada etapa y, de esta manera, incrementar la velocidad global del sistema canalizado.

La publicación de solicitud de patente US No. 2005/0127952A1 (Expediente: CNTR.2200-CP1) , titulada "Noninverting Domino Register", abordó los problemas descritos anteriormente. En la divulgación anterior, se describió un 45 registro dominó, no inversor, que combinaba las funciones de evaluación lógica con sus registros correspondientes para conseguir un tiempo reloj-a-salida más rápido que los enfoques convencionales, sin comprometer la estabilidad de su salida. Se demostró que las transiciones de la señal de salida del registro dominó, no inversor, divulgado en dicho documento eran muy rápidas en respuesta a las transiciones de la señal de reloj, en contraste con las respuestas de transición más lentas de los registros dominó, inversores, convencionales. El registro dominó, no inversor, anterior era también flexible con respecto a la configuración de la lógica de evaluación, que podría ser provista como lógica de canal N, lógica de canal P, o una combinación de las mismas.

En la publicación de solicitud de patente US No. 2006/0038589A1 (Expediente: CNTR.2299) , titulada "P-Domino Register", se divulga una versión de canal P del registro dominó, no inversor.

Ambas versiones de canal N y canal P del registro dominó, no inversor, proporcionan considerables ventajas de velocidad cuando las entradas de datos hacen que el registro no inversor descargue un nodo precargado o cargue un nodo predescargado, en función del reloj. Sin embargo, los presentes inventores han indicado también un deseo de reducir el tiempo reloj-a-salida para ambas versiones de canal P y canal N del registro dominó, no inversor, cuando las entradas de datos sean tales que el nodo precargado no se descargue o el nodo predescargado no se cargue, en función del reloj.

Consiguientemente, se desea proporcionar registros, de tipo dominó N, y dominó P mejorados, con caminos acelerados para proporcionar todos los beneficios de los registros dominó, no inversores, anteriores, y que sean más flexibles con relación a la etapa dominó, y que además sean óptimas para su uso en un entorno de fuga alta o de ruido alto.

SUMARIO DE LA INVENCIÓN

En una realización, se proporciona un registro dinámico, no inversor. El registro dinámico, no inversor, incluye una etapa dominó, un multiplexador y una etapa de salida. La etapa dominó evalúa una función lógica en base a al menos una señal de datos de entrada y una señal de reloj a impulsos, donde la etapa dominó precarga un nodo precargado a alto cuando la señal de reloj a impulsos está baja y abre una ventana de evaluación cuando la señal de reloj a impulsos sube, y pone el nodo precargado a nivel bajo si evalúa, y mantiene el nodo precargado alto si no evalúa. El mux está acoplado a la etapa dominó. El mux es sensible a la señal de reloj a impulsos y al nodo precargado. El mux pone un nodo de retroalimentación a nivel bajo si el nodo precargado baja durante la ventana de evaluación, y pone el nodo de retroalimentación a nivel alto si el nodo precargado está alto durante la ventana de evaluación. El mux recibe una señal de retroalimentación retrasada que tiene el mismo estado que el nodo de retroalimentación, pero retrasado en el tiempo, donde la señal de retroalimentación retrasada es seleccionada cuando la señal de reloj a impulsos baja. La etapa de salida está acoplada al nodo precargado y al nodo de retroalimentación. La etapa de salida proporciona una señal de salida en base a los estados del nodo precargado y el nodo de retroalimentación.

En otra realización, se proporciona un procedimiento para registrar una función lógica y generar una salida no invertida. El procedimiento incluye precargar un primer nodo alto mientras una señal de reloj a impulsos está baja, evaluar una función lógica para controlar el estado del primer nodo cuando la señal de reloj a impulsos sube (donde la evaluación comprende poner el primer nodo a nivel bajo cuando la función lógica evalúa y mantener el primero nodo alto cuando la función lógica no evalúa) , controlar, en primer lugar, el estado de un segundo nodo con un primer estado retrasado del primer nodo cuando la señal de reloj a impulsos sube (donde el primer control comprende seleccionar primero el primer estado retrasado del primer nodo como una salida de un mux, donde la salida está acoplada al segundo nodo) , controlar, en segundo lugar, el estado del segundo nodo con un segundo estado retrasado del segundo nodo cuando la señal de reloj a impulsos baja, y determinar el estado de un nodo de salida en base a los estados de los nodos primero y segundo.

BREVE DESCRIPCIÓN DE LOS DIBUJOS

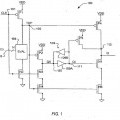

Los beneficios, características y ventajas de la presente invención se comprenderán mejor con referencia a la descripción siguiente y a los dibujos adjuntos, en los que:

La Figura 1 es un diagrama esquemático de un registro, de tipo dominó N, no inversor, implementado según una divulgación previa, que se incorpora por referencia; La Figura 2 es un diagrama de tiempos que ilustra el funcionamiento del registro, de tipo dominó N, no inversor, de las... [Seguir leyendo]

Reivindicaciones:

1. Registro dinámico, de canal N, no inversor, que comprende:

una etapa dominó, para evaluar una función lógica en base a al menos una señal de datos de entrada y una señal de reloj a impulsos, en el que dicha etapa dominó precarga un nodo precargado a alto cuando dicha señal de reloj a impulsos está baja y abre una ventana de evaluación cuando dicha señal de reloj a impulsos sube, y baja dicho nodo precargado si evalúa, y mantiene dicho nodo precargado alto si no evalúa; un mux, acoplado a la etapa dominó, que responde a dicha señal de reloj a impulsos y a dicho nodo precargado, que baja un nodo de retroalimentación si dicho nodo precargado baja durante dicha la ventana de evaluación, y que sube dicho nodo de retroalimentación si dicho nodo precargado está alto durante dicha ventana de evaluación, y que recibe una señal de retroalimentación retrasada que tiene el mismo estado que dicho nodo de retroalimentación, pero retrasado en el tiempo, en el que la señal de retroalimentación retrasada es seleccionada cuando dicha señal de reloj a impulsos baja; y una etapa de salida, acoplada a dicho nodo precargado y dicho nodo de retroalimentación, que proporciona una señal de salida en base a los estados de dicho nodo precargado y dicho nodo de retroalimentación.

2. Registro dinámico, no inversor, según la reivindicación 1, en el que la etapa dominó comprende:

un dispositivo de canal P que tiene una puerta que recibe dicha señal de reloj a impulsos, y un drenador y una fuente acoplados entre una fuente de voltaje y dicho nodo precargado; un dispositivo de canal N que tiene una puerta que recibe dicha señal de reloj a impulsos, y un drenador acoplado a dicho nodo precargado, y una fuente; y lógica de evaluación acoplada entre tierra y dicha fuente de dicho dispositivo de canal N.

3. Registro dinámico, no inversor, según la reivindicación 2, en el que la lógica de evaluación comprende lógica de semiconductor de óxido metálico complementario.

4. Registro dinámico, no inversor, según la reivindicación 1, que comprende además:

una primera lógica de retraso, acoplada a dicho nodo precargado y una primera entrada de dicho mux, configurada para generar una primera señal retrasada que tiene el mismo estado que dicho nodo precargado, pero retrasado en el tiempo.

5. Registro dinámico, no inversor, según la reivindicación 4, que comprende además:

una segunda lógica de retraso, acoplada a dicho nodo de retroalimentación y una segunda entrada de dicho mux, configurada para generar dicha señal de retroalimentación retrasada.

6. Registro dinámico, no inversor, según la reivindicación 1, en el que dicha señal de reloj a impulsos está acoplada a una primera entrada de selección de dicho mux, y en el que una versión invertida de dicha señal de reloj a impulsos está acoplada a una segunda entrada de selección de dicho mux.

7. Registro dinámico, no inversor, según la reivindicación 1, en el que la etapa de salida comprende una puerta NAND.

8. Registro dinámico, no inversor, según la reivindicación 1, en el que dicha etapa dominó, dicho mux y dicha etapa de salida se fabrican usando un proceso de silicio-sobre-aislante, a una escala de 90 nanómetros.

9. Procedimiento de registro de una función lógica y generación de una salida no invertida, que comprende:

precargar un primer nodo alto, mientras una señal de reloj a impulsos está baja; evaluar una función lógica para controlar el estado del primer nodo cuando la señal de reloj a impulsos sube, comprendiendo dicha evaluación; bajar el primer nodo cuando la función lógica evalúa y mantener el primer nodo alto cuando la función lógica falla en la evaluación; controlar, en primer lugar, el estado de un segundo nodo con un primer estado retrasado del primer nodo cuando la señal de reloj a impulsos sube, comprendiendo dicho primer control; seleccionar, en primer lugar, un primer estado retrasado del primer nodo como una salida de un mux, en el que la salida está acoplada al segundo nodo; controlar, en segundo lugar, el estado del segundo nodo con un segundo estado retrasado del segundo nodo cuando la señal del reloj a impulsos baja, y determinar el estado de un nodo de salida en base a los estados del primer nodo y del segundo nodo.

10. Procedimiento según la reivindicación 9, en el que dicho segundo control comprende: Seleccionar, en segundo lugar, el segundo estado retrasado del segundo nodo de la salida del MUX.

11. Procedimiento según la reivindicación 9, en el que dicha determinación del estado de un nodo de salida comprende combinar lógicamente los estados del primer nodo y del segundo nodo con una función NAND.

Patentes similares o relacionadas:

FAMILIA DE CIRCUITOS LOGICOS PARALELOS DE ENTRADA LOGICA COMPLEMENTARIA (CLIP)., del 16 de Noviembre de 1995, de THUNDERBIRD TECHNOLOGIES, INC.: UNA FAMILIA DE CIRCUITOS LOGICOS PARALELOS DE ENTRADA LOGICA COMPLEMENTARIA (CLIP), DE BAJA CAPACITANCIA Y ALTA VELOCIDAD QUE INCLUYE UNA […]

CONTROL DEL PICO DE CORRIENTE EN CMOS DINAMICAS., del 1 de Octubre de 1993, de AMERICAN TELEPHONE AND TELEGRAPH COMPANY: UN CIRCUITO INTEGRADO QUE TIENE UN GRAN NUMERO DE ETAPAS CON PUERTAS LOGICAS PARA TRASMISION SE HA ENCONTRADO QUE SUFRE UNA GRAN PICO DE CORRIENTE AL CONECTARSE. ESTO ES […]

CIRCUITO DE ENGANCHE DE SALIDA DOMINÓ N, del 23 de Diciembre de 2011, de VIA TECHNOLOGIES, INC.: Un circuito de enganche dominó N que comprende: una etapa dominó (P1, N2, 301) acoplada a una señal (CLK) de reloj aproximadamente simétrica, y para evaluar una función […]

REGISTRO DE TIPO DOMINÓ P, del 25 de Mayo de 2011, de VIA TECHNOLOGIES, INC.: Registro de tipo dominó P, que comprende: una etapa dominó, acoplada a una señal de impulsos de reloj, y destinada a evaluar una función lógica según […]

REGISTRO DE TIPO DOMINÓ P, del 25 de Mayo de 2011, de VIA TECHNOLOGIES, INC.: Registro de tipo dominó P, que comprende: una etapa dominó, acoplada a una señal de impulsos de reloj, y destinada a evaluar una función lógica según […]

REGISTRO DE EFECTO DOMINO N CON TRAYECTO ACELERADO SIN DESCARGA, del 16 de Abril de 2009, de VIA TECHNOLOGIES, INC.: Un registro con efecto dominó de no inversión , que comprende: una etapa con efecto dominó para evaluar una función lógica basada en al menos una señal de datos de entrada […]

REGISTRO DE EFECTO DOMINO N CON TRAYECTO ACELERADO SIN DESCARGA, del 16 de Abril de 2009, de VIA TECHNOLOGIES, INC.: Un registro con efecto dominó de no inversión , que comprende: una etapa con efecto dominó para evaluar una función lógica basada en al menos una señal de datos de entrada […]