GESTOR DE MENSAJES Y METODO PARA EL CONTROL DE ACCESO A LOS DATOS DE UNA MEMORIA DE MENSAJES DE UN MODULO DE COMUNICACION.

Módulo de comunicación (100) con un gestor de mensajes (200) y una memoria de mensajes (300),

a la cual, mediante un acceso, se pueden ingresar o de la cual se pueden extraer datos, por este motivo la memoria de mensajes (300) se encuentra conectada a una primera disposición de memoria búfer (205, 206) y a una segunda disposición de memoria búfer (201, 202), produciéndose un acceso a los datos mediante la primera o la segunda disposición de memorias búfer, con lo cual se encuentra colocada la primera disposición de memoria búfer (205, 206) entre la memoria de mensajes (300) y una interfaz (207, 208), hacia un enlace de comunicación (101), así como la segunda disposición de memoria búfer (201, 202) se encuentra colocada entre la memoria de mensajes (300) y una interfaz (203, 204) hacia un procesador participante (102),

caracterizado porque,

- en el gestor de mensajes (200) se prevee al menos una primera máquina de estado finito (503, 503), la cual dirige el acceso a la memoria de mensajes mediante la primera disposición de memoria búfer (205, 206) y

- se prevee al menos una segunda máquina de estado finito (501), la cual dirige el acceso mediante la segunda disposición de memoria búfer (201, 202), por lo que al menos una primera máquina de estado finito y una segunda máquina de estado finito presentan peticiones de acceso y

- se prevee una tercera máquina de estado finito (500), la cual adjudica el acceso, a al menos una de las máquinas de estado finito y a la segunda máquina de estado finito, dependiendo de sus peticiones de acceso,

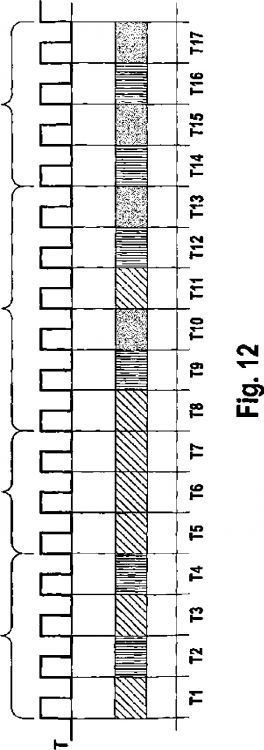

- se preveen medios del temporizador, a través de los cuales se transmiten los datos en un período predeterminado del temporizador (T) y la tercera máquina de estado finito (500) adjudica períodos del temporizador consecutivos a cada una de las máquinas de estado finito y a la segunda máquina de estado finito, dependiendo de sus peticiones de acceso,

- se preveen los medios para dividir el tiempo total de acceso, de manera tal que esta división coincida con el número de peticiones de acceso,

- a través de la tercera máquina de estado finito (500), por lo que, por cada máquina de estado finito sólo se admite al mismo tiempo una petición de acceso, y

- se preveen los medios para, hasta la finalización de una transmisión de un objeto de mensaje en un primera dirección entre la segunda disposición de memoria búfer (201, 202) y la memoria de mensajes (300), bloquear la segunda disposición de memoria búfer (201, 202) para otros accesos en la primera dirección de transmisión

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2005/053074.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20,70442 STUTTGART.

Inventor/es: HARTWICH, FLORIAN, HORST,CHRISTIAN, BAILER,FRANZ, IHLE,MARKUS.

Fecha de Publicación: .

Fecha Concesión Europea: 23 de Diciembre de 2009.

Clasificación Internacional de Patentes:

- G06F13/16A8S

Clasificación PCT:

- G06F13/16 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › para el acceso al bus de memoria (G06F 13/28 tiene prioridad).

Fragmento de la descripción:

Gestor de mensajes y método para el control de acceso a los datos de una memoria de mensajes de un módulo de comunicación.

Estado actual de la técnica

La presente invención se basa en un gestor de mensajes y en un método para el control de acceso a los datos de una memoria de mensajes de un módulo de comunicación conforme al preámbulo de la reivindicación independiente.

La conexión en red de dispositivos de control, sensores y actuadores con ayuda de un sistema de comunicación y de un sistema ómnibus, por consiguiente, de un enlace de comunicación, ha aumentado en forma drástica en los últimos años, tanto en la construcción de vehículos modernos como también en la construcción de máquinas, especialmente en el sector de las máquinas-herramienta, y en la automatización. A través de la distribución de funciones en varios dispositivos de control pueden obtenerse efectos sinérgicos. Se habla así de sistemas distribuidos. La comunicación entre diferentes estaciones tiene lugar cada vez más frecuentemente mediante un sistema ómnibus, o mediante un enlace de comunicación. La circulación de la información en el sistema ómnibus, los mecanismos de entrada y salida, así como también el control de errores están regidos por un protocolo. Dentro de este área es conocido el protocolo CAN, así como también los protocolos TTCAN y FlexRay que sirven de base actualmente a la especificación del protocolo FlexRay. Flexray es un sistema ómnibus rápido, determinista y tolerante a fallos, en especial para la utilización en un vehículo. El protocolo FlexRay trabaja conforme al acceso múltiple por división de tiempo (TDMA), en el cual los componentes -las partes- de los mensajes a transmitir son adjudicados en ranuras de tiempo, donde éstas tienen una entrada exclusiva al enlace de comunicación. Un translado similar tiene lugar en TTCAN. Las ranuras de tiempo se repiten en un ciclo determinado, de manera que el instante en el que se transmite el mensaje mediante el bus, puede predecirse con exactitud, y el acceso al bus se produce determinísticamente. Para aprovechar óptimamente el ancho de la banda para la transmisión del mensaje en el sistema ómnibus, FlexRay subdivide el ciclo en una parte dinámica y una parte estática. Las ranuras de tiempo determinadas se encuentran así en la parte estática al comienzo de un ciclo de bus. En la parte dinámica las ranuras de tiempo se adjudican dinámicamente. De esta forma se posibilita entonces el exclusivo acceso al bus cada vez sólo por un corto tiempo, conocido como minislots (miniranuras de tiempo). Sólo cuando un acceso al bus tiene lugar dentro de una miniranura, se alarga la ranura durante el tiempo necesario. De esta manera, el ancho de banda se utiliza sólo cuando efectivamente se le necesita. De este modo FlexRay comunica mediante dos líneas separadas con una velocidad máxima de 10 MB. Ambos canales corresponden a la capa física, en especial al modelo de capas del OSI (Open System Architecture). Estos canales sirven efectivamente para lograr una transmisión de mensajes redundante y tolerante a fallos, por lo cual se duplicaría entonces la velocidad. FlexRay puede, sin embargo, ser activado también con velocidades más bajas. Para realizar funciones sincrónicas y optimizar el ancho de banda mediante pequeñas distancias entre los mensajes, los componentes distribuidos en la red de comunicación FlexRay los participantes, requieren de una base de tiempo común, conocida como tiempo global.

Para lograr la sincronización de tiempos se transmiten colas de mensajes a la parte estática del ciclo, de manera tal que con la ayuda de un algoritmo especial correspondiente a la especificación FlexRay, el tiempo local de un componente es corregido, logrando así que todos los relojes marchen sincrónicamente en una secuencia de tiempo global. Esta sincronización es similar en la red de comunicación TTCAN.

Un nodo de red FlexRay o un participante-FlexRay o procesador central contiene un procesador participante o procesador central, un controlador FlexRay o controlador de comunicación así como un control del bus contiene un controlador del bus. Con ello el procesador central o procesador participante envía y procesa los datos transmitidos por el controlador de comunicación FlexRay. Para la comunicación en una red FlexRay pueden configurarse mensajes u objetos de mensajes, con por ejemplo, hasta 254 bytes de datos. Para transmitir estos mensajes u objetos de mensajes entre la capa física, por tanto entre el enlace de comunicación y el procesador central, se emplea un módulo de comunicación, en particular un controlador de comunicación.

La solicitud US5983327 da a conocer un método de arbitraje, por el cual, accesos simultáneos de diferentes componentes de una memoria común, son anidados unos dentro de otros, de manera tal que palabras de dato de los accesos opuestos puedan transmitirse en forma alternada.

Es objeto de la presente invención el dirigir la transmisión de datos, de manera tal, que se asegure la integridad de los datos y se optimice la velocidad de transmisión.

Ventajas de la invención

La invención se basa en un módulo de comunicación, conforme a la reivindicación 1, y en un procedimiento conforme a la reivindicación 3.

Esto significa que la invención describe un método y un dispositivo para la transferencia de datos entre una memoria de mensajes, por tanto entre una memoria RAM y una memoria búfer de entrada y de salida, así como entre la memoria de mensajes y las unidades de transmisión y recepción hacia el bus de comunicación, y para la dirección de esta transferencia de manera tal, que se asegure la integridad de los datos requerida y una mayor velocidad de transferencia de los mensajes a almacenar.

Convenientemente, los datos se dirigen a través de un gestor de mensajes mediante la primera disposicición de búfers y dos rutas de datos con dos direcciones de datos cada una respectivamente, por lo cual una primera disposición de búfers contiene un primer búfer para una primer ruta de datos y una segundo búfer para una segunda ruta de datos y, a su vez, la ruta de datos se encuentra provista de una primer máquina de estado o máquina de estado finito, de manera que resultan dos máquinas de estado para la primera disposición de búfers, por lo que cada una de las dos primeras máquinas de estado o máquinas de estado finitas dirigen el acceso a la memoria de mensajes mediante un búfer.

Convenientemente se preveen medios de temporización, a través de los cuales se pueden transmitir los datos en un período del temporizador predeterminado, con lo cual la tercera máquina de estado o máquina de estado finito y cada segunda máquina de estado finito, adjudica, dependiendo de sus peticiones de acceso, los correspondientes períodos sucesivos del temporizador.

De manera ventajosa, se preveen los medios para dividir el tiempo total de acceso, de manera tal que esta división coincida con el número de peticiones de acceso, a través de la tercera máquina de estado finito (500), por lo que, por cada máquina de estado finito sólo se admite al mismo tiempo una petición de acceso.

El método y el gestor de mensajes descritos, así como un módulo de comunicación correspondiente con esa clase de gestor de mensajes, le permite al procesador CPU 102 en actividad, leer o escribir cualquier objeto de mensaje en la memoria de mensajes, sin que el objeto de mensaje seleccionado para la duración del acceso del procesador CPU 102 sea encerrado (Búfer Locking -cierre de búfer-) por la participación en el intercambio de datos en los dos canales del bus FlexRay. Al mismo tiempo, se asegura la integridad de los datos depositados en la memoria de mensajes, mediante la imbricación de los accesos, conforme al temporizador, y también se aumenta la velocidad de transmisión.

Otras ventajas y diseños ventajosos resultan de la descripción, así como también de las características de las reivindicaciones.

Dibujos

La invención se explica en detalle mediante las siguientes figuras.

La figura 1 muestra, mediante una representación esquemática, el módulo de comunicación y su conexión a la capa física, por tanto el enlace de comunicación y el participante del procesador o participante de la comunicación.

La figura 2 presenta en detalle, en una forma de ejecución especial, el módulo de comunicación de la figura 1, así como su conexión.

En la figura 3 se representa la estructura de la memoria.

Las figuras 4 a 6 describen esquemáticamente la arquitectura y el proceso...

Reivindicaciones:

1. Módulo de comunicación (100) con un gestor de mensajes (200) y una memoria de mensajes (300), a la cual, mediante un acceso, se pueden ingresar o de la cual se pueden extraer datos, por este motivo la memoria de mensajes (300) se encuentra conectada a una primera disposición de memoria búfer (205, 206) y a una segunda disposición de memoria búfer (201, 202), produciéndose un acceso a los datos mediante la primera o la segunda disposición de memorias búfer, con lo cual se encuentra colocada la primera disposición de memoria búfer (205, 206) entre la memoria de mensajes (300) y una interfaz (207, 208), hacia un enlace de comunicación (101), así como la segunda disposición de memoria búfer (201, 202) se encuentra colocada entre la memoria de mensajes (300) y una interfaz (203, 204) hacia un procesador participante (102),

caracterizado porque,

2. Módulo de comunicación (100) conforme a la reivindicación 1, caracterizado porque, los datos son transmitidos mediante una primera disposición de memoria búfer (205, 206) en dos rutas de datos con dos direcciones de datos respectivamente y la primera disposición de memoria búfer (205, 206) contiene una primera memoria búfer (206) para una primera ruta de datos y una segunda memoria búfer (205) para una segunda ruta de datos y para cada ruta de datos se prevee una primera máquina de estado finito (502, 503), por lo cual cada una de las máquinas de estado finito dirige el acceso a la memoria de entrada mediante una memoria búfer.

3. Método para controlar el acceso de datos de una memoria de mensajes (300) de un módulo de comunicación a través de un gestor de mensajes (200), por lo cual se ingresan o se devuelven datos gracias al acceso, por lo que la memoria de mensajes (300) se encuentra conectada a una primera disposición de memoria búfer (205, 206) y a una segunda disposición de memoria búfer (201, 202), produciéndose un acceso a los datos mediante la primera o la segunda disposición de memorias búfer, con lo cual se encuentra colocada la primera disposición de memoria búfer (205, 206) entre la memoria de mensajes (300) y una interfaz (207, 208), hacia un enlace de comunicación (101), así como la segunda disposición de memoria búfer (201, 202) se encuentra colocada entre la memoria de mensajes (300) y una interfaz (203, 204) hacia un procesador participante (102), caracterizado porque,

4. Método conforme a la reivindicación 3, caracterizado porque, los datos son transmitidos mediante una primera disposición de memoria búfer (205, 206) en dos rutas de datos con dos direcciones de datos respectivamente y la primera disposición de memoria búfer (205, 206) contiene una primera memoria búfer (206) para una primera ruta de datos y una segunda memoria búfer (205) para una segunda ruta de datos y para cada ruta de datos se prevee una primera máquina de estado finito (502, 503), por lo cual cada una de las máquinas de estado finito dirige el acceso a la memoria de entrada mediante una memoria búfer.

Patentes similares o relacionadas:

PROCEDIMIENTO Y APARATO PARA LLEVAR A CABO UNA OPERACIÓN ATÓMICA DE SEMÁFORO, del 9 de Enero de 2012, de QUALCOMM INCORPORATED: Un sistema de procesamiento que comprende: un bus (106; 106a, 106b); una región de memoria acoplada al bus; y una pluralidad […]

Circuito integrado foto-repetido con compensación de retardos de propagación de señal, especialmente de señales de reloj, del 22 de Julio de 2020, de Pyxalis: Circuito integrado que comprende N patrones adyacentes, todos idénticos, que corresponden a N circuitos parciales adyacentes idénticos (C1, C2, C3) de rango i = 1 a […]

Técnicas de ahorro de energía para sistemas de memoria, del 22 de Abril de 2020, de QUALCOMM INCORPORATED: Un procesador central , que comprende: una interfaz de capa física, PHY, configurada para acoplarse a una pluralidad de carriles de datos de un […]

Método y dispositivo para procesar datos, del 12 de Junio de 2019, de ZTE CORPORATION: Un método para procesar datos, que comprende: después de recibir datos introducidos por un bus de datos, de acuerdo con una indicación de destino de los datos y una indicación […]

Sincronización de actualización automática dirigida, del 5 de Junio de 2019, de QUALCOMM INCORPORATED: Un procedimiento, mediante un módulo de memoria y un controlador , de actualización de una pluralidad de bancos de memoria , que comprende: aceptar […]

Memoria configurada para proporcionar acceso simultáneo de lectura/escritura a múltiples bancos, del 19 de Febrero de 2019, de QUALCOMM INCORPORATED: Un dispositivo, que comprende: una memoria de múltiples bancos con al menos bancos de memoria primero y segundo ; al menos controladores […]

Controlador de acceso a memoria, sistemas y procedimientos para optimizar los tiempos de acceso a memoria, del 9 de Enero de 2019, de QUALCOMM INCORPORATED: Un controlador de memoria , que comprende: un controlador configurado para acceder al menos a una ubicación de memoria correspondiente […]

Esquema de interfaz de DDR de un único canal y de doble canal híbrida mediante intercalado de las señales de dirección/control durante el funcionamiento de doble canal, del 21 de Septiembre de 2018, de QUALCOMM INCORPORATED: Una estructura de memoria, que comprende: un controlador de memoria configurado para recibir una señal de reloj y para ser […]