Generación de señal de reloj y control para dispositivos de memoria de alto rendimiento.

Un dispositivo de memoria que comprende:

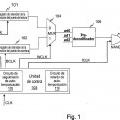

un primer generador de reloj configurado para generar una primera señal de reloj (RCLKb) utilizada para operaciones de lectura y escritura;

un segundo generador de reloj configurado para generar una segunda señal de reloj (WCLKb) utilizada para operaciones de escritura;

una matriz de memoria que comprende células de memoria y células ficticias;

caracterizado por que:

el primer generador de reloj comprende un primer circuito configurado para generar bordes iniciales en la primera señal de reloj basada en una señal de reloj externa (CLK) y para generar bordes finales en la primera señal de reloj basada en al menos una señal de reinicio,

en el que un circuito de reinicio está configurado para generar la al menos una señal de reinicio para el primer y segundo generadores de reloj, y

en el que el circuito de reinicio está configurado para generar la al menos una señal de reinicio con el tiempo determinado basándose en la carga en una línea de bits para una columna de las células ficticias en la matriz de memoria o la carga en una línea de palabras para una fila de células ficticias en el matriz de memoria.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2008/065448.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: Attn: International IP Administration 5775 Morehouse Drive San Diego, CA 92121 ESTADOS UNIDOS DE AMERICA.

Inventor/es: JUNG,CHANG HO, CHEN,ZHIQIN.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C11/418 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 11/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento eléctricos o magnéticos particulares; Elementos de almacenamiento correspondientes (G11C 14/00 - G11C 21/00 tienen prioridad). › Circuitos de direccionamiento.

- G11C11/419 G11C 11/00 […] › Circuitos de lectura-escritura [R-W].

- G11C7/22 G11C […] › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Circuitos de sincronización o de reloj para la lectura-escritura [R-W]; Generadores o gestión de señales de control para la lectura-escritura [R-W].

PDF original: ES-2745948_T3.pdf

Patentes similares o relacionadas:

Circuitos de líneas de bits globales de Memoria Estática de Acceso Aleatorio (SRAM) para reducir los fallos de energía durante los accesos de lectura de memoria, y procedimientos y sistemas relacionados, del 17 de Abril de 2019, de QUALCOMM INCORPORATED: Un circuito de línea de bits global de memoria estática de acceso aleatorio, SRAM, para una pluralidad de células de bits de SRAM, que […]

Sistema y procedimiento de operación de un dispositivo de memoria, del 13 de Mayo de 2015, de QUALCOMM INCORPORATED: Un aparato que comprende: una célula bit acoplada a una primera línea de bit , a una segunda línea de bit , y a una línea de palabra (106, […]

PRECARGA DE CMOS Y CIRCUITO DE ECUALIZACION., del 16 de Marzo de 1996, de ADVANCED MICRO DEVICES INC.: LA PRECARGA DE UNA CMOS Y UN CIRCUITO DE ECUALIZACION PARA SU USO CON CELDAS DE MEMORIAS ACOPLADAS ENTRE LINEAS DE BIT PAREADAS EN UNA MATRIZ […]

MEMORIA INTEGRADA QUE COMPRENDE UN AMPLIFICADOR DE DETECCION., del 1 de Diciembre de 1995, de PHILIPS ELECTRONICS N.V.: UNA MEMORIA INTEGRADA QUE COMPRENDE UN AMPLIFICADOR DE DETECCION QUE TIENE UN EFECTO DE ECUALIZACION SOBRE LOS VOLTAJES EN LAS ENTRADAS […]

CELDA PARA EL ALMACENAMIENTO DE BITS., del 1 de Junio de 1994, de CARLSTEDT ELEKTRONIK AB: EL INVENTO SE DESCRIBE COMO UNA CELULA DE UN BIT DE MEMORIA MUY RAPIDA PARA SER REALIZADA CON TECNICAS VLSI. SE PUEDEN EMPAQUETAR MUCHAS DE ESTAS CELULAS DE […]

PROCESADOR DE REDUCCION., del 16 de Mayo de 1994, de CARLSTEDT ELEKTRONIK AB: SE PROPORCIONA UN PROCESADOR DE REDUCCION, EL CUAL SE CONTROLA MEDIANTE UN PROGRAMA QUE TIENE UNA ESTRUCTURA Y QUE ESTA ADAPTADO DE MANERA QUE REDUZCA DICHA ESTRUCTURA […]

Multiplexado de direcciones en una memoria de puerto pseudo-dual, del 25 de Marzo de 2015, de QUALCOMM INCORPORATED: Un sistema de multiplexado de direcciones de memoria de puerto pseudo-dual que comprende:

un componente de memoria;

un registro de retención […]

Multiplexado de direcciones en una memoria de puerto pseudo-dual, del 25 de Marzo de 2015, de QUALCOMM INCORPORATED: Un sistema de multiplexado de direcciones de memoria de puerto pseudo-dual que comprende:

un componente de memoria;

un registro de retención […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]