Multiplexado de direcciones en una memoria de puerto pseudo-dual.

Un sistema de multiplexado de direcciones de memoria de puerto pseudo-dual que comprende:

un componente de memoria;

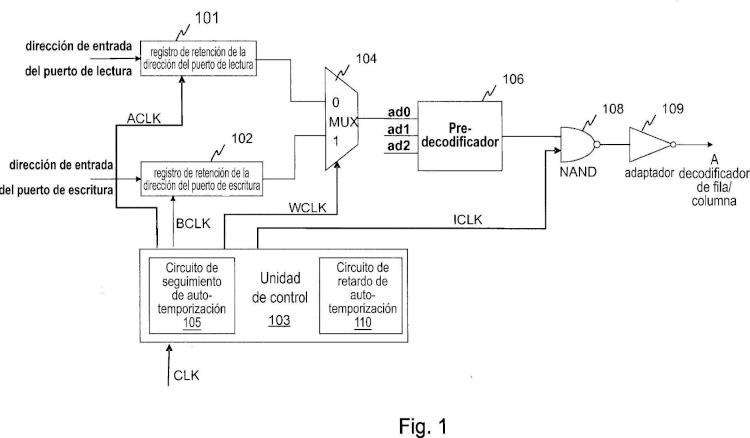

un registro de retención (101) de la dirección del puerto de lectura operativa para mantener una dirección de lectura en respuesta a una señal de reloj externa;

un registro de retención (102) de la dirección del puerto de escritura operativa para mantener una dirección de escritura en respuesta a la señal de reloj externa;

un circuito (103) de control que controla el acceso de lectura/escritura a la memoria en base a la supervisión de una primera operación de memoria mediante el envío de la señal de conmutación, en la que dicho circuito (103) de control es operativo también para identificar los modos de operación lectura/escritura, solo lectura y solo escritura; y

un multiplexor (104) que conmuta entre una dirección de lectura mantenida y una dirección de escritura mantenida en respuesta a la señal del conmutador desde el circuito (103) de control; en el que una operación de lectura de memoria es una condición o estado de memoria por defecto cuando se espera una próxima señal de reloj externa de modo que la operación de lectura de memoria es una primera operación a ser ejecutada cuando se han de realizar tanto operaciones de lectura como de escritura durante un único ciclo de reloj de la señal del reloj externo;

en respuesta a una solicitud de lectura en ausencia de una solicitud de escritura, dicho multiplexor (104) proporciona una dirección de lectura a dicho componente de memoria y dicho circuito (103) de control mantiene una señal de enclavamiento de la dirección del puerto de escritura, de modo que el registro de retención (102) de la dirección del puerto de escritura esté listo para recibir cualquier señal aplicada que pudiera llegar; y

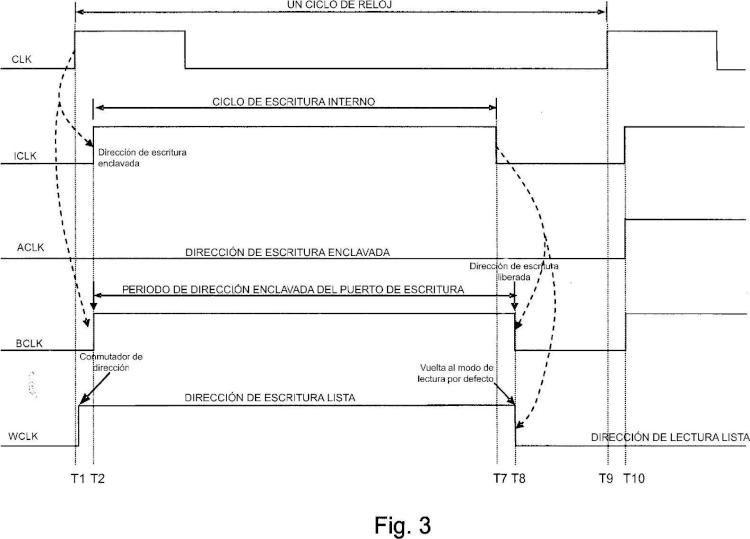

en respuesta a una solicitud de escritura en ausencia de una solicitud de lectura, dicho multiplexor (104) proporciona una dirección de escritura a dicho componente de memoria y dicho circuito (103) de control mantiene la señal de enclavamiento de la dirección del puerto de lectura, de modo que el registro de retención (101) de la dirección del puerto de lectura esté listo para recibir cualquier señal aplicada que pudiera llegar y avance una temporización de una operación de escritura de modo que la operación de escritura se inicie antes, durante un ciclo de reloj, que cuando se solicitan tanto operaciones de lectura como de escritura y se realizan en un mismo ciclo de reloj.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2009/035371.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: ATTN: INTERNATIONAL IP ADMINISTRATION 5775 MOREHOUSE DRIVE SAN DIEGO, CALIFORNIA 92121-1714 ESTADOS UNIDOS DE AMERICA.

Inventor/es: ZHONG,CHENG, JUNG,CHANGHO.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C7/22 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Circuitos de sincronización o de reloj para la lectura-escritura [R-W]; Generadores o gestión de señales de control para la lectura-escritura [R-W].

- G11C8/16 G11C […] › G11C 8/00 Disposiciones para seleccionar una dirección en una memoria digital (circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Red de memoria de acceso múltiple, p. ej. direccionamiento de un elemento de almacenamiento mediante al menos dos grupos de líneas de direccionamiento independientes.

PDF original: ES-2540058_T3.pdf

Fragmento de la descripción:

Multiplexado de direcciones en una memoria de puerto pseudo-dual Campo de la divulgación La divulgación se refiere en general a circuitos de memoria. Más específicamente, la divulgación se refiere al control de direcciones para memorias de puerto pseudo-dual.

Antecedentes Las memorias de puerto dual tienen típicamente dos puertos y una matriz de celdas de memoria. Puede accederse simultáneamente a la matriz de memoria desde ambos puertos siempre que las celdas de memoria a las que se está accediendo desde un puerto no sean las mismas celdas de memoria a las que se está accediendo desde el otro puerto. El tipo común de celda de memoria usada en dichas memorias de puerto dual implica ocho transistores de efecto de campo (FET) .

Las celdas de memoria en una memoria típica de puerto único solo incluyen seis transistores. La celda de memoria de seis transistores consume típicamente solo aproximadamente la mitad del área del circuito integrado que la celda de ocho transistores cuando se fabrican los dos tipos de celdas de memoria usando el mismo proceso. Sin embargo, muchas aplicaciones requieren la funcionalidad de una memoria de puerto dual, es decir, una memoria capaz de manejar tanto una operación de lectura como de escritura dentro de un único ciclo de reloj.

Para aprovechar el tamaño más pequeño de la celda de memoria de seis transistores, mientras que se da satisfacción a aquellas aplicaciones que requieren la funcionalidad de memoria de puerto dual, se usa frecuentemente un dispositivo de memoria denominado memoria de puerto pseudo-dual. En un ejemplo, una memoria de puerto pseudo-dual tiene una única matriz de memoria en la que cada celda de memoria de la matriz es una celda de memoria de seis transistores que se puede conectar selectivamente a un único par de líneas de bits (por ejemplo, la línea de bits B y la barra de la línea de bits BN) .

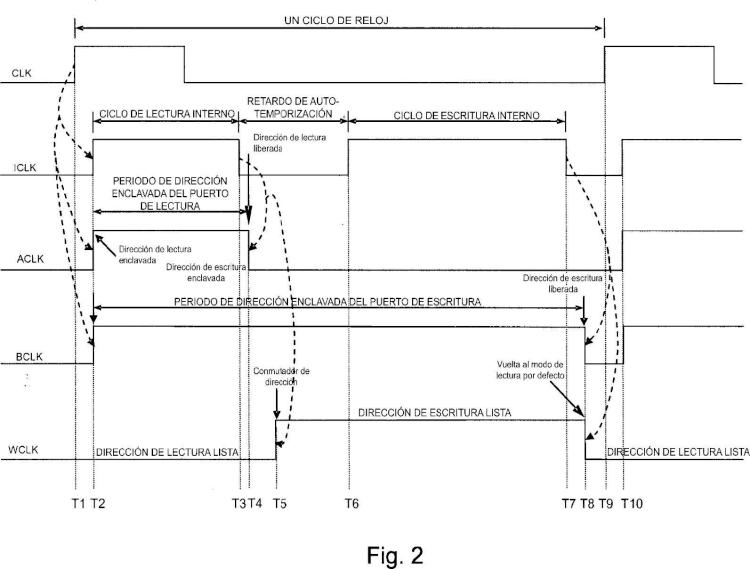

La matriz de memoria opera como una memoria de puerto único en que solamente se realiza un acceso a la memoria en un instante. La memoria de puerto pseudo-dual, sin embargo, imita una memoria de puerto dual en que tiene dos puertos. En un ejemplo, la memoria de puerto pseudo-dual tiene un circuito denominado a veces un Multiplexor de Tiempo Retardado (TDM) . Se recibe una única entrada de señal de reloj en la memoria de puerto pseudo-dual y se usa esta única señal de entrada de reloj para enclavar una dirección de lectura de entrada, una dirección de escritura de entrada y un valor de datos de entrada. El flanco ascendente de la señal de reloj de entrada se usa para iniciar una operación de lectura usando la dirección de lectura de entrada. Se completa la operación de lectura. Posteriormente, tiene lugar el flanco descendente de la señal de entrada de reloj. El TDM usa el flanco descendente de la señal de reloj de entrada para iniciar una operación de escritura. La dirección de escritura de entrada se usa para direccionar la matriz de memoria durante la operación de escritura y los datos escritos en la matriz de memoria son los datos del valor de entrada. Aunque se realicen dos operaciones de memoria en un único ciclo de la señal de entrada de reloj, las dos operaciones de memoria se realizan en realidad una tras otra. Desde el exterior de la memoria de puerto pseudo-dual, sin embargo, la memoria de puerto pseudo-dual parece permitir dos accesos a la matriz de memoria al mismo tiempo o sustancialmente al mismo tiempo, es decir, dentro de un único ciclo de reloj.

La cantidad de tiempo requerido para realizar la primera operación de lectura de memoria puede no ser igual a la cantidad de tiempo requerido para realizar la segunda operación de escritura de memoria. El uso de un enfoque TDM convencional ralentiza los tiempos de acceso a memoria globales debido a que las cantidades de tiempo relativas disponibles para las dos operaciones están determinadas por el tiempo en el que el flanco ascendente del ciclo de reloj tiene lugar y el momento en el que tiene lugar el flanco descendente del ciclo de reloj. Si, por ejemplo, la señal de reloj está baja durante tanto tiempo como está alta en un ciclo de reloj (es decir, la señal de reloj tiene un ciclo de trabajo 50/50) , entonces se debe permitir la misma cantidad de tiempo para la realización tanto de la operación de lectura más rápida como de la operación de escritura más lenta. El resultado es una cantidad de tiempo desperdiciado que comienza después de que se haya completado la operación de lectura y finaliza tras el flanco descendente de la señal de reloj.

El documento WO 2007/114858 describe una memoria de puerto pseudo-dual que realiza tanto una primera operación de acceso a memoria como una segunda operación de acceso memoria en un único período de una señal CLK de reloj suministrada externamente. La señal CLK se usa para enclavar una primera dirección para la primera operación y una segunda dirección para la segunda operación.

El documento US 2008/0027338 describe una memoria que tiene un novedoso circuito de auto-temporización que genera señales de control interno de la memoria. Las señales de control pueden incluir una señal que permite el enclavamiento de direcciones, una señal que habilita el decodificador, y una señal que habilita el amplificador de detección.

El documento US 6 252 814 describe dos líneas de palabra ficticia separadas, una línea de palabra ficticia de lectura y una línea de palabra ficticia de escritura, que se implementan dentro de una matriz de memoria para proporcionar una operación de frecuencia más alta de ciclos de lectura y escritura dentro de la matriz de memoria. Las dos líneas de palabra ficticia se utilizan para activar y desactivar la señal de habilitación de la línea de palabra para las partes de lectura y escritura de un acceso. Dicho acceso puede ser un ciclo lectura/intercambio.

Sumario de la divulgación De acuerdo con un aspecto de la presente invención se proporciona un sistema de multiplexado de direcciones de una memoria de puerto pseudo-dual tal como se expone en la reivindicación 1.

De acuerdo con otro aspecto de la presente invención, se proporciona un procedimiento para el control de una aplicación de una señal de dirección a una memoria como se expone la reivindicación 11.

De acuerdo con una realización de la presente divulgación, un sistema de multiplexado de direcciones de memoria de puerto pseudo-dual tiene un registro de retención de la dirección del puerto de lectura, un registro de retención de la dirección del puerto de escritura, un circuito de control y un multiplexor. El registro de retención de la dirección del puerto de lectura es operativo para mantener una dirección de lectura en respuesta a una señal de reloj externa. El registro de retención de la dirección del puerto de escritura es operativo para mantener una dirección de escritura en respuesta a la señal de reloj externa. El circuito de control controla el acceso a la memoria de lectura/escritura en base a la supervisión de una primera operación de memoria. El multiplexor conmuta entre una dirección de lectura mantenida y una dirección de escritura mantenida en respuesta a una señal de conmutación desde el circuito de control.

En otra realización de la presente invención, un procedimiento controla una aplicación de una señal de dirección a una memoria. El procedimiento incluye la detección de solicitudes de lectura y escritura. En respuesta a una solicitud de lectura en ausencia de una solicitud de escritura, el procedimiento incluye el suministro de una dirección de lectura a un componente de memoria. En respuesta a una solicitud de escritura en ausencia de una solicitud de lectura, el procedimiento incluye el suministro de una dirección de escritura al componente de memoria.

En respuesta a tanto una solicitud de lectura como una solicitud de escritura a ser realizadas durante un único ciclo de reloj, el procedimiento incluye el suministro de la dirección de lectura al componente de memoria. En base a la supervisión de una operación de lectura, el procedimiento incluye además la determinación de un tiempo dentro de un único ciclo de reloj para el suministro de la dirección de escritura al componente de memoria. El procedimiento incluye también la conmutación entre la dirección de lectura y la dirección de escritura para suministrar la dirección de escritura al componente memoria en el momento determinado.

Una ventaja de las realizaciones desveladas es que el multiplexado de la dirección se proporciona en una memoria de puerto pseudo-dual sin impacto en el tiempo de acceso de lectura. Además, el multiplexado se realiza con mínimas penalidades de área y de rendimiento.

Lo precedente ha destacado, bastante ampliamente, características y ventajas técnicas... [Seguir leyendo]

Reivindicaciones:

1. Un sistema de multiplexado de direcciones de memoria de puerto pseudo-dual que comprende:

un componente de memoria;

un registro de retención (101) de la dirección del puerto de lectura operativa para mantener una dirección de lectura en respuesta a una señal de reloj externa; un registro de retención (102) de la dirección del puerto de escritura operativa para mantener una dirección de escritura en respuesta a la señal de reloj externa; un circuito (103) de control que controla el acceso de lectura/escritura a la memoria en base a la supervisión de una primera operación de memoria mediante el envío de la señal de conmutación, en la que dicho circuito (103) de control es operativo también para identificar los modos de operación lectura/escritura, solo lectura y solo escritura; y un multiplexor (104) que conmuta entre una dirección de lectura mantenida y una dirección de escritura mantenida en respuesta a la señal del conmutador desde el circuito (103) de control; en el que una operación de lectura de memoria es una condición o estado de memoria por defecto cuando se espera una próxima señal de reloj externa de modo que la operación de lectura de memoria es una primera operación a ser ejecutada cuando se han de realizar tanto operaciones de lectura como de escritura durante un único ciclo de reloj de la señal del reloj externo; en respuesta a una solicitud de lectura en ausencia de una solicitud de escritura, dicho multiplexor (104) proporciona una dirección de lectura a dicho componente de memoria y dicho circuito (103) de control mantiene una señal de enclavamiento de la dirección del puerto de escritura, de modo que el registro de retención (102) de la dirección del puerto de escritura esté listo para recibir cualquier señal aplicada que pudiera llegar; y en respuesta a una solicitud de escritura en ausencia de una solicitud de lectura, dicho multiplexor (104) proporciona una dirección de escritura a dicho componente de memoria y dicho circuito (103) de control mantiene la señal de enclavamiento de la dirección del puerto de lectura, de modo que el registro de retención (101) de la dirección del puerto de lectura esté listo para recibir cualquier señal aplicada que pudiera llegar y avance una temporización de una operación de escritura de modo que la operación de escritura se inicie antes, durante un ciclo de reloj, que cuando se solicitan tanto operaciones de lectura como de escritura y se realizan en un mismo ciclo de reloj.

2. El sistema de multiplexado de direcciones de memoria de puerto pseudo-dual según la reivindicación 1, en el que:

el registro de retención (101) de la dirección del puerto de lectura se libera tras la operación de lectura, y el registro de retención (102) de la dirección de escritura permanece enclavado después de la operación de lectura.

3. El sistema de multiplexado de direcciones de memoria de puerto pseudo-dual según la reivindicación 2, en el que el registro de retención (102) de la dirección del puerto de escritura se libera tras una operación de escritura.

4. El sistema de multiplexado de direcciones de memoria de puerto pseudo-dual de acuerdo con la reivindicación 1, en el que el circuito (103) de control comprende un circuito (110) de retardo de auto-temporización que crea un retardo de auto-temporización, reafirmando el circuito (103) de control la señal de control interna tras el retardo de auto-temporización para iniciar una segunda operación de memoria.

5. El sistema de multiplexado de direcciones de memoria de puerto pseudo-dual de acuerdo con la reivindicación 1, en el que el circuito (103) de control comprende un circuito (105) de seguimiento de auto-temporización que inicia la generación de la señal de conmutación en respuesta a una finalización detectada de dicha operación de lectura.

6. El sistema de multiplexado de direcciones de memoria de puerto pseudo-dual de acuerdo con la reivindicación 5, en el que la finalización detectada se basa en la supervisión de una línea de bits ficticia.

7. El sistema de multiplexado de direcciones de memoria de puerto pseudo-dual de acuerdo con la reivindicación 1, en el que la primera operación de memoria es una operación de escritura.

8. El sistema de multiplexado de direcciones de memoria de puerto pseudo-dual de acuerdo con la reivindicación 2, en el que dicho multiplexor (104) es operativo para mantener una situación por defecto en la que dicha dirección de lectura se transmite a dicha unidad de dirección de memoria.

9. El sistema de multiplexado de direcciones de memoria de puerto pseudo-dual de acuerdo con la reivindicación 1, que además comprende un pre-decodificador (106) que recibe la dirección de escritura mantenida después de que la operación de lectura esté al menos sustancialmente completada.

10. El sistema de multiplexado de direcciones de memoria de puerto pseudo-dual de acuerdo con la reivindicación 9, que además comprende una puerta (108) que recibe la dirección de escritura desde el pre-decodificador (106) antes de recibir una segunda reafirmación de una señal de reloj interno, siendo una primera reafirmación de la señal de reloj interno sensible a la señal de reloj externo.

11. Un procedimiento de control de una aplicación de una señal de dirección a una memoria que comprende:

el establecimiento de la operación de lectura de memoria como una condición o estado de memoria por defecto cuando se espera una siguiente señal de reloj externo de modo que una operación de lectura de memoria sea una primera operación a ser ejecutada cuando se han de realizar tanto operaciones de lectura como de escritura durante un único ciclo de reloj de la señal de reloj externo; detección de las solicitudes de lectura y escritura; en respuesta a la solicitud de lectura en ausencia de una solicitud de escritura, el suministro de una dirección de lectura a un componente de memoria y el mantenimiento de una señal de enclavamiento de escritura de modo que un registro de retención (102) de la dirección del puerto de escritura esté lista para recibir cualquier señal aplicada que pudiera llegar; en respuesta a una solicitud de escritura en ausencia de una solicitud de lectura, el suministro de una dirección de escritura a dicho componente de memoria y el mantenimiento de una señal de enclavamiento de lectura de modo que un registro de retención (101) de la dirección del puerto de lectura esté listo para recibir cualquier señal aplicada que pudiera llegar y avance unos tiempos de una operación de escritura de modo que la operación de escritura se inicie antes, durante un ciclo de reloj, que cuando se solicitan ambas operaciones de lectura y escritura y se realizan en un mismo ciclo; y en respuesta tanto a una solicitud de lectura como a una solicitud de escritura a ser realizadas durante un único ciclo de reloj, i) suministro de dicha dirección de lectura a dicho componente de memoria, ii) en base a la supervisión de una operación de lectura, determinación de un tiempo dentro de dicho ciclo de reloj único para suministrar dicha dirección de escritura a dicho componente de memoria y iii) conmutación entre dicha dirección de lectura y dicha dirección de escritura para suministrar de ese modo dicha dirección de escritura a dicho componente de memoria en el instante determinado.

12. El procedimiento de acuerdo con la reivindicación 11, que además comprende la generación de una señal de reloj interno que tenga una frecuencia que depende de si ambas solicitudes de lectura y escritura están presentes durante un periodo de tiempo inicial o solamente una de dichas solicitudes de lectura y escritura están presentes durante dicho período de tiempo inicial.

13. El procedimiento de acuerdo con la reivindicación 11, que además comprende la generación de una señal de reloj interno que tenga un periodo dependiente solo de si está presente una solicitud de escritura durante dicho período de tiempo inicial.

14. El procedimiento de acuerdo con la reivindicación 11, en el que dicha determinación incluye:

la detección de una condición de una línea de bits ficticia, y la detección de una finalización de una operación de lectura.

15. El procedimiento de acuerdo con la reivindicación 11 en el que, en respuesta a tanto dicha solicitud de lectura como a dicha solicitud de escritura a ser realizadas durante dicho ciclo de reloj único, dichas direcciones de escritura y lectura se almacenan en registros de retención (101, 102) de direcciones de puertos de lectura y escritura respectivos durante un primer periodo y, durante un periodo inmediatamente posterior, solamente se almacena dicha dirección de escritura en dicho registro de retención (102) de la dirección del puerto de escritura y se libera dicho registro de retención (101) de la dirección del puerto de lectura.

Patentes similares o relacionadas:

Generación de señal de reloj y control para dispositivos de memoria de alto rendimiento, del 19 de Junio de 2019, de QUALCOMM INCORPORATED: Un dispositivo de memoria que comprende: un primer generador de reloj configurado para generar una primera señal de reloj (RCLKb) utilizada para operaciones […]

Sistema y procedimiento de operación de un dispositivo de memoria, del 13 de Mayo de 2015, de QUALCOMM INCORPORATED: Un aparato que comprende: una célula bit acoplada a una primera línea de bit , a una segunda línea de bit , y a una línea de palabra (106, […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]

Difusión general selectiva de datos en dispositivos conectados en serie, del 9 de Abril de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Método para seleccionar un subconjunto de dispositivos de una pluralidad de dispositivos conectados en serie a un controlador de memorias con el fin […]

SISTEMA DE REGISTRO, DISPOSITIVO DE REGISTRO DE DATOS, DISPOSITIVO DE MEMORIA, Y METODO DE REGISTRO DE DATOS, del 1 de Abril de 2008, de SONY CORPORATION: Un sistema de registro de datos que incluye un aparato de memoria desmontable y un aparato de registro de datos operable para escribir datos en el aparato de […]

SISTEMA DE REGISTRO, DISPOSITIVO DE REGISTRO DE DATOS, DISPOSITIVO DE MEMORIA, Y METODO DE REGISTRO DE DATOS, del 1 de Abril de 2008, de SONY CORPORATION: Un sistema de registro de datos que incluye un aparato de memoria desmontable y un aparato de registro de datos operable para escribir datos en el aparato de […]

Sistema de memoria de múltiples flujos de instrucciones, del 6 de Mayo de 2020, de QUALCOMM INCORPORATED: Un dispositivo de memoria que comprende: un decodificador ; una pluralidad de células de memoria , en el que cada una de las células […]