Método y dispositivo para generar identificadores y números verdaderamente aleatorios.

La presente invención tiene por objeto un método que consta de dos etapas:

una primera etapa de clasificación de las celdas de memoria estáticas en dos conjuntos disjuntos según su comportamiento ante repetidas veces en que se conectan a alimentación tras haber estado un tiempo suficiente sin alimentación, de manera que las celdas de uno de los conjuntos son adecuadas para generar identificadores (claves o secretos) y las del otro son adecuadas para generar números verdaderamente aleatorios. Gracias a esta clasificación, en la segunda etapa de generación de números, los identificadores así como los números aleatorios generados ofrecen mejores prestaciones. También es objeto de la invención el dispositivo para implementar el método propuesto que puede realizarse añadiendo circuitería muy simple a la memoria o ejecutando un software muy sencillo. Las áreas científico-técnicas a las que se puede corresponder el invento son las de Criptografía, Tecnología Electrónica, Seguridad y Privacidad.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201400225.

Solicitante: UNIVERSIDAD DE SEVILLA.

Nacionalidad solicitante: España.

Inventor/es: BATURONE CASTILLO,María Iluminada, EIROA LORENZO,Susana, PRADA DELGADO,Miguel Ángel.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F7/58 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Generadores de números aleatorios o seudoaleatorios.

PDF original: ES-2548792_A1.pdf

Fragmento de la descripción:

Método y dispositivo para generar identificadores y números verdaderamente aleatorios

5 Objeto de la invención

La presente invención tiene por objeto un método que consta de dos etapas: una primera etapa de clasificación de las celdas de memoria estáticas en dos conjuntos disjuntos según su comportamiento ante repetidas veces en que se conectan a alimentación tras haber estado un tiempo suficiente sin alimentación, de manera que 10 las celdas de uno de los conjuntos son adecuadas para generar identificadores (claves o secretos) y las del otro son adecuadas para generar números verdaderamente aleatorios. Gracias a esta clasificación, en la segunda etapa de generación de números, los identificadores así como los números aleatorios generados ofrecen mejores prestaciones. También es objeto de la invención el dispositivo para 15 implementar el método propuesto que puede realizarse añadiendo circuitería muy simple a la memoria o ejecutando un software muy sencillo. Las áreas científico- técnicas a las que se puede corresponder el invento son las de Criptografía, Tecnología Electrónica, Seguridad y Privacidad.

20 Estado de la técnica

Las celdas de memoria estáticas se caracterizan porque poseen dos estados estables, de forma que mantienen el dato binario (valor lógico "0" ó "1") que se les escribe mientras están alimentadas, pero pierden la información si se les interrumpe la alimentación. Si se alimentan pero no se les escribe ningún dato, las celdas 25 evolucionan hacia un valor u otro de una forma que es difícil de predecir, modelar matemáticamente y clonar físicamente, por lo que es muy difícil obtener un conjunto de celdas que se comporten de la misma forma. Aprovechando estas características, estas celdas se han empleado para generar identificadores de circuitos y números verdaderamente aleatorios.

30 Las celdas de memoria estáticas están constituidas por circuitos acoplados en cruz, como latches, flip-flops, puertas ÑOR, inversores, etc. En [Kumar2008] se proponen celdas basadas en dos latches en cruz para identificar FPGAs. En [Maes2008] se

propone el uso de flip-flops para identificar FPGAs. En [Su2008] se proponen celdas basadas en dos puertas ÑOR en cruz para identificar circuitos integrados de aplicaciones específicas. En [Layman2004] se propone un método que emplea celdas basadas en dos inversores en cruz (las típicas que forman las memorias estáticas de acceso aleatorio, SRAMs) para identificar las obleas de circuitos integrados y/o los dados en que se divide cada oblea.

En aplicaciones de identificación, se suele usar una técnica reto-respuesta con las celdas de memoria para identificar el dispositivo en el que esté incluida la memoria, de modo que el reto sean las celdas que se van a emplear y las respuestas sean los valores a los que se estabilizan las celdas cuando se les conecta la alimentación [Guajardo2007] [Holcomb2009] [Kim2010] [Gebara2012]. También se han propuesto otros métodos que combinan las respuestas de las celdas. En estas aplicaciones siempre es necesaria una etapa de registro en la que a cada dispositivo se le asigna un identificador, ID. En la etapa de identificación, se calcula la distancia (normalmente una distancia de Hamming, HD) entre el ID generado por el dispositivo y los registrados y se identifica el dispositivo como aquel cuyo ID registrado presente la menor distancia. En aplicaciones de autenticación solo se registra un dispositivo, de modo que en la etapa de autenticación se calcula la distancia entre el ID generado y el registrado y si la distancia está por debajo de un umbral, el dispositivo se considera auténtico, y si no, el dispositivo se considera falso. La calidad de una técnica de identificación/autenticación se suele evaluar midiendo las razones de falso rechazo (FRR, "False Rejection Rate") y de falsa aceptación (FAR, "False Acceptance Rate") para cada valor de umbral elegido. Lo ideal es que exista al menos un valor de umbral para el que no haya dispositivos auténticos rechazados como falsos (FRR=0) y, a la vez, no haya dispositivos falsos aceptados como auténticos (FAR=0). De forma equivalente, también se representan los porcentajes de población genuina (auténtica) e impostora frente a cada valor de umbral elegido. Lo ideal es que ambas poblaciones estén claramente separadas.

En aplicaciones de identificación/autenticación interesa que las celdas proporcionen siempre el mismo valor. Sin embargo, hay celdas que proporcionan un valor en la etapa de identificación distinto al que se les asignó en la etapa de registro. Hay celdas de memoria que presentan una tendencia clara a estabilizarse en un valor u otro y celdas que no presentan ninguna tendencia clara (su valor de inicialización es distinto cada vez que se las alimenta). En [Holcomb2009] las celdas de SRAMs se clasifican dependiendo de sus curvas de transferencia de tensión ("Voltage Transfer Curves" o

VTCs) en celdas asimétricas ("skewed cells"), que presentan una probabilidad mayor para estabilizarse en un valor que en otro, y celdas simétricas ("neutral cells"), que no presentan ninguna tendencia clara a un valor u otro. Uno de los motivos por los que una celda es de un tipo u otro son las variaciones que haya habido en el proceso de fabricación de la memoria, que dan lugar a que los dos circuitos en cruz constitutivos de cada celda no sean perfectamente idénticos. Las celdas que son asimétricas por este motivo son las más adecuadas a la hora de generar identificadores pues caracterizan la naturaleza intrínseca, única e irrepetible de la memoria. Pero las variaciones en el proceso de fabricación no son el único motivo. Las memorias presentan remanencia, es decir, valores previos almacenados en las celdas pueden influir en los valores futuros a los que evolucionen las celdas si el tiempo que está la memoria apagada es corto. Aunque esta influencia se puede eliminar si el tiempo de apagado es suficiente (por ejemplo unas pocas decenas de segundos). Por otro lado, en el caso de SRAMs, se ha estudiado que el envejecimiento y el efecto NBTI (Negative Bias Temperature Instability), consecuencia de un uso prolongado de la SRAM, también provocan que una celda sea asimétrica o simétrica [Guajardo2007] [Holcomb2009], Mucho más influyente que el motivo anterior a la hora de modificar el comportamiento de las celdas son las condiciones de operación, sobre todo la temperatura. La temperatura influye en las tensiones umbrales y en la movilidad electrón-hueco de los transistores CMOS que forman cada celda de memoria, de manera que un cambio de temperatura puede convertir una celda asimétrica en simétrica y viceversa [Kim2010] [Gebara2012], Las variaciones en la tensión de alimentación también influyen considerablemente porque modifican el margen de ruido estático (Static Noise Margin, SNM) de las celdas, haciendo que sean más o menos susceptibles al ruido [Holcomb2009].

Para reducir el problema de celdas que proporcionan un valor en la etapa de identificación distinto al que se les asignó en la etapa de registro se han propuesto distintas soluciones. La propuesta en [Holcomb2009] es promediar los valores a los que se estabilizan un conjunto dado de celdas de SRAMs para un número dado de medidas realizadas a la temperatura y tensión de alimentación nominales y, en base al promedio obtenido, asignar a cada celda el valor binario más probable para formar con ellos el identificador registrado. La propuesta en [Kim2010] es generar un identificador como en [Holcomb2009], pero no un solo identificador obtenido en condiciones de operación nominales, sino generar varios identificadores para varias condiciones de operación, fundamentalmente para varias temperaturas. Cuantos más IDs se registren

por cada SRAM, uno para cada temperatura, mejor será la caracterización de la SRAM. Como solución de compromiso entre buena caracterización y etapa de registro no demasiado costosa, se propone generar un ID para la máxima temperatura de operación, otro para la mínima y otro para el valor intermedio. La propuesta en [Gebara2012] extiende el trabajo en [Kim2010] y caracteriza las celdas de memoria alimentándolas con varios valores de tensión (desde 0.2Vdd a 1.4Vdd, con Vdd el valor nominal) durante un tiempo (aproximadamente 1 microsegundo) y luego ajustando la alimentación a su valor nominal antes de leer los valores a los que se estabilizan las celdas. Se realizan varias medidas a cada valor de tensión de alimentación y para cada valor de temperatura. La información que se almacena en la etapa de registro es, no solo el ID más probable por cada temperatura, sino también la probabilidad de cada celda de estabilizarse en un valor u otro. Incluso introducen la posibilidad de no usar las celdas de memoria cuyos valores cambien en distintas condiciones... [Seguir leyendo]

Reivindicaciones:

1Método para generar al menos un número de identificación de n bits y al menos un número verdaderamente aleatorio de m bits a partir de N celdas de memoria estáticas teniendo cada celda capacidad de almacenar un bit de información, en el cual n puede tomar valores desde 0 hasta N-m y m puede tomar valores desde 0 hasta N-n,

estando el método caracterizado porque comprende una primera fase en la que se clasifican las N celdas de memoria en al menos dos grupos etiquetados como A y B, y una segunda fase en la que se generan al menos un número de identificación de n bits a partir de n celdas etiquetadas en la primera fase como A y al menos un número verdaderamente aleatorio de m bits a partir de m celdas etiquetadas en la primera fase como B, donde la primera fase de clasificación se lleva a cabo al menos una vez, de forma que, una vez clasificadas las celdas, la generación de números de identificación y aleatorios se puede llevar a cabo directamente ejecutando la segunda fase sin tener que volver a ejecutar la primera fase;

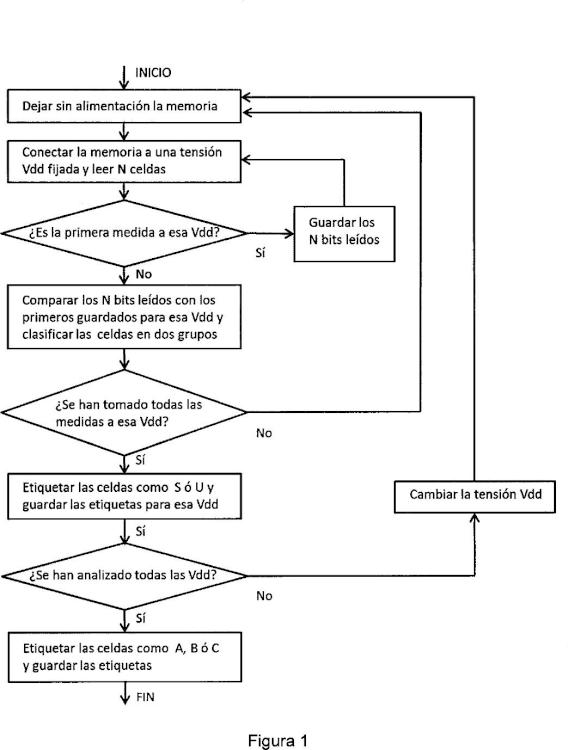

donde la primera fase del método a su vez comprende:

(a) dejar sin alimentación a la memoria (y, por tanto, a sus celdas) durante un tiempo suficiente para que desaparezcan todos los valores de los bits que pudieran estar almacenados,

(b) conectar la memoria a una tensión de alimentación fijada y leer los valores de los bits a los que se han estabilizado N celdas de memoria sin antes haber escrito nada en ellas,

(c) guardar los valores de los bits leídos de las N celdas,

(d) dejar sin alimentación a la memoria durante el tiempo suficiente para borrar los valores almacenados,

(e) alimentar de nuevo la memoria con el mismo valor de tensión y volver a leer los valores de bits de las N celdas sin antes haber escrito nada en ellas,

(f) comparar los valores de bits obtenidos en el paso (e) con los guardados en el paso (c), clasificando las celdas de memoria en dos grupos: las celdas que siempre proporcionan el mismo valor de bit y las celdas que alguna vez han proporcionado un valor de bit diferente,

(g) ir al paso (h) si ya se han tomado todas las medidas para el mismo valor de tensión de alimentación fijado; mientras que, en otro caso, volver al paso (d),

(h) etiquetar las celdas que siempre han proporcionado el mismo valor de bit para todas las medidas realizadas a un mismo valor de tensión como S, etiquetar las otras

5 celdas como U y guardar el resultado de la clasificación para el valor de tensión analizada,

(i) ir al paso 0) si ya se han analizado todos los valores de tensión de alimentación; mientras que, en otro caso, fijar un nuevo valor de tensión de alimentación a analizar y volver al paso (a),

10 G) comparar los resultados de clasificación obtenidos para los valores de tensión analizados y etiquetar las celdas de memoria que han sido etiquetadas siempre como S con todos los valores de tensión analizados con una etiqueta A y etiquetar las celdas que han sido etiquetadas siempre como U con todos los valores de tensión analizados con una etiqueta B (asignando una etiqueta C a las celdas que no se les asigna una 15 etiqueta A ni B);

y donde la segunda fase del método a su vez comprende:

(1) dejar sin alimentación a la memoria (y, por tanto, a sus celdas) durante un tiempo suficiente para que desaparezcan todos los valores de bits que pudieran estar almacenados,

20 (2) alimentar la memoria a su valor de tensión nominal, no escribir nada en las N

celdas analizadas en la primera fase y generar una secuencia de bits (cadena-A) con los valores de bits a los que se hayan estabilizado las celdas etiquetadas como A y generar otra secuencia de bits (cadena-B) con los valores de bits de las celdas etiquetadas como B, finalizando la lectura cuando al menos se tenga una cadena-A de 25 n bits y una cadena-B de m bits,

(3) utilizar la cadena-A para generar al menos un número de identificación digital de n bits y la cadena-B para generar al menos un número verdaderamente aleatorio de m bits.

2. Método según la reivindicación 1 caracterizado porque en una primera fase se analizan P valores de tensión de alimentación (siendo P mayor o igual a 1), de los cuales al menos uno es el valor de tensión nominal (Vdd).

3. Método según una cualquiera de las reivindicaciones 1 a 2, caracterizado porque al repetirse la primera fase del método, se etiquetan con una etiqueta A las celdas que en la anterior primera fase se etiquetaron con A y en la actual primera fase del método vuelven a etiquetarse como A; se etiquetan con una etiqueta B las celdas que en la anterior primera fase se etiquetaron con B y en la actual primera fase del método vuelven a etiquetarse como B y se etiquetan con una etiqueta C el resto de las celdas.

4.- Método según una cualquiera de las reivindicaciones 1 a 2, caracterizado porque al realizarse la primera fase del método sin indicar que sea una repetición, se borra cualquier resultado de posibles clasificaciones anteriores y se almacena el resultado de la clasificación actual.

5. Dispositivo para implementar el método según se define en las reivindicaciones 1 a 4 que presenta al menos dos modos de operación seleccionables: modo de etiquetado de celdas de memoria y modo de generación de números, donde el modo de generación de números funciona correctamente si previamente se ha llevado a cabo el modo de etiquetado al menos una vez; estando dicho dispositivo caracterizado porque comprende:

una memoria estática (1),

un bloque de tensión (2) que deja de alimentar a la memoria (1) o la alimenta a un valor de tensión determinado,

un bloque de clasificación (3) que, si el modo de operación es el de etiquetado, analiza a qué celdas de la memoria (1) asignarles la etiqueta Aya cuáles la etiqueta B, y, si el modo de operación es el de generación de números, envía el resultado de la clasificación al bloque de control (4);

un bloque de control (4) que controla todos los demás bloques para ejecutar los pasos del método, de modo que: (a) indica al bloque de tensión (2) cuándo no alimentar a la memoria (1) y cuándo alimentarla y, en tal caso, fija el valor de la

tensión de alimentación; (b) habilita la lectura de la memoria (1) y activa las señales específicas de la lectura de las celdas de memoria; (c) indica al bloque de clasificación (3) el modo de operación y, si el modo de operación es el de generación de números, (d) emplea la información almacenada del modo de etiquetado para leer los bits generados por las celdas de memoria con etiqueta A y generar con ellos identificadores y los bits generados por las celdas con etiqueta B y generar con ellos números aleatorios.

6. Dispositivo según reivindicación 5 caracterizado porque la memoria estática (1) es una memoria estática de acceso aleatorio, SRAM.

7. Dispositivo según cualquiera de las reivindicaciones 5 a 6 caracterizado porque el bloque de tensión (2) comprende:

un interruptor controlado por una señal digital del bloque de control (4) que cierra o abre el interruptor para alimentar o no a la memoria (1) y

un potenciómetro controlado digitalmente por el bloque de control (4) para modificar el valor de la tensión que alimenta a la memoria (1), en el caso de analizar más de un valor de tensión de alimentación (en el caso de analizar solo el valor de tensión nominal no es necesario el potenciómetro).

8. Dispositivo según cualquiera de las reivindicaciones 5 a 7 caracterizado porque el bloque de clasificación (3) comprende:

una memoria o registros para almacenar los N bits leídos de la memoria (1) en la primera medida realizada a una tensión de alimentación, borrándose los anteriormente almacenados;

operadores XOR destinados a comparar los bits leídos de la memoria (1) en cada medida con los bits almacenados de la primera medida realizada al mismo valor de tensión de alimentación, resultando valores lógicos "O" si los valores de los bits de ambas lecturas coinciden y valores "1" si los valores no coinciden;

operadores OR destinados a ir combinando los resultados de los operadores XOR anteriores obtenidos sobre medidas al mismo valor de tensión de

alimentación, resultando un valor lógico "0" para una celda que siempre va proporcionando el mismo valor de bit en todas las medidas y un valor lógico "1" para una celda que alguna vez haya proporcionado un valor de bit diferente;

una memoria o registros destinados a almacenar NxP bits (N bits por cada uno de los P valores de tensión de alimentación analizados), cada bit de los N etiquetando una de las N celdas de memoria analizadas, de modo que el valor del bit indica si la celda ha sido etiquetada como S (valor del bit "0") o como U (valor del bit "1") para cada valor de tensión, de modo que, en el caso de analizar un único valor de tensión, a una celda etiquetada como S se le asigna el código de la etiqueta Aya una celda etiquetada como U se le asigna el código de la etiqueta B;

operadores ÑOR, en el caso de analizar P>1 valores de tensión de

alimentación, destinados a combinar P bits de etiquetas por cada celda, de forma que si resulta un valor lógico "1", a la celda se le asigna el código de la etiqueta A;

operadores AND, en el caso de analizar P>1 valores de tensión de

alimentación, destinados a combinar P bits de etiquetas por cada celda, de forma que si resulta un valor lógico "1", a la celda se le asigna el código de la etiqueta B;

una memoria o registros para almacenar 2N bits, en el caso de analizar P>1 valores de tensión de alimentación, cada 2 bits codificando si cada una de las N celdas de memoria analizadas posee la etiqueta A, B ó ninguna de ellas.

operadores XOR destinados a comparar las etiquetas asociadas a las N celdas obtenidas en el modo de operación de etiquetado actual con las etiquetas obtenidas en modo(s) de operación de etiquetado anteriores.

9. Dispositivo según cualquiera de las reivindicaciones 5 a 8 caracterizado porque el bloque de control (4) comprende:

contadores para medir: (a) el tiempo que se deja al bloque de memoria (1) sin alimentar, (b) las medidas que se llevan a cabo por cada valor de tensión de alimentación, (c) el número de los valores de tensión a analizar, en el caso de analizar varias tensiones de alimentación, (d) las celdas de memoria que se analizan, (e) el número de bits para generar identificadores y (f) el número de bits para generar números aleatorios;

un bloque que traduce en direcciones de acceso a la memoria (1) las etiquetas asociadas a las N celdas.

10. Dispositivo según cualquiera de las reivindicaciones 5 a 9 en el que, al configurar el modo de operación de etiquetado, el bloque de control (4) recibe como parámetros de configuración al menos el número N de celdas de memoria a analizar, el número P de tensiones de alimentación a fijar, el número Q de medidas a realizar por cada tensión de alimentación y una señal binaria REP, que indica si se repite el etiquetado o no, y recibe una señal de inicio, INIT, que inicializa a cero todos los contadores y que marca el comienzo del proceso de etiquetado, de modo que el bloque de control (4), para cada una de las tensiones a analizar, indica al bloque de tensión (2) que no alimente la memoria (1) durante el tiempo necesario, que está controlado por uno de los contadores del bloque de control; transcurrido ese tiempo, el bloque de control (4) indica al bloque de tensión (2) que alimente la memoria (1) al valor de tensión determinado y activa las señales específicas de la lectura de datos en la memoria (1) para leer los bits a los que se han estabilizado N celdas de memoria, dependiendo el mecanismo de lectura de las señales de entrada y de la memoria (1), dependiendo la temporización de dicha lectura del tipo de memoria empleada, y controlando uno de los contadores del bloque de control (4) cuándo se finaliza la lectura de N celdas al menos; además, el bloque de control (4) indica al bloque de clasificación (3) que opere en modo de etiquetado, de manera que el bloque de clasificación (3) recibe los N bits de la memoria (1), almacenando los bits correspondientes a la primera medida de cada tensión de alimentación y comparando con ellos los sucesivos N bits leídos en las sucesivas medidas, empleando operadores XOR para la comparación, y combinando con operadores OR los resultados para cada celda obtenidos de las operaciones XOR, resultando un valor lógico "O" para las celdas que siempre proporcionan el mismo valor de bit en las sucesivas medidas y un valor lógico "1" para las celdas que han cambiado alguna vez el valor de bit proporcionado en las sucesivas medidas, almacenando esos resultados en una memoria o registros de N bits asociados con la tensión de alimentación analizada; de modo que cuando el contador del bloque de control (4) que cuenta las medidas analizadas a ese valor de tensión llega al valor de cuenta Q configurado, si P=1 y REP=0 (el etiquetado no se repite), el bloque de control (4) indica al bloque de clasificación (3) que almacene en una memoria o registros de 2N bits, de forma ordenada, las N etiquetas codificadas con 2 bits de las N celdas, de forma que el bloque de clasificación (3) almacena los 2 bits que indican la etiqueta A para las celdas que siempre proporcionaron el mismo valor

de bit (resultaron un valor lógico "0" tras la operación OR) y almacena los 2 bits que indican la etiqueta B para las celdas que cambiaron alguna vez el valor de bit proporcionado (resultaron un valor lógico "1" tras la operación OR); y si REP=1 y N mantiene su valor (el etiquetado se repite), el bloque de control (4) indica al bloque de clasificación (3) que compare de forma ordenada y mediante operadores XOR si cada etiqueta obtenida para cada celda es A ó B, como en etiquetados anteriores, en cuyo caso se mantienen almacenadas en la memoria o registros de 2N bits las correspondientes etiquetas A ó B, mientras que si la nueva etiqueta obtenida no es ni A ni B o no coinciden con las anteriores las nuevas etiquetas obtenidas, entonces se almacenan para esa celda 2 bits que indican la etiqueta C; mientras que si P>1, el bloque de control (4) inicia otras Q medidas, inicializando los contadores que cuentan el número de celdas a analizar y el número de medidas a realizar, indicando al bloque de tensión (2) el siguiente valor de tensión a analizar; repitiéndose el proceso hasta que el contador del bloque de control (4) que cuenta los valores de tensión analizados llega al valor de cuenta P configurado, en cuyo caso, el bloque de control (4) indica al bloque de clasificación (3) que combine los P grupos de N bits almacenados para cada tensión de alimentación analizada mediante operadores ÑOR y AND y almacene en una memoria o registros de 2N bits, de forma ordenada, las N etiquetas codificadas con 2 bits de las N celdas, de forma que el bloque de clasificación (3), si REP=0, almacena los 2 bits que indican la etiqueta A para las celdas que siempre proporcionaron el mismo valor de bit para todas las medidas y todas las tensiones (resultaron un valor lógico "1" tras la operación ÑOR), almacena los 2 bits que indican la etiqueta B para las celdas que cambiaron alguna vez el valor de bit proporcionado para todas las tensiones (resultaron un valor lógico "1" tras la operación AND), y almacena 2 bits que indican la etiqueta C, para el resto de las celdas, y si REP=1 y el valor de N se mantiene, el bloque de control (4) indica al bloque de clasificación (3) que compare de forma ordenada y mediante operadores XOR si cada etiqueta obtenida para cada celda es A ó B, como en etiquetados anteriores, en cuyo caso se mantienen almacenadas en la memoria o registros de 2N bits las correspondientes etiquetas A ó B, mientras que si la nueva etiqueta obtenida no es ni A ni B o no coinciden con las anteriores las nuevas etiquetas obtenidas, se almacenan para esa celda los 2 bits que indican la etiqueta C; de forma que, cuando el proceso de etiquetado ha finalizado, el bloque de control (4) lo indica mediante una señal binaria FIN.

11. Dispositivo según cualquiera de las reivindicaciones 5 a 10 en el que, al configurar el modo de operación de generación de números, el bloque de control (4) recibe como parámetros de configuración al menos el tamaño en bits, n, del identificador a generar y el tamaño en bits, m, del número aleatorio a generar, y recibe una señal de inicio, INIT, que inicializa a cero todos los contadores y marca el comienzo del proceso de generación, de modo que el bloque de control (4) indica al bloque de tensión (2) que no alimente la memoria (1) durante el tiempo necesario, que está controlado por uno de los contadores del bloque de control; transcurrido ese tiempo (o bien si la memoria ya llevaba al menos ese tiempo desconectada de la alimentación) el bloque de control (4) indica al bloque de tensión (2) que alimente la memoria al valor de tensión nominal e indica al bloque de clasificación (3) que le envíe las etiquetas asociadas a las N celdas, de modo que son traducidas a direcciones de acceso a las celdas de tipo A y B de la memoria (1); empleando esa información, el bloque de control activa las señales específicas de la lectura de datos en las celdas de tipo A y B de la memoria (1), dependiendo el mecanismo de lectura de las señales de entrada y de la memoria (1) y dependiendo la temporización de dicha lectura del tipo de memoria empleada, y el bloque de control (4) concatena los bits generados por celdas etiquetadas como A en la cadena-A y los bits generados por celdas etiquetadas como B en la cadena-B; de forma que uno de los contadores del bloque de control cuenta n bits de la cadena-A, que el bloque de control los proporciona como identificador y uno de los contadores del bloque de control cuenta m bits de la cadena-B, que el bloque de control los proporciona como número verdaderamente aleatorio; de manera que, cuando el proceso de generación de números ha finalizado, el bloque de control (4) lo indica mediante una señal binaria FIN.

Patentes similares o relacionadas:

Método para generar números aleatorios y generador de número aleatorio asociado, del 19 de Febrero de 2020, de Quantum Numbers Corp: Un método para generar al menos un número aleatorio, el método comprende los pasos de: generar una corriente de tunelización de cargas desde […]

Procedimiento y sistema de generación de bits cuánticos aleatorios, del 17 de Julio de 2019, de Quantum Numbers Corp: Un procedimiento para generar una muestra de bits aleatorios mediante el uso de una barrera de tunelización cuántica que comprende un aislante intercalado […]

PROCESO PARA LA GENERACIÓN FÍSICA DE NÚMEROS ALEATORIOS UTILIZANDO UN LÁSER EMISOR DE SUPERFICIE DE CAVIDAD VERTICAL, del 9 de Mayo de 2019, de FUNDACIÓ INSTITUT DE CIÈNCIES FOTÒNIQUES: Procedimiento para la generación física de números aleatorios que comprende los pasos de: - modular la ganancia de un láser emisor de superficie de cavidad vertical periódicamente […]

Generador de números aleatorios verdaderos, del 13 de Marzo de 2019, de Trentino Sviluppo S.p.A: Un generador de números aleatorios del tipo que comprende:

- una fuente de fotones;

- uno o más detectores de fotones del tipo SPAD configurados […]

Generador de números aleatorios verdaderos, del 13 de Marzo de 2019, de Trentino Sviluppo S.p.A: Un generador de números aleatorios del tipo que comprende:

- una fuente de fotones;

- uno o más detectores de fotones del tipo SPAD configurados […]

Dispositivo y método para generar una clave de identificación, del 9 de Enero de 2019, de ICTK Holdings Co., Ltd: Un aparato para generar una clave de identificación, el aparato comprende: un generador de claves configurado para generar un bit digital basado en si […]

Autenticación de suministro de a través de respuesta al desafío de temporización, del 11 de Diciembre de 2018, de HEWLETT-PACKARD DEVELOPMENT COMPANY, L.P.: Un dispositivo de suministro reemplazable que incluye una CPU y una memoria , la memoria almacenando una clave de base , […]

Procedimiento y aparato para generador de números aleatorios, del 13 de Septiembre de 2017, de QUALCOMM INCORPORATED: Un procedimiento para generar números aleatorios para su uso en un dispositivo de comunicación inalámbrica, generándose los números aleatorios en un generador […]

Procedimiento y equipo para generar números aleatorios utilizando la arquitectura de un doble oscilador y caos de tiempo continuo, del 19 de Julio de 2017, de TUBITAK: Generador de bits aleatorios que incluye una arquitectura de doble oscilador que comprende un oscilador rápido con frecuencia rápida f(fast) […]