Procedimiento y aparato de adición de una señal aleatoria en convertidores de digital a analógico Sigma-Delta de bit múltiple.

Un aparato para la reducción de los tonos de inactividad no deseados mediante la adición de una señal aleatoria a una señal digital en un convertidor de digital a analógico Sigma-Delta de bit múltiple (DAC),

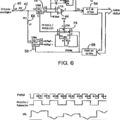

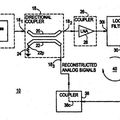

que comprende: un modulador de bits múltiples Sigma-Delta (202; 502) que tiene una entrada y una salida de señal digital (212; 512), el modulador Sigma-Delta de bit múltiple (202; 502) comprendiendo: un filtro de bucle digital (110; 510) que recibe la señal de entrada digital, y que convierte la señal a palabras digitales de L bit en secuencia; y el cuantificador de resolución variable (208; 508) que recibe las palabras digitales de L bit en una secuencia y que emite una palabra digital respectiva de M bit; en donde M > 1 y L > M; el aparato comprendiendo además un convertidor de digital a analógico de bit múltiple (DAC) que tiene una salida analógica y una entrada digital que recibe la palabra digital respectiva de M bit; y un filtro analógico de paso bajo (106; 105) que tiene una entrada analógica acoplada a la salida analógica del DAC de bit múltiple; el filtro de paso bajo analógico emite una señal de salida analógica respectiva;

el aparato se caracteriza porque,

el modulador de múltiples bits sigma delta (202; 502) comprende además un generador de secuencia aleatoria (214; 514), el generador de secuencia aleatoria (214; 514) genera una pluralidad de números aleatorios N(n) en una secuencia, en donde cada número aleatorio N(n) es un número entero aleatorio entre 1 y M;

y el cuantificador de resolución variable (208; 508) se controla por el generador de secuencia aleatoria (214; 514) y adaptado para reducir la resolución de la palabra digital respectiva de L bit a una palabra digital respectiva de N(n) bits en función del respectivo número aleatorio N(n); y cuando M es mayor que el respectivo número aleatorio N(n), añadir M-N(n) bits menos significativos, comprendiendo cada uno un cero, a esta palabra digital respectiva de N(n) bits para generar la palabra de M-bit respectiva.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2009/061599.

Solicitante: MICROCHIP TECHNOLOGY INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 2355 WEST CHANDLER BOULEVARD CHANDLER, ARIZONA 85224-6199 ESTADOS UNIDOS DE AMERICA.

Inventor/es: QUIQUEMPOIX,VINCENT, DEVAL,PHILIPPE, BARRETO,ALEXANDRE.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M3/04 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 3/00 Conversión de valores analógicos en, o a partir de una modulación diferencial. › Modulación diferencial con varios bits.

PDF original: ES-2622145_T3.pdf

Patentes similares o relacionadas:

CONVERSION MULTI-BIT DE ANALOGICO A DIGITAL CON MODULACION SIGMA-DELTA, del 3 de Noviembre de 2009, de NELLCOR PURITAN BENNETT LLC: Un aparato oxímetro que comprende: un modulador sigma-delta con una entrada acoplada para recibir una señal de sensor analógico y que comprende adicionalmente integradores […]

CONVERSION MULTI-BIT DE ANALOGICO A DIGITAL CON MODULACION SIGMA-DELTA, del 3 de Noviembre de 2009, de NELLCOR PURITAN BENNETT LLC: Un aparato oxímetro que comprende: un modulador sigma-delta con una entrada acoplada para recibir una señal de sensor analógico y que comprende adicionalmente integradores […]

CORRECCION DE MODULADORES SIGMA-DELTA MULTIBITS MEDIANTE UN FILTRO NO LINEAL., del 1 de Septiembre de 2006, de LOCKHEED MARTIN CORPORATION: UN CONVERTIDOR ANALOGICO/DIGITAL SI - DE (CAD) INCLUYE UN MODULADOR MULTIBITS SI - DE 216 Y UN BUCLE DE REALIMENTACION 240, 241 QUE INCLUYE UN CONVERTIDOR […]

RECEPTOR A RAFAGAS CON DEMODULACION DIFERENCIAL., del 1 de Junio de 1997, de ALCATEL STANDARD ELECTRICA, S.A.: RECEPTOR A RAFAGAS CON DEMODULACION DIFERENCIAL. DE ESPECIAL APLICACION EN SISTEMAS DIGITALES DE RADIOCOMUNICACIONES CON ACCESO MULTIPLE POR […]

PROCEDIMIENTO PARA LA REDUCCION DE DATOS EN EL PROCESAMIENTO DIGITAL DE UNA SUCESION DE VALORES DE SEÑAL., del 1 de Mayo de 1996, de SIEMENS AKTIENGESELLSCHAFT: LA INVENCION SE REFIERE A UN PROCEDIMIENTO PARA LA REDUCCION DE DATOS EN EL PROCESAMIENTO DE UNA SUCESION DE VALORES DE SEÑAL CON FORMACION […]

UN CONVERTIDOR DIGITAL A ANALOGICO QUE UTILIZA MODULACION SIGMADELTA PARA SISTEMAS TELEFONICOS, del 16 de Agosto de 1981, de STANDARD ELECTRICA, S.A.: CONVERTIDOR DIGITAL ANALOGICO PARA SISTEMAS TELEFONICOS. EL SISTEMA TRATA LA SEÑAL DIGITAL (XN) CONVERTIDA, CON UNA CADENCIA DE PALABRA DADA, […]

CONVERTIDOR ANALOGICO-DIGITAL SIGMA-DELTA DE BAJO RUIDO, del 1 de Julio de 2007, de LOCKHEED MARTIN CORPORATION: SE DESCRIBE UN DISPOSITIVO CONVERTIDOR , DE REALIMENTACION ANALOGICA/DIGITAL Y DEL TIPO SIGMA - DELTA, QUE CONSIGUE UN BAJO RUIDO Y UNA AMPLIA GAMA DINAMICA […]

CONVERTIDOR ANALOGICO-DIGITAL SIGMA-DELTA DE BAJO RUIDO, del 1 de Julio de 2007, de LOCKHEED MARTIN CORPORATION: SE DESCRIBE UN DISPOSITIVO CONVERTIDOR , DE REALIMENTACION ANALOGICA/DIGITAL Y DEL TIPO SIGMA - DELTA, QUE CONSIGUE UN BAJO RUIDO Y UNA AMPLIA GAMA DINAMICA […]