Pastilla de señal de circuito integrado con tolerancia a cinco voltios con asistencia de tres voltios.

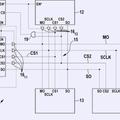

Un circuito integrado que opera a un voltaje de operación nominal (VDD) con una pastilla de señal (140) y un circuito de control (100) acoplado a la pastilla de señal (140),

comprendiendo el circuito de control (100):

un primer transistor semiconductor de óxido metálico de canal N (NMOS) (142) que tiene un drenaje acoplado a la pastilla de señal de circuito integrado (140) y una compuerta acoplada al voltaje de operación nominal (VDD);

un segundo transistor NMOS (128) que tiene una fuente acoplada a un común de potencia (130) y un drenaje acoplado a una fuente del primer transistor NMOS (142);

un primer transistor semiconductor de óxido metálico de canal P (PMOS) (126) que tiene un drenaje acoplado a la pastilla de señal (140) de circuito integrado;

un segundo transistor PMOS (124) que tiene un drenaje acoplado a una fuente del primer transistor PMOS (126), y una fuente del segundo transistor PMOS (124) acoplada al voltaje de operación nominal (VDD); un tercer transistor PMOS (122) que tiene un drenaje acoplado a la pastilla de señal de circuito integrado (140) y una fuente acoplada a una compuerta del segundo transistor PMOS (124);

un cuarto transistor PMOS (114) que tiene un drenaje acoplado a la compuerta del segundo transistor PMOS (124) y la fuente del tercer transistor PMOS (122), teniendo el cuarto transistor PMOS (114) una fuente acoplada a una señal de control (108);

un tercer transistor NMOS (116) que tiene un drenaje acoplado a la compuerta del segundo transistor PMOS (124) y la fuente del tercer transistor PMOS (122), teniendo el tercer transistor NMOS (116) una compuerta acoplada al voltaje de operación nominal y una fuente acoplada a la señal de control (108); un cuarto transistor NMOS (120) que tiene una fuente acoplada a la pastilla de señal de circuito integrado (140);

un quinto transistor PMOS (118) que tiene una fuente acoplada a la pastilla de señal de circuito integrado (140) y una compuerta acoplada al voltaje de operación nominal (VDD);

los drenajes del cuarto transistor NMOS (120) y del quinto transistor PMOS (118) están acoplados a una compuerta del cuarto transistor PMOS (114); una compuerta del primer transistor PMOS (126) está acoplada a una señal de salida de datos (110);

caracterizado porque

la señal de control es una señal de control (108) que cuando se establece proporciona una tolerancia a cin30 co voltios de la pastilla de señal de circuito integrado (140);

la compuerta del cuarto transistor NMOS (120) está acoplada al voltaje nominal de operación (VDD);

una compuerta del segundo transistor NMOS (128) está acoplada a una señal de validación de salida de datos (112);

un primer diodo parásito (132) está formado entre la fuente y el drenaje del primer transistor PMOS (126); y

un segundo diodo parásito (134) está formado entre la fuente y el drenaje del segundo transistor PMOS (124), en el que cuando la señal de control (108) está en una lógica 1, el circuito de control se controla de tal manera que el flujo de corriente a través del segundo diodo parásito (134) puede accionar la pastilla de señal del circuito integrado (140) hasta sustancialmente el voltaje de operación nominal (VDD) mientras el segundo diodo parásito (134) evita sustancialmente el flujo de corriente desde la pastilla de señal de circui40 to integrado (140) hasta el voltaje de operación nominal (VDD) cuando la pastilla de señal de circuito integrado (140) está a un voltaje superior al voltaje de operación nominal (VDD).

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2008/063509.

Solicitante: MICROCHIP TECHNOLOGY INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 2355 WEST CHANDLER BOULEVARD CHANDLER, AZ 85224-6199 ESTADOS UNIDOS DE AMERICA.

Inventor/es: COOPER, RUSSELL, E., WANG,GUOLI, THOMSEN,JOSEPH A.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K19/003 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › Modificaciones para aumentar la fiabilidad.

PDF original: ES-2626629_T3.pdf

Patentes similares o relacionadas:

Interruptor de alimentación de bloque con protección integrada contra descargas electrostáticas (esd) y polarización adaptativa del cuerpo, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento de fabricación de un circuito, que comprende: formar un interruptor de alimentación que comprenda múltiples etapas conectadas […]

Dispositivo de memoria que corrige el efecto de colisiones de partículas de alta energía, del 28 de Agosto de 2019, de THALES: Dispositivo de memoria que corrige automáticamente el efecto de colisiones de partículas de alta energía, que comprende una célula (CM) de memoria; […]

Circuito eléctrico con protección contra radiación y procedimiento operativo, del 15 de Mayo de 2019, de IHP GmbH-Innovations for High Performance Microelectronics / Leibniz-Institut für innovative Mikroelektronik (100.0%): Circuito eléctrico con - dos memorias maestra-esclava redundantes (LMa, LSa, LMb, LSb) que presentan en cada caso un elemento de memoria maestro (LMa, LMB) […]

Aparato de radio de aeronave y procedimiento con redundancia reconfigurable de manera dinámica, del 21 de Junio de 2017, de ROHDE & SCHWARZ GMBH & CO. KG: Aparato de radio de aeronave con un elemento de circuito reconfigurable de manera dinámica con una capacidad predeterminada, presentando el aparato […]

Procedimiento y configuración de circuitos para conmutar un interruptor semiconductor, del 14 de Diciembre de 2016, de CONTI TEMIC MICROELECTRONIC GMBH: Procedimiento para conmutar un interruptor semiconductor (HS1) desde un primer estado de conexión estático hasta un segundo estado de conexión […]

Circuito eléctrico para la transmisión de señales entre dos maestros y uno o varios esclavos, del 22 de Enero de 2016, de ROBERT BOSCH GMBH: Circuito eléctrico que comprende dos maestros y uno o varios esclavos , diseñado para la transmisión de señales entre dos maestros (11, […]

Circuito eléctrico para la transmisión de señales entre dos maestros y uno o varios esclavos, del 22 de Enero de 2016, de ROBERT BOSCH GMBH: Circuito eléctrico que comprende dos maestros y uno o varios esclavos , diseñado para la transmisión de señales entre dos maestros (11, […]

Circuito integrado con un gran número de circuitos elementales idénticos alimentados en paralelo, del 8 de Agosto de 2012, de E2V SEMICONDUCTORS: Circuito integrado que comprende una sucesión de N circuitos elementales idénticos (CE1, CE2, ... CEN),yuxtapuestos en el orden de su fila j que varían desde 1 […]

PROCEDIMIENTO PARA LA MEJORA DE LA FIABILIDAD DE CIRCUITOS INTEGRADOS DIGITALES EN CONDICIONES DE BAJA RELACIÓN SEÑAL A RUIDO, del 11 de Enero de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Procedimiento para la mejora de la fiabilidad de circuitos integrados digitales en condiciones de baja relación señal a ruido.

Procedimiento para la mejora de la fiabilidad […]

PROCEDIMIENTO PARA LA MEJORA DE LA FIABILIDAD DE CIRCUITOS INTEGRADOS DIGITALES EN CONDICIONES DE BAJA RELACIÓN SEÑAL A RUIDO, del 11 de Enero de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Procedimiento para la mejora de la fiabilidad de circuitos integrados digitales en condiciones de baja relación señal a ruido.

Procedimiento para la mejora de la fiabilidad […]