Métodos para la gestión y el almacenamiento de datos corregidos.

Un método para gestionar datos en un sistema de memoria con una matriz de memoria no volátil queincluye múltiples bloques,

un bloque representando la unidad de borrado mínima, comprendiendo:

recibir una orden de lectura a partir de un host, identificar una pluralidad de sectores en un primer bloquepara leer dentro de un límite temporal predeterminado menor al tiempo requerido para copiar un bloque dela matriz de memoria;

leer la pluralidad de sectores a partir de un primer bloque y determinar si los sectores de la pluralidaddeben corregirse y reemplazarse; si un sector individual debe ser corregido y reemplazado, corrigiendodespués el sector individual y escribiendo el sector corregido en un segundo bloque dentro del límitetemporal predeterminado;

mantener los sectores que no deben corregirse ni reemplazarse en el primer bloque en la forma sincorregir sin escribirlos en el segundo bloque;

enviar el sector individual y los sectores que no deben ser corregidos ni reemplazados al host; ycopiar consecuentemente el sector individual y los sectores que no deben ser corregidos ni reemplazadosa un tercer bloque.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2006/038808.

Solicitante: Intelligent Intellectual Property Holdings LLC.

Inventor/es: CONLEY, KEVIN, M., GONZALEZ, CARLOS J., GOROBETS,SERGEY ANATOLIEVICH, ELHAMIAS,REUVEN.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F11/10 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › añadiendo cifras binarias o símbolos especiales a los datos expresados según un código, p. ej. control de paridad, exclusión de los 9 o de los 11.

- G11C29/00 G […] › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › Verificación del funcionamiento correcto de memorias; Ensayo de memorias durante su funcionamiento fuera de línea (offline")o en espera ("standby").

PDF original: ES-2442490_T3.pdf

Fragmento de la descripción:

Métodos para la gestión y el almacenamiento de datos corregidos ANTECEDENTES

Esta invención hace referencia en general al funcionamiento de sistemas de memoria flash no volátil, y, más específicamente, a técnicas de renovación y corrección de datos almacenados en ella, particularmente en sistemas de memoria con bloques de celda de memoria muy grandes.

Existen muchos productos de memoria no volátil con éxito comercial utilizados hoy en día, particularmente en forma de pequeñas tarjetas de factor de forma, que emplean un conjunto de celdas flash EEPROM (en inglés Electrically Erasable Programmable Read Only Memor y , memoria de solo lectura programable y borrable eléctricamente) formadas sobre uno o más chips de circuito integrado. Un controlador de memoria, normalmente pero no siempre en un chip del circuito integrado separado, conecta con un host al que se conecta la tarjeta de manera extraíble y controla el funcionamiento de la matriz de memoria dentro de la tarjeta. Dicho controlador típicamente incluye un microprocesador, alguna memoria de solo lectura (ROM) no volátil, una memoria de acceso aleatorio (RAM) y uno o más circuitos especiales como uno que calcula un código corrector de errores (ECC) a partir de datos mientras pasan a través del controlador durante la programación y lectura de datos. Alguna de las tarjetas comercialmente disponibles son las tarjetas CompactFlash™ (CF) , las tarjetas Multimedia (MMC) , tarjetas Secure Digital (SD) , tarjetas Smart Media, personnel tags (P-Tag) y tarjetas Memor y Stick. Los Hosts incluyen ordenadores personales, ordenadores portátiles, agendas digitales personales (PDAs) , varios dispositivos de comunicación de datos, cámaras digitales, teléfonos móviles, reproductores de audio portátiles, sistemas de sonido para automóviles, y tipos de equipos similares. Además de la implementación de la tarjeta de memoria, este tipo de memoria puede estar integrada de manera alternativa en varios tipos de sistema host.

Dos arquitecturas generales de matriz de celdas de memoria han encontrado una aplicación comercial: NOR y NAND. En una puerta NOR típica, las celdas de memoria están conectadas entre una fuente de línea de bits adyacente y difusiones del drenador que se extienden en una dirección de columna con las puertas de control conectadas a líneas de palabra que se extienden a lo largo de filas de celdas. Una celda de memoria incluye al menos un elemento de almacenamiento situado sobre al menos una parte de la región del canal de celda entre la fuente y el drenaje. Un nivel programado de carga en los elementos de almacenamiento controla así una característica de funcionamiento de las celdas, que pueden ser leídas entonces al aplicar tensiones apropiadas sobre las celdas de memoria dirigidas. Los ejemplos de dichas celdas, sus usos en sistemas de memoria y métodos de fabricarlas se presentan en las patentes estadounidenses números 5.070.032, 5.095.344, 5.313.421, 5.315.541, 5.343.063, 5.661.053 y 6.222.762.

La puerta NAND utiliza cadenas de series de más de dos celdas de memoria, por ejemplo de 16 o 32, conectadas junto con uno o más transistores seleccionados entre líneas de bits individuales y una referencia potencial para formar columnas de celdas. Las líneas de palabra se extienden por las celdas dentro de un gran número de estas columnas. Una celda individual dentro de una columna se lee y verifica durante la programación provocando que las celdas restantes en la cadena sean difíciles de encender para que la corriente que fluye a través de una cadena dependa del nivel de carga almacenado en la celda dirigida. Los ejemplos de arquitectura de puertas NAND y su funcionamiento como parte del sistema de memoria se encuentran en las patentes estadounidenses números 5.570.315, 5.774.397, 6.046.935 y 6.522.580.

Los elementos de almacenamiento de carga de las actuales memorias flash EEPROM, según se debate en las patentes anteriormente mencionadas, son más comúnmente puertas flotantes de conductividad eléctrica, típicamente formadas a partir de un material conductor dopado de polisilicio. Un tipo de celda de memoria alternativa útil en los sistemas flash EEPROM utiliza un material dieléctrico no conductivo en lugar de la puerta flotante conductiva para almacenar carga de manera no volátil. Un material dieléctrico de triple capa formado con óxido de silicio, nitruro de silicio y óxido de silicio (ONO) , se sitúa entre una puerta de control conductiva y una superficie de un sustrato semi-conductivo por encima del canal de celda de memoria. La celda se programa inyectando electrones desde el canal de celda hacia el nitruro, donde se retienen y almacenan en una región limitada, y se borran inyectando electrones calientes en el nitruro. Varias estructuras y conjuntos de celdas específicos empleando elementos dieléctricos de almacenamiento se describen en la solicitud de patente estadounidense publicada núm. 2003/0109093.

Como en la mayoría de las aplicaciones de circuito integrado, la presión para reducir el área del sustrato de silicona requerida para implementar alguna función del circuito integrado también existe con las matrices de celdas de memoria flash EEPROM. Constantemente se desea aumentar la cantidad de datos digitales que pueden almacenarse en un área dada de un sustrato de silicona, para aumentar la capacidad de almacenamiento de una tarjeta de memoria dada y otros tipos de paquetes, o para aumentar la capacidad y disminuir el tamaño. Una manera de aumentar la densidad de almacenamiento de datos consiste en almacenar más de un bit de datos por celda de

memoria y/o por unidad o elemento de almacenamiento. Esto se consigue dividiendo una ventana del intervalo de niveles de voltaje de la carga de un elemento de almacenamiento en más de dos estados. El uso de cuatro de estos estados permite a cada celda almacenar dos bits de datos, ocho estados almacenan tres bits de datos por elemento de almacenamiento, y así sucesivamente. Las estructuras de múltiples estados flash EEPROM utilizando puertas flotantes y su funcionamiento se describen en las patentes estadounidenses con números 5.043.940 y 5.172.338, y para las estructuras utilizando puertas flotantes dieléctricas en la solicitud de patente estadounidense núm. 10/280.352 mencionada con anterioridad. Las partes seleccionadas de un conjunto de celdas de memoria multiestado también pueden funcionar en dos estados (binario) por varias raciones, de la manera descrita en las patentes estadounidenses con números 5.930.167 y 6.456.528.

Las celdas de memoria de un típico conjunto flash EEPROM se dividen en bloques discretos de celdas que se borran a la vez. Es decir, el bloque es la unidad de borrado, un número mínimo de celdas que pueden borrarse de manera simultánea. Cada bloque almacena típicamente una o más páginas de datos, la página siendo la unidad mínima de programación y lectura, pese a que más de una página se puede programar o leer en paralelo en diferentes sub-conjuntos o planos. Cada página almacena típicamente uno o más sectores de datos, el tamaño del sector estando definido por el sistema host. Un sector de ejemplo incluye 512 bytes de datos de usuario, siguiendo un estándar establecido con unidades de disco magnético, además de algunos conjuntos de bytes de información de cabecera sobre los datos de usuario y/o el bloque en el que se almacenan. Dichas memorias están típicamente configuradas con 16, 32 o más páginas dentro de cada bloque, y cada página almacena uno o solo unos pocos sectores de datos.

Con tal de aumentar el grado de paralelismo durante la programación de los datos de usuario en la matriz de memoria y la lectura de los datos de usuario a partir de ella, la matriz se divide típicamente en subconjuntos, comúnmente conocidos como planos, que contienen sus propios registros de datos y otros circuitos para permitir el funcionamiento paralelo con tal de que los sectores de datos puedan programarse o leerse desde cada uno de varios o todos los planos de manera simultánea. Un conjunto de un único circuito integrado puede estar físicamente dividido en planos, o cada plano puede formarse a partir de uno o más chips del circuito integrado. Los ejemplos de tal implementación de memoria se describen en las patentes estadounidenses con números 5.798.968 y 5.890.192.

Con tal de administrar de manera más eficiente la memoria, pueden enlazarse de manera lógica los bloques físicos para formar bloques virtuales o "metabloques". Es decir, cada metabloque está definido para incluir un bloque de cada plano. El uso del metabloque se describe en la publicación de la solicitud de patente internacional núm. WO 02/058074. El metabloque se identifica mediante una dirección del bloque lógico del host como destino para... [Seguir leyendo]

Reivindicaciones:

1. Un método para gestionar datos en un sistema de memoria con una matriz de memoria no volátil que incluye múltiples bloques, un bloque representando la unidad de borrado mínima, comprendiendo: recibir una orden de lectura a partir de un host, identificar una pluralidad de sectores en un primer bloque para leer dentro de un límite temporal predeterminado menor al tiempo requerido para copiar un bloque de la matriz de memoria; leer la pluralidad de sectores a partir de un primer bloque y determinar si los sectores de la pluralidad deben corregirse y reemplazarse; si un sector individual debe ser corregido y reemplazado, corrigiendo después el sector individual y escribiendo el sector corregido en un segundo bloque dentro del límite temporal predeterminado; mantener los sectores que no deben corregirse ni reemplazarse en el primer bloque en la forma sin corregir sin escribirlos en el segundo bloque; enviar el sector individual y los sectores que no deben ser corregidos ni reemplazados al host; y copiar consecuentemente el sector individual y los sectores que no deben ser corregidos ni reemplazados a un tercer bloque.

2. El método de la Reivindicación 1, comprendiendo también corregir otros sectores desde el primer bloque y escribir los otros sectores corregidos en el segundo bloque con el sector individual dentro del límite temporal.

3. El método de la Reivindicación 1 comprendiendo también la escritura adicional de sectores en el segundo bloque, los sectores adicionales reemplazando los sectores de datos en uno o más bloques de la matriz de memoria distintos al primer bloque; y compactar consecuentemente los datos en el segundo bloque copiando sectores del segundo bloque que

no están obsoletos en un cuarto bloque, sin copiar en el cuarto bloque los sectores del segundo bloque que no están obsoletos.

4. El método de la Reivindicación 3, en el que la compactación ocurre en respuesta al umbral de sectores almacenados en el segundo bloque.

5. El método de la Reivindicación 4, en el que el umbral de sectores se determina mediante la cantidad máxima de datos que pueden copiarse dentro de un límite temporal para una orden de lectura.

6. El método de la Reivindicación 1, comprendiendo consecuentemente la lectura únicamente de las copias de

sectores corregidos que tienen tanto una copia corregida como una copia no corregida en la matriz de memoria no volátil.

7. El método de la Reivindicación 6, en el que la copia corregida de un sector se identifica a partir de una lista de sectores corregidos y reemplazados.

8. Un método para gestionar datos en un sistema de memoria con una matriz de memoria no volátil que incluye múltiples bloques, un bloque representando la unidad de borrado mínima, comprendiendo:

identificar sectores de datos a corregir y reemplazar, y escribir sectores de reemplazo corregidos únicamente para los sectores identificados en un bloque dedicado, mientras los sectores sin corregir

permanecen en los bloques originales con los sectores identificados; recibir sectores actualizados desde un host, con los sectores actualizados reemplazando sectores almacenados en la matriz de memoria no volátil; almacenar los sectores actualizados en la memoria no volátil; recibir consecuentemente una orden de lectura desde un host, identificando un sector con una dirección 50 lógica para la que existe un primer sector corregido de reemplazo en el bloque dedicado y para la que un primer sector actualizado existe en la memoria no volátil; y enviar al host el sector más recientemente escrito del primer sector corregido de reemplazo y el primer sector actualizado.

9. El método de la Reivindicación 8, en el que los sectores actualizados se almacenan en bloques actualizados y el primer sector actualizado se almacena en un primer bloque actualizado, un bloque actualizado almacenando datos actualizados dentro de un rango de dirección lógica que corresponde a uno más bloques originales.

10. El método de la Reivindicación 9 en el que el primer bloque de actualización almacena sectores en un orden lógico no secuencial.

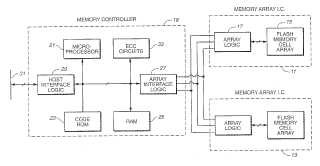

Dibujos MATRIZ DE MEMORIA I.C.

CONTROLADOR DE MEMORIA

MATRIZ MATRIZ DE CELDAS MICRO-CIRCUITOS ECC LÓGICA DE MEMORIA

PROCESADOR

INTERFAZ INTERFAZ LÓGICA DEL LÓGICA DE LA HOST MATRIZ

MATRIZ DE MEMORIA I.C.

MATRIZ

CÓDIGO

MATRIZ DE CELDAS

ROM LÓGICA DE MEMORIA

29

SISTEMA DE DATOS RAM

CÓDIGO ROM

MICRO-

PROCESADOR

INTERFAZ

LÓGICA DE LA

MEMORIA

OTROS CIRCUITOS

Y SUBSISTEMAS

BLOQUE

BLOQUE

BLOQUE PÁGINA

BLOQUE BLOQUE PÁGINA

BLOQUE PÁGINA

BLOQUE PÁGINA

BLOQUE

PARÁMETROS DE

SECTOR DE DATOS DE USUARIO HOST ECC DE DATOS ECC DE O.H

BLOQUE/DATOS

DATOS DE CABECERA (“O.H.)

PLANO 2

PLANO 1

PLANO 3

PLANO 0

BLOQUE 0

BLOQUE 1

31

PLANO 0 PLANO 1 PLANO 2 PLANO 3

BLOQUE 0

BLOQUE 1

BLOQUE 1 BLOQUE 1 BLOQUE DE DATOS

BLOQUE 2

BLOQUE 2

LÓGICOS

BLOQUE 3

BLOQUE 4

NÚMERO DE CELDAS

ESTADO

ESTADO

ESTADO ESTADO

DRIVERS DEL

BLOQUE

SELECCIONA

DIRECCIONES DO Y LÍNEA

DE PALABRA

(WL)

DIRECCIÓN

DATOS DRIVERS DE LA LÍNEA DE BITS (BL) Y CIRCUITOS DE LECTURA

CONTROLAR LOS SISTEMAS DE MEMORIA PARA UN EVENTO QUE DESENCADENA LA DEPURACIÓN

DETERMINAR LAS LOCALIZACIONES CANDIDATAS A LA DEPURACIÓN

DETERMINAR SI SE DEPURA EN ESTE MOMENTO

DETERMINAR LOS CANDIDATOS A DEPURAR

REALIZAR UNA LECTURA DE DEPURACIÓN

DETERMINAR LA INTEGRIDAD DE LOS DATOS LEÍDOS

DETERMINAR SI ES NECESARIA UNA ACCIÓN CORRECTIVA

DETERMINAR SI SE POSPONE LA FINALIZACIÓN DEL DEPURADO

CORREGIR LOS DATOS

REALIZAR LA ACCIÓN CORRECTIVA

INICIAR EN RESPUESTA AL EVENTO DESENCADENANTE DE LA DEPURACIÓN

DETERMINAR LAS UNIDADES DE CELDA DE MEMORIA QUE SON CANDIDATAS PARA DEPURAR

POSPONER DEPURACIÓN?

Sí

ALMACENAR DIRECCIONES DE LAS UNIDADES CANDIDATAS

MÁS UNIDADES PARA DEPURAR?

Sí

FIN

INICIAR EN RESPUESTA AL EVENTO DESENCADENANTE DE LA DEPURACIÓN POSPUESTA

LEER DATOS Y PARÁMETROS ALMACENADOS PARA SU CORRECCIÓN Y/O REESCRITURA

CORREGIR LOS DATOS

REESCRIBIRLOS DATOS

HAY MÁS ACTIVIDAD DE DEPURACIÓN POSPUESTA?

Sí INCREMENTAR A LA SIGUIENTE UNIDAD DE INFORMACIÓN DATOS

MAPEAR ALGUNA UNIDAD DE DATOS?

Sí

MAPEAR UNIDADES

FIN

INCREMENTAR EL ESTADO DE CONDICIONES DE DEPURACIÓN

Sí

MÁS CONDICIONES DE LECTURA DE DEPURACIÓN?

ALMACENAR DIRECCIÓN, PARÁMETROS Y CONDICIONES PARA LA ACCIÓN POSPUESTA

INCREMENTAR A LA SIGUIENTE UNIDAD DE INFORMACIÓN DE DATOS

IDENTIFICAR LAS UNIDADES CANDIDATAS A DEPURAR

ESTABLECER CONDICIONES DE LECTURA DE DEPURACIÓN APROPIADAS

REALIZAR LECTURA DE DEPURACIÓN SOBRE LA UNIDAD DE DATOS IDENTIFICADA

ALGÚN ERROR DE DATOS?

Sí

LOS ERRORES SON CORREGIBLES?

Sí

ES DESEABLE UNA ACCIÓN CORREGIBLE?

Sí

Sí

POSPONER LA CORRECCIÓN DE DATOS?

CORREGIR LOS DATOS

Sí

POSPONER LA ACCIÓN CORRECTIVA?

REESCRIBIR LOS DATOS

Sí OTRAS UNIDADES DE DATOS A DEPURAR?

ESTABLECER CONDICIONES APROPIADAS DE REINTENTO DE LECTURA

REALIZAR REINTENTO DE LECTURA

ALGÚN ERROR DE DATOS?

Sí

LOS ERRORES SON Sí CORREGIBLES?

MÁS CONDICIONES DE REINTENTO DE LECTURA?

Sí

INCREMENTAR EL ESTADO DE CONDICIONES DE REINTENTO

FALLO

LECTURA HOST CON REEMPLAZAMIENTO PARCIAL

LECTURA HOST

LECTURA DEL SECTOR REQUERIDA DESDE EL BLOQUE EN LA MATRIZ

ERROR EN SECTOR?

Sí

CORREGIR SECTOR

ENVIAR SECTOR CORREGIDO AL HOST

ERRORES> UMBRAL?

Sí

ESCRIBIR SECTOR CORREGIDO EN EL BLOQUE DEDICADO

SECTORES ADICIONALES

FIN ?

Sí

LECTURA CON REEMPLAZAMIENTO PARCIAL

BLQUE ORIGINAL BLOQUE DE CORRECCIÓN

SECTORES SECTORES SIN CORREGIDOS (X=2) ’ CORREGIR X, X+3 CORRECCIÓN Y (X+9) ’ HASTA X+8, X+10 Y

SECTORES

X+11

CORREGIDOS (X+1) ’ (X+2) ’ Y (X+9)

CONSOLIDACIÓN DE DATOS CORREGIDOS Y SIN CORREGIR

BLOQUE ORIGINAL BLOQUE DE CORRECCIÓN BLOQUE CONSOLIDADO

COMPACTACIÓN DEL BLOQUE DE CORRECCIÓN

BLOQUE ORIGINAL BLOQUE DE CORRECCIÓN BLOQUE CONSOLIDADO OBSOLETO OBSOLETO

OBSOLETO OBSOLETO OBSOLETO OBSOLETO

BLOQUE DE CORRECCIÓN COMPACTADO

ESPACIO LIBRE

BLOQUES DE CORRECCIÓN Y ACTUALIZACIÓN

BLOQUE DE ACTUALIZACIÓN DESORDENADA

BLOQUE ORIGINAL BLOQUE DE CORRECCIÓN

Patentes similares o relacionadas:

Método de segmentación de un bloque de transporte en múltiples bloques de código cuando se añade una CRC a cada bloque de código, del 2 de Octubre de 2019, de LG ELECTRONICS INC.: Un método para transmitir datos en un sistema de acceso inalámbrico, el método que comprende: obtener (S601) un número C de bloques de código en base […]

Dispositivo de memoria de semiconductor no volátil, del 28 de Agosto de 2019, de Winbond Electronics Corp: Un dispositivo de almacenamiento de semiconductor no volátil , que comprende: una matriz de memoria ; una pluralidad de circuitos de retención de […]

Seguimiento de cambios usando redundancia en tiempo lógico, del 4 de Junio de 2019, de Microsoft Technology Licensing, LLC: Un método para mantener el seguimiento de cambios entre porciones unitarias de un sistema de almacenaje, comprendiendo el método: […]

Métodos y sistemas para detectar y corregir errores en una memoria no volátil, del 30 de Enero de 2019, de Winbond Electronics Corp: Un sistema de memoria, que comprende: una matriz de memoria no volátil resistiva configurada para almacenar datos, bits de anticipación y bits de […]

Sistemas y métodos para asegurar datos en movimiento, del 9 de Mayo de 2018, de Security First Corp: Un método para leer y escribir un conjunto de datos, que comprende: dividir el conjunto de datos en una o más comparticiones de datos 5 usando un algoritmo […]

Método para procesar datos en Ethernet, circuito integrado de capa física y dispositivo de Ethernet, del 2 de Mayo de 2018, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesamiento de datos de Ethernet, aplicable al procesamiento de datos en un extremo de transmisión, que comprende: * la realización de una codificación […]

Dispositivo de inspección de traducción de dirección, dispositivo de procesamiento central y procedimiento de inspección de traducción de dirección, del 17 de Enero de 2018, de MITSUBISHI HEAVY INDUSTRIES, LTD.: Un dispositivo de comprobación de traducción de dirección que comprende: una unidad de gestión de memoria de traducción entre una dirección virtual y una dirección […]

Procedimiento, dispositivo y sistema de almacenamiento distribuido, del 11 de Octubre de 2017, de HUAWEI TECHNOLOGIES CO., LTD.: Un procedimiento de almacenamiento distribuido, que comprende: dividir un archivo de datos para generar K segmentos de datos, dividir cada segmento de […]