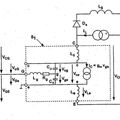

Circuito de conmutación de cascode.

Un circuito de conmutación de cascode que comprende un dispositivo semiconductor normalmente encendido (105),

un dispositivo semiconductor normalmente apagado (107) y un controlador de compuerta (201), en donde:

dicho dispositivo semiconductor normalmente encendido (105) y dicho dispositivo semiconductor normalmente apagado (107) tienen cada uno un terminal de compuerta, un terminal de drenaje y un terminal de fuente;

dicho controlador de compuerta (201) tiene una primera salida (203) y una segunda salida (205);

dicha primera salida (203) de dicho controlador de compuerta (201) está acoplada a dicho terminal de compuerta de dicho dispositivo semiconductor normalmente encendido (105);

dicha segunda salida (205) de dicho controlador de compuerta (201) está acoplada a dicho terminal de compuerta de dicho dispositivo semiconductor normalmente apagado (107);

dicho terminal de drenaje de dicho dispositivo semiconductor normalmente apagado (107) está acoplado a dicho terminal de fuente de dicho dispositivo semiconductor normalmente encendido (105) de tal manera que se forma una ruta de corriente a través de dicho dispositivo semiconductor normalmente encendido (105) y dicho dispositivo semiconductor normalmente apagado (107);

dicho controlador de compuerta (201) está configurado de tal manera que un proceso de encendido de dicho circuito de conmutación de cascode se controla controlando dicho dispositivo semiconductor normalmente apagado (107);

un proceso de apagado de dicho circuito de conmutación de cascode está configurado para ser controlado controlando dicho dispositivo semiconductor normalmente encendido (105); y

durante dicho proceso de apagado de dicho circuito de conmutación de cascode, dicho controlador de compuerta (201) está configurado para provocar una transición de dicho circuito de conmutación de cascode desde el estado ENCENDIDO al estado de APAGADO cambiando dicha primera salida (203) de dicho controlador de compuerta (201) de un primer nivel de voltaje a un segundo nivel de voltaje para apagar dicho dispositivo semiconductor normalmente encendido (105),

luego, después de un primer tiempo de retardo predeterminado, cambiando dicha segunda salida de dicho controlador de compuerta (201) de un tercer nivel de voltaje a un cuarto nivel de voltaje para apagar dicho dispositivo semiconductor normalmente apagado (107), y

después de un segundo tiempo de retardo predeterminado, cambiando dicha primera salida (203) de dicho controlador de compuerta (201) de dicho segundo nivel de voltaje a dicho primer nivel de voltaje.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2015/029187.

Solicitante: United Silicon Carbide Inc.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 7 Deer Park Drive, Suite E. Monmouth Junction, NJ 08852 ESTADOS UNIDOS DE AMERICA.

Inventor/es: LI,XUEQING, BHALLA,ANUP.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K17/10 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 17/00 Conmutación o apertura de puerta electrónica, es decir, por otros medios distintos al cierre y apertura de contactos (amplificadores controlados H03F 3/72; disposiciones de conmutación para los sistemas de centrales que utilizan dispositivos estáticos H04Q 3/52). › Modificaciones para aumentar la tensión conmutada máxima admisible.

- H03K17/16 H03K 17/00 […] › Modificaciones para eliminar las tensiones o corrientes parásitas.

- H03K17/567 H03K 17/00 […] › Circuitos caracterizados por la utilización de al menos dos tipos de dispositivos semiconductores, p. ej. BIMOS, dispositivos compuestos tales como IGBT.

- H03K17/687 H03K 17/00 […] › siendo los dispositivos transistores de efecto de campo.

PDF original: ES-2746278_T3.pdf

Patentes similares o relacionadas:

Célula de conmutación y circuito de compensación para la misma, del 19 de Junio de 2019, de TM4 Inc: Una célula de conmutación configurada para limitar la sobretensión de conmutación y para limitar la corriente de recuperación, que comprende: un conmutador […]

Procedimiento para controlar dos IGBT de conducción inversa, conectados eléctricamente en serie, de un semipuente, del 17 de Mayo de 2019, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para controlar dos IGBT de conducción inversa (T1, T2) conectados eléctricamente en serie, de un semipuente , en el cual se encuentra […]

Dispositivo y circuito de control de un componente electrónico de potencia, procedimiento de mando y distribuidor asociados, del 12 de Abril de 2017, de ALSTOM Transport Technologies: Circuito de control de la apertura y del cierre de un componente electrónico de potencia , teniendo el componente electrónico de potencia […]

Procedimiento y configuración de circuitos para conmutar un interruptor semiconductor, del 14 de Diciembre de 2016, de CONTI TEMIC MICROELECTRONIC GMBH: Procedimiento para conmutar un interruptor semiconductor (HS1) desde un primer estado de conexión estático hasta un segundo estado de conexión […]

Circuito y procedimiento de accionamiento para MOSFET, del 15 de Junio de 2016, de NORTH-WEST UNIVERSITY: Un procedimiento de utilización de un circuito para accionar un dispositivo semiconductor de puerta aislada que comprende como un primer […]

Circuito excitador para activar un interruptor de semiconductor de potencia, del 3 de Diciembre de 2014, de SEMIKRON ELEKTRONIK GMBH & CO. KG: Circuito excitador con una primera salida (12a) y una segunda salida (12b) para activar un interruptor de semiconductor de potencia conectable con una señal de una primera […]

CIRCUITO INTEGRADO PARA LA GENERACION DE UNA SEÑAL DE ACTIVACION PARA UN TRANSISTOR BIPOLAR CON PUERTA AISLADA (IGBT)., del 16 de Junio de 2006, de SIEMENS AG: Circuito integrado para la generación de una señal de activación para un IGBT con una conexión de entrada para una señal de control generada por medio de un microcontrolador […]

PROCEDIMIENTO Y DISPOSITIVO PARA REGULAR, EN FUNCION DEL ESTADO, EL COMPORTAMIENTO TRANSITORIO DE INTERRUPTORES DE SEMICONDUCTOR DE POTENCIA, del 1 de Agosto de 2008, de CT-CONCEPT TECHNOLOGIE AG: Procedimiento para regular un proceso transitorio de conmutación de al menos un interruptor de semiconductor de potencia (S1-S4) que comprende al menos un terminal […]

PROCEDIMIENTO Y DISPOSITIVO PARA REGULAR, EN FUNCION DEL ESTADO, EL COMPORTAMIENTO TRANSITORIO DE INTERRUPTORES DE SEMICONDUCTOR DE POTENCIA, del 1 de Agosto de 2008, de CT-CONCEPT TECHNOLOGIE AG: Procedimiento para regular un proceso transitorio de conmutación de al menos un interruptor de semiconductor de potencia (S1-S4) que comprende al menos un terminal […]