Circuito excitador para activar un interruptor de semiconductor de potencia.

Circuito excitador (4) con una primera salida (12a) y una segunda salida (12b) para activar un interruptor de semiconductor de potencia (2) conectable con una señal de una primera tensión (UVP) con respecto a un potencial de referencia (GND) y desconectable con una señal de una segunda tensión (UVN) con respecto al potencial de referencia (GND),

y con una primera entrada (18a) y una segunda entrada (18b) para activar por una señal (UIN) un circuito lógico (8) alimentado con una tercera tensión (UL) y el potencial de referencia (GND), con un trayecto de conexión (10a) alimentado entre la primera tensión (UVP) y el potencial de referencia (GND) y dotado de la primera entrada (18a) y la primera salida (12a), y con un trayecto de desconexión (10b) alimentado entre la tercera tensión (UL) y la segunda tensión (UVN) y dotado de la segunda entrada (18b) y la segunda salida (12b), conteniendo el trayecto de conexión (10a) y el trayecto de desconexión (10b), en cada caso, un convertidor de nivel (20a,b) que presenta la respectiva entrada (18a,b), un amplificador de corriente (22a,b) activado por el convertidor de nivel (20a,b) y una etapa final (24a,b) activada por el amplificador de corriente (22a,b) y dotada de la respectiva salida (12a,b).

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E08012363.

Solicitante: SEMIKRON ELEKTRONIK GMBH & CO. KG.

Nacionalidad solicitante: Alemania.

Dirección: SIGMUNDSTRASSE 200 90431 NURNBERG ALEMANIA.

Inventor/es: Bode,Rüdiger, Mühlhöfer,Alexander, Hofmair,Markus, KÖNIGSMANN,GUNTHER.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K17/06 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 17/00 Conmutación o apertura de puerta electrónica, es decir, por otros medios distintos al cierre y apertura de contactos (amplificadores controlados H03F 3/72; disposiciones de conmutación para los sistemas de centrales que utilizan dispositivos estáticos H04Q 3/52). › Modificaciones para asegurar un estado completamente conductor.

- H03K17/16 H03K 17/00 […] › Modificaciones para eliminar las tensiones o corrientes parásitas.

- H03K17/567 H03K 17/00 […] › Circuitos caracterizados por la utilización de al menos dos tipos de dispositivos semiconductores, p. ej. BIMOS, dispositivos compuestos tales como IGBT.

- H03K17/687 H03K 17/00 […] › siendo los dispositivos transistores de efecto de campo.

- H03K19/018 H03K […] › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › utilizando únicamente transistores bipolares.

PDF original: ES-2531452_T3.pdf

Fragmento de la descripción:

Circuito excitador para activar un interruptor de semiconductor de potencia.

La invención concierne a un circuito excitador que sirve para activar un interruptor de semiconductor de potencia.

Los interruptores de semiconductor de potencia, por ejemplo un IGBT (Insulated Gate Bipolar Transistor -Transistor Bipolar de Puerta Aislada) , tienen que obtener una señal de conexión para realizar un proceso de conexión. Ésta es suministrada en general por un circuito lógico, por ejemplo un PLD (Programmable Logic Device -Dispositivo Lógico Programable) . Un IGBT es, por ejemplo, conectado con una tensión de +15 V y desconectado con una tensión de, por ejemplo, -15 V. La corriente punta para conectar o cargar la puerta del IGBT puede ascender a varios amperios. La lógica programable trabaja aquí, por ejemplo, en un intervalo comprendido entre masa y 3, 3 V y suministra señales en el rango de intensidades de corriente de pocos mA. Por tanto, el circuito lógico en sí no proporciona con su señal de control ni una corriente suficiente ni una tensión suficiente para poder conectar realmente el interruptor de semiconductor de potencia. Por consiguiente, se tienen que amplificar las corrientes y tensiones suministradas por la lógica programable para poder conectar realmente el interruptor de semiconductor de potencia. Para amplificar la señal lógica se necesita una etapa final o circuito excitador correspondiente.

Es conocido el emplear como etapa final o en un circuito excitador un módulo de activación completamente integrado, tal como, por ejemplo, del tipo LM5107 de la firma National Semiconductor o un circuito integrado comparable.

En el documento US 6, 208, 185 B1 se muestra otro circuito.

Sin embargo, una solución de esta clase es cara y, además, hay que proporcionar usualmente una alimentación de corriente propia de, por ejemplo, 10 V para la alimentación del módulo integrado.

El problema de la presente invención consiste en indicar un circuito excitador o etapa final mejorado para su intercalación entre una lógica programable y un interruptor de semiconductor de potencia.

La invención parte del conocimiento de que un interruptor de semiconductor de potencia que debe ser activado por el circuito excitador según la invención necesita una señal de una primera tensión con respecto a un potencial de referencia -en general, masa -para poder ser conectado y necesita una señal de una segunda tensión con respecto a este potencial de referencia para poder ser desconectado. Además, está disponible para la activación del interruptor de semiconductor de potencia un circuito lógico que es alimentado entre una tercera tensión y el potencial de referencia y que, en consecuencia, puede suministrar señales de conexión con tensiones comprendidas entre el potencial de referencia y la tercera tensión.

La invención se resuelve por medio de un circuito excitador con una primera salida y una segunda salida. La primera salida sirve para activar el interruptor de semiconductor de potencia con una señal de la primera tensión y la segunda salida sirve para activar el interruptor de semiconductor de potencia con una señal de la segunda tensión, en cada caso con respecto al potencial de referencia. Además, el circuito excitador presenta una primera entrada y una segunda entrada que pueden ser activadas por el circuito lógico. Una activación de la primera entrada produce una señal de conexión en la primera salida y una activación de la segunda entrada produce una señal de conexión en la segunda salida. El circuito excitador contiene un trayecto de conexión que presenta la primera entrada y la primera salida. El trayecto de conexión es alimentado con la primera tensión y el potencial de referencia. El circuito excitador contiene también un trayecto de desconexión que presenta la segunda entrada y la segunda salida y que es alimentado por la tercera tensión y la segunda tensión. Los trayectos de conexión y de desconexión, cada uno de ellos por separado, presentan sendos convertidores de nivel que contienen a su vez la primera entrada o la segunda entrada, según que se trate del trayecto de conexión o del trayecto de desconexión. Ambos trayectos presentan un amplificador de corriente activado por el respectivo convertidor de nivel y una respectiva etapa final activada por el amplificador de corriente. La respectiva etapa final del respectivo trayecto contiene la primera salida o la segunda salida.

El circuito excitador completo presenta así la ventaja de que tiene que ser alimentado únicamente por las tensiones necesarias de todos modos para la activación del interruptor de semiconductor de potencia, concretamente las tensiones primera a tercera y el potencial de referencia. No es necesaria una alimentación de tensión adicional. El respectivo trayecto de activación, es decir, el trayecto de entrada o el trayecto de salida, puede ser activado directamente por el circuito lógico, es decir que se activa con señales en el intervalo comprendido entre el potencial de referencia y la tercera tensión y, no obstante, suministran en sus salidas una señal de conexión de la primera tensión con respecto al potencial de referencia para conectar el interruptor de semiconductor de potencia y de la segunda tensión con respecto al potencial de referencia para desconectar el interruptor de semiconductor de potencia.

El control temporal de los procesos de conexión y desconexión, es decir, la activación de las salidas primera y segunda y, por tanto, la generación correspondiente de una tensión de conexión en las salidas primera y segunda, 2

es asumido por el circuito lógico. Por tanto, se puede conseguir así un solapamiento temporal de la activación de las dos etapas finales en los trayectos de conexión y de desconexión.

El convertidor de nivel, el amplificador de corriente y la etapa final pueden estar todos ellos construidos de forma discreta por separado. Una construcción discreta, es decir, el empleo de componentes no integrados o de tan sólo una baja integración, como, por ejemplo, transistores bipolares y transistores MOSFET, en conexión mutua discreta, es sensiblemente más barato que el empleo de un módulo de activación completamente integrado antes mencionado.

El convertidor de nivel puede contener un transistor con una resistencias en serie unido mediante su entrada de control con la respectiva entrada del trayecto de conexión o de desconexión. En general, el transistor se conecta entonces mediante el colector y el emisor, a través de una respectiva resistencia óhmica, a las dos tensiones de alimentación del respectivo trayecto, la base se conecta a la respectiva entrada y entre la base y el emisor está conectada una resistencia de entrada.

El amplificador de corriente puede ser un seguidor de emisor que contenga dos transistores. Por ejemplo, en la forma de realización que se acaba de citar el terminal del colector del transistor del convertidor de nivel se pone entonces en paralelo con dos bases de dos transistores que están conectados en serie con sus colectores y emisores entre las dos tensiones de alimentación del respectivo trayecto.

La etapa final puede contener un MOSFET con resistencia en serie unido mediante su salida de potencia con la salida. Por ejemplo, para la forma de realización antes citada el terminal de fuente del MOSFET está unido entonces con la respectiva primera o segunda tensión en el respectivo trayecto y el terminal de drenaje se ha llevado hasta la salida, la puerta está unida con los emisores del seguidor de emisor unidos uno con otro, y entre la puerta y la fuente está conectada una resistencia de entrada óhmica.

La primera tensión asciende preferiblemente a +15 V, la segunda tensión va de -8 V a -15 V y la tercera tensión es de +3, 3 V; el potencial de referencia es preferiblemente masa. Estas constelaciones de tensiones son valores de tensión usuales, por ejemplo, para el funcionamiento de un IGBT por medio de un circuito lógico PLD correspondiente.

Como ya se ha mencionado, el circuito lógico puede ser un PLD.

Como ya se ha mencionado también, el circuito excitador puede ser un circuito de esta clase para activar un IGBT actuante como interruptor de semiconductor de potencia.

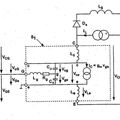

Para una descripción adicional de la invención se hace referencia a los ejemplos de realización de los dibujos. Muestran, en cada caso en un croquis de principio esquemático:

La figura 1, un circuito excitador según la invención en una vista general, La figura 2, los trayectos de entrada y de salida del circuito excitador de la figura 1 en un diagrama de bloques y La figura 3, los trayectos de entrada y de salida de la figura 2 en detalle.

La figura 1 muestra una... [Seguir leyendo]

Reivindicaciones:

1. Circuito excitador (4) con una primera salida (12a) y una segunda salida (12b) para activar un interruptor de semiconductor de potencia (2) conectable con una señal de una primera tensión (UVP) con respecto a un potencial de referencia (GND) y desconectable con una señal de una segunda tensión (UVN) con respecto al potencial de 5 referencia (GND) , y con una primera entrada (18a) y una segunda entrada (18b) para activar por una señal (UIN) un circuito lógico (8) alimentado con una tercera tensión (UL) y el potencial de referencia (GND) , con un trayecto de conexión (10a) alimentado entre la primera tensión (UVP) y el potencial de referencia (GND) y dotado de la primera entrada (18a) y la primera salida (12a) , y con un trayecto de desconexión (10b) alimentado entre la tercera tensión (UL) y la segunda tensión (UVN) y dotado de la segunda entrada (18b) y la segunda salida (12b) , conteniendo el trayecto de conexión (10a) y el trayecto de desconexión (10b) , en cada caso, un convertidor de nivel (20a, b) que presenta la respectiva entrada (18a, b) , un amplificador de corriente (22a, b) activado por el convertidor de nivel (20a, b) y una etapa final (24a, b) activada por el amplificador de corriente (22a, b) y dotada de la respectiva salida (12a, b) .

2. Circuito excitador (4) según la reivindicación 1, en el que el convertidor de nivel (20a, b) , el amplificador de 15 corriente (22a, b) y la etapa final (24a, b) son de construcción discreta.

3. Circuito excitador (4) según la reivindicación 1 o 2, en el que el convertidor de nivel (20a, b) contiene un transistor (Q1, Q5) con resistencias en serie (R1-3, R5-7) unido mediante su entrada de control (13) con la entrada (18a, b) .

4. Circuito excitador (4) según cualquiera de las reivindicaciones anteriores, en el que el amplificador de corriente (22a, b) es un seguidor de emisor (26a, b) que contiene dos transistores (Q2-3, Q6-7) .

5. Circuito excitador (4) según cualquiera de las reivindicaciones anteriores, en el que la etapa final (24a, b) contiene un MOSFET (S1, S2) con una resistencia en serie (R4, R8) unido mediante su salida de potencia (28) con la salida (12a, b) .

6. Circuito excitador (4) según cualquiera de las reivindicaciones anteriores, en el que al menos aproximadamente la primera tensión (UVP) es de +15 V, la segunda tensión (UVN) está en el intervalo de -8 V a -15 V y la tercera tensión 25 (UL) es de +3, 3 V, y el potencial de referencia (GND) es masa.

7. Circuito excitador (4) según cualquiera de las reivindicaciones anteriores, en el que el circuito lógico (8) es un PLD.

8. Circuito excitador (4) según cualquiera de las reivindicaciones anteriores, que es un circuito excitador para activar un IGBT actuante como interruptor de semiconductor de potencia (2) .

Patentes similares o relacionadas:

Circuito de conmutación de cascode, del 10 de Julio de 2019, de United Silicon Carbide Inc: Un circuito de conmutación de cascode que comprende un dispositivo semiconductor normalmente encendido , un dispositivo semiconductor normalmente […]

Célula de conmutación y circuito de compensación para la misma, del 19 de Junio de 2019, de TM4 Inc: Una célula de conmutación configurada para limitar la sobretensión de conmutación y para limitar la corriente de recuperación, que comprende: un conmutador […]

Procedimiento para controlar dos IGBT de conducción inversa, conectados eléctricamente en serie, de un semipuente, del 17 de Mayo de 2019, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para controlar dos IGBT de conducción inversa (T1, T2) conectados eléctricamente en serie, de un semipuente , en el cual se encuentra […]

Dispositivo y circuito de control de un componente electrónico de potencia, procedimiento de mando y distribuidor asociados, del 12 de Abril de 2017, de ALSTOM Transport Technologies: Circuito de control de la apertura y del cierre de un componente electrónico de potencia , teniendo el componente electrónico de potencia […]

Procedimiento y configuración de circuitos para conmutar un interruptor semiconductor, del 14 de Diciembre de 2016, de CONTI TEMIC MICROELECTRONIC GMBH: Procedimiento para conmutar un interruptor semiconductor (HS1) desde un primer estado de conexión estático hasta un segundo estado de conexión […]

Circuito y procedimiento de accionamiento para MOSFET, del 15 de Junio de 2016, de NORTH-WEST UNIVERSITY: Un procedimiento de utilización de un circuito para accionar un dispositivo semiconductor de puerta aislada que comprende como un primer […]

CIRCUITO INTEGRADO PARA LA GENERACION DE UNA SEÑAL DE ACTIVACION PARA UN TRANSISTOR BIPOLAR CON PUERTA AISLADA (IGBT)., del 16 de Junio de 2006, de SIEMENS AG: Circuito integrado para la generación de una señal de activación para un IGBT con una conexión de entrada para una señal de control generada por medio de un microcontrolador […]

PROCEDIMIENTO Y DISPOSITIVO PARA REGULAR, EN FUNCION DEL ESTADO, EL COMPORTAMIENTO TRANSITORIO DE INTERRUPTORES DE SEMICONDUCTOR DE POTENCIA, del 1 de Agosto de 2008, de CT-CONCEPT TECHNOLOGIE AG: Procedimiento para regular un proceso transitorio de conmutación de al menos un interruptor de semiconductor de potencia (S1-S4) que comprende al menos un terminal […]

PROCEDIMIENTO Y DISPOSITIVO PARA REGULAR, EN FUNCION DEL ESTADO, EL COMPORTAMIENTO TRANSITORIO DE INTERRUPTORES DE SEMICONDUCTOR DE POTENCIA, del 1 de Agosto de 2008, de CT-CONCEPT TECHNOLOGIE AG: Procedimiento para regular un proceso transitorio de conmutación de al menos un interruptor de semiconductor de potencia (S1-S4) que comprende al menos un terminal […]