Procedimiento de fabricación de un transistor de efecto de campo de unión JFET.

Procedimiento de fabricación de un transistor de efecto de campo de tipo de puerta en zanja que comprende:

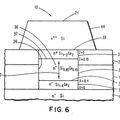

- La formación (110) de al menos una zanja (11, 12, 13) en una capa activa semiconductora (1) de un primer tipo de conductividad de un substrato que comprende dos caras opuestas denominadas cara delantera y cara trasera,

- La implantación primaria (120) de iones que tienen un segundo tipo de conductividad de modo que se implante cada zanja del substrato para formar una región activa de puerta,

- El depósito (160) de una capa de silicio policristalino del segundo tipo de conductividad sobre la región activa de puerta implantada,

- La oxidación parcial (160) de la capa de silicio policristalino para obtener una película (3') aislante eléctricamente de silicio policristalino oxidado sobre una subcapa de silicio policristalino no oxidado, formando la subcapa de silicio policristalino y la zona implantada una región activa de puerta, y

- La metalización (180) del substrato sobre su cara delantera para formar una región activa de fuente, y

- La metalización (180) del substrato sobre la otra cara para formar una región activa de drenaje.

estando caracterizado el citado procedimiento por que la etapa de formación comprende las subetapas de:

- Depósito de una máscara primaria (4) sobre la cara delantera del substrato semiconductor, incluyendo la máscara primaria una abertura principal (41) y dos aberturas subsidiarias (42, 43), siendo las dimensiones de la abertura principal superiores a las dimensiones de las aberturas subsidiarias,

- Grabado primario del substrato a través de la abertura principal para formar una zanja principal (11), y a través de la aberturas subsidiarias para formar dos zanjas subsidiarias (12, 13),

siendo realizada la etapa de implantación primaria a través de la máscara primaria, y por que el procedimiento comprende además:

- una etapa (130) de depósito de una máscara de grabado secundario (5) sobre la cara delantera del substrato posteriormente a la etapa de implantación primaria, incluyendo la citada máscara de grabado secundario una abertura de grabado secundario (51) a nivel de la zanja principal (11),

- una etapa (140) de grabado secundario del substrato a través de la abertura de grabado secundario (51) para formar una zanja secundaria (111) en la zanja principal (11).

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/FR2012/051983.

Solicitante: Institut National des Sciences Appliquées de Lyon.

Nacionalidad solicitante: Francia.

Dirección: 20 Avenue Albert Einstein 69100 Villeurbanne.

Inventor/es: MILLAN, JOSE, GODIGNON, PHILIPPE, TOURNIER,DOMINIQUE, CHEVALIER,FLORIAN.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H01L21/04 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 21/00 Procedimientos o aparatos especialmente adaptados para la fabricación o el tratamiento de dispositivos semiconductores o de dispositivos de estado sólido, o bien de sus partes constitutivas. › los dispositivos presentan al menos una barrera de potencial o una barrera de superficie, p. ej. una unión PN, una región de empobrecimiento, o una región de concentración de portadores de cargas.

- H01L29/808 H01L […] › H01L 29/00 Dispositivos semiconductores adaptados a la rectificación, amplificación, generación de oscilaciones o a la conmutación que tienen al menos una barrera de potencial o de superficie; Condensadores o resistencias, que tienen al menos una barrera de potencial o de superficie, p. ej. unión PN, región de empobrecimiento, o región de concentración de portadores de carga; Detalles de cuerpos semiconductores o de sus electrodos (H01L 31/00 - H01L 47/00, H01L 51/05 tienen prioridad; otros detalles de los cuerpos semiconductores o de sus electrodos H01L 23/00; consistentes en una pluralidad de componentes de estado sólido formados en o sobre un sustrato común H01L 27/00). › de unión PN.

PDF original: ES-2586331_T3.pdf

Patentes similares o relacionadas:

Método para fabricar un JFET de triple implante, del 8 de Abril de 2020, de United Silicon Carbide Inc: Un método para crear un JFET (o 'transistor de efecto de campo de unión o juntura'), que comprende: a. aplicar una primera máscara […]

Dispositivo de transistor bipolar de compuerta aislada que comprende un transistor de efecto de campo de compuerta aislado conectado en serie con un transistor de efecto de campo de ensamblaje que tiene un contacto de drenaje modificado, del 13 de Diciembre de 2017, de Eklund, Klas-Håkan: Un dispositivo transistor bipolar de puerta aislada en el que se conecta un primer transistor de efecto de campo de puerta aislada en serie con un segundo transistor […]

METODO PARA LA FABRICACION DE PRENDAS INTERIORES Y SIMILARES., del 1 de Noviembre de 1982, de HASHIMOTO,KENJI YABUMOTO,KENJI: METODO PARA LA FABRICACION DE PRENDAS INTERIORES Y SIMILARES. COMPRENDE LAS SIGUIENTES OPERACIONES: PRIMERA, SE CONFECCIONA UNA PIEZA FRONTAL PARA CUBRIR […]

TRANSISTORES DE EFECTO DE CAMPO DE UNION VERTICAL, del 1 de Febrero de 2008, de INTERNATIONAL BUSINESS MACHINES CORPORATION: SE DESCRIBE UN TRANSISTOR DE EFECTO DE CAMPO DE UNION Y UN METODO PARA PRODUCIRLO, QUE INCORPORAN CAPAS SEMICONDUCTORAS HORIZONTALES (14, 16, […]

TRANSISTORES DE EFECTO DE CAMPO DE UNION VERTICAL, del 1 de Febrero de 2008, de INTERNATIONAL BUSINESS MACHINES CORPORATION: SE DESCRIBE UN TRANSISTOR DE EFECTO DE CAMPO DE UNION Y UN METODO PARA PRODUCIRLO, QUE INCORPORAN CAPAS SEMICONDUCTORAS HORIZONTALES (14, 16, […]

Convertidor matricial para la transformación de energía eléctrica, del 15 de Marzo de 2017, de ALSTOM Transport Technologies: Convertidor matricial para la transformación de energía eléctrica entre al menos una fuente de tensión , especialmente una red de alimentación […]