Downconverter integrado con diversidad de polarización para receptor óptico coherente con multiplexación por polarización.

Downconverter con diversidad de polarización para receptor óptico coherente con multiplexación por polarización,

susceptible de ser integrado monolíticamente. Dicho downconverter, la red de diversidad de polarización del estado de la técnica es sustituida por una red de acoplo y diversidad de polarización, asistida en fase, que reduce, o incluso elimina, la necesidad de utilizar rotadores y separadores de polarización con elevadas relaciones de extinción. Esto permite realizar la funcionalidad de diversidad de polarización con gran precisión basándose en componentes individuales de menores prestaciones (en cuanto a su capacidad de manipular la polarización), lo que facilita la integración monolítica del receptor completo en una única oblea. Asimismo es objeto de la invención un receptor óptico coherente que comprende dicho downconverter con diversidad de polarización para señales ópticas multiplexadas en polarización.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201300742.

Solicitante: UNIVERSIDAD DE MALAGA.

Nacionalidad solicitante: España.

Inventor/es: HALIR,Robert, ORTEGA MOÑUX,Alejandro, Molina Fernández,Iñigo, ALONSO RAMOS,Carlos Alberto, REYES IGLESIAS,Pedro.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04B10/64 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04B TRANSMISION. › H04B 10/00 Sistemas de transmisión que utilizan haces de radiación electromagnéticas u otro tipo de ondas, p. ej. la luz, los infrarrojos, ultravioletas o radiación corpuscular, p. ej. comunicación cuántica. › Heterodino.

Fragmento de la descripción:

DOWNCONVERTER INTEGRADO CON DIVERSIDAD DE POLARIZACiÓN PARA RECEPTOR ÓPTICO COHERENTE CON MULTIPLEXACiÓN POR POLARIZACiÓN

OBJETO DE LA INVENCiÓNLa presente invención pertenece al campo de las telecomunicaciones y la óptica integrada, y más concretamente a los receptores integrados para sistemas de comunicaciones ópticas coherentes basados en multiplexación por polarización.

ANTECEDENTES DE LA INVENCiÓN

El incremento de los requerimientos de ancho de banda de los sistemas de comunicación ópticos actuales ha hecho que éstos hayan evolucionado, desde los basados en división por longitud de onda con modulación de la amplitud de la señal, a los llamados sistemas coherentes que permiten detectar amplitud y fase de la señal, mejorando la eficiencia espectral del sistema. El siguiente paso en el camino hacia los sistemas de nueva generación es la utilización de esquemas basados en multiplexación por polarización. Estos sistemas, al mandar distinta información en dos polarizaciones ortogonales, permiten doblar la eficiencia espectral respecto a los sistemas convencionales.

Los receptores ópticos coherentes del estado de la técnica (1000) [E. Ip, A. P. Tao, D. J. F. Barros y J. M. Khan, Opt. Express, 16 (2) , pp. 753-791 (2008) ] para modulaciones basadas en multiplexación por polarización, como el descrito en la figura 1, se componen de tres subsistemas: el oscilador local (1100) , un conversor inferior o 'downconverter' con diversidad de polarización (1200) Y un de subsistema procesado de señal (1300) .

El oscilador local es habitualmente un láser cuya longitud de onda se ajusta a un valor cercano a la de la señal óptica que se desea demodular. La señal de oscilador local se introduce junto con la señal a demodular en el 'downconverter' con diversidad de polarización cuya función es trasladar a banda base la señal recibida. Esa señal en banda base se introduce a un bloque de procesado de señal que realiza una gran variedad de funciones necesarias para la correcta recepción, entre las que se encuentran, la ortogonalización de las etapas anteriores, la recuperación de portadora, el sincronismo de símbolo, la demultiplexación de la polarización y la cancelación de la dispersión tal y como están descritos en el estado de la técnica [S. J. Savor y , IEEE J. Sel. Top. Quantum Electron., 16 (5) , pp. 1164 (2010) ].

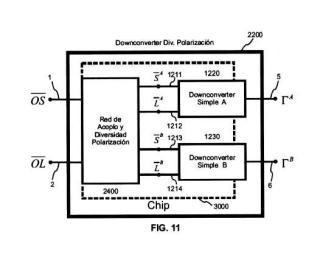

A su vez, el 'downconverter' con diversidad de polarización, figura 2, está formado por un bloque que implementa la funcionalidad de diversidad de polarización (1210) y dos 'downconverters' simples (1220, 1230) , cada uno de los cuales incluye, según se muestra en la figura 3, una red de diversidad de fase (100) , una etapa de conversión optoelectrónica (200) y una etapa de combinación lineal (300) que puede ser analógica o digital. Cuando en la entrada (1) del receptor se introduce la señal a demodular OS, que contiene información (modulada en fase y cuadratura) sobre cada una de sus dos polarizaciones (i.e. OS = [OSx, OsJ) y en la entrada (2) se introduce un oscilador local OL, que tiene un estado de polarización arbitrario (i.e. aL = [OL"OLy }) y cuya longitud de onda se escoge de forma que esté muy

cercana a la longitud de onda central de la señal recibida, en las salidas (3, 4) se obtienen las señales demoduladas que tratan de recuperar la información de la señal original, de forma que idealmente rx -OS, y r y -OSy.

Los bloques de diversidad de fase y conversión optoelectrónica de cada uno de los 'downconverters' simples, (1220, 1230) , están constituidos habitualmente, tal y como se muestra en la figura 4a, por un híbrido de 90°

(110) seguido de dos fotodetectores balanceados (210) [R. Kunkel, H.G. Bach, D. Hoffmann, C.M. Weinert, 1. Molina-Fernández, R. Halir, Proc. Int.

Conf. InP and Related Materials, pp. 167-170 (2009) ]. Aunque también existen otras posibilidades, que se presentan en la figura 4, como por ejemplo un híbrido de 90° (110) Y cuatro fotodetectores (220) [A Carena, V. Curri, P. Poggiolini, F. Forghieri, IEEE Photon. Photon. Technol. Lett., 20 (15) , pp. 12811283 (2008) ] figura 4b, o híbrido de 120° (120) seguidos de tres fotodetectores (220) [P.J. Reyes, A Ortega-Moñux, I Molina-Fernández, Opt. Express, 20 (21) , pp. 23013-23018 (2012) ], figuras 4c y 4d.

El bloque de combinación lineal (300) toma como entradas las salidas de los fotodetectores y mediante combinaciones lineales de las mismas trata de generar el símbolo demodulado. Así, por ejemplo, en el caso de usar híbridos de 90° y 2 fotodetectores balanceados [R. Kunkel, H.G. Bach, D. Hoffmann, C.M. Weinert, 1. Molina-Fernández, R. Halir, Proc. Int. Conf. InP and Related Materials, pp. 167-170 (2009) ], los propios fotodiodos balanceados realizan la función de combinación lineal (resta) , figura 4a, por lo que la funcionalidad de los bloques de conversión O/E (200) Y combinación lineal (300) está siendo realizada por los fotodiodos balanceados (210) . Por el contrario, en el caso de usar híbridos de 90° y fotodiodos simples [C.R. Doerr,

L.L. Buhl, Y. Beayens, R. Aroca, s. Chandrasekhar, X. Liu, L. Chen, Y.K. Chen, IEEE Photon. Technol. Lett., 23 (12) , pp. 762-764] el bloque de combinación lineal se puede conseguir mediante el uso de amplificadores diferenciales de transimpedancia (ATI) , figura 4b, que realizan la resta analógica de las señales de salida dos a dos. Por último, es necesario destacar que, para todos los casos, la combinación lineal de las salidas de los fotodetectores puede realizarse de forma analógica o digital. Esto se ilustra para el caso del híbrido de 120° en el cual existe la posibilidad de realizar la combinación lineal de las tres señales de salida de forma analógica tal y como ha sido propuesto en [C. Xie, P.J. Winzer, G. Raybon, AH. Gnauck, B. Zhu, T. Geisler, B. Edvold, Proc. ECOC, (2011) ], figura 4c, o bien pueden muestrearse las tres salidas y realizar la combinación lineal de forma digital tal y como se propone en [P.J. Reyes, A Ortega-Moñux, I Molina-Fernández, Opt. Express, 20 (21) , pp. 23013-23018 (2012) ], figura 4d.

Todas estas arquitecturas, aunque diferentes, realizan sin embargo, la misma funcionalidad. Esta funcionalidad que es bien conocida en el estado de la técnica [S. J. Savor y , IEEE J. Sel. Top. Quantum Electron., 16 (5) , pp. 1164 (2010) ], puede ser resumida diciendo que, si a cada una de las dos entradas de un 'downconverter' simple (por ejemplo el A) , le llegan respectivamente la señal de información con una única polarización y el oscilador local (SA y LA respectivamente) , y estas entradas tienen la misma frecuencia y el mismo estado de polarización, a su salida se obtienen una serie de señales a partir de las cuales puede calcularse el símbolo rA (5) que contiene información sobre dicho estado de polarización de la señal. Por el contrario, si a las dos entradas de un 'downconverter' simple le llegan la señal de información y el oscilador local con estados de polarización ortogonales, se generan unas señales de salida nulas.

Para abaratar el coste de estos receptores existe un gran interés en integrar el mayor número de bloques en un mismo circuito integrado o 'chip'. La integración de todos los componentes es actualmente muy complicada, y como paso intermedio se está trabajando en la posibilidad de integrar en el mismo 'chip' sólo el conversor inferior o 'downconverter' con diversidad de polarización (1200) [European FP7 Project Mirthe, (http://www.iest-mirthe.eu) ]. Este tipo de 'downconverter' con diversidad de polarización integrado, cuyo diagrama se pude ver en la figura 5 trata de realizar en la misma oblea semiconductora (o 'chip') , los tres subsistemas que lo componen: el subsistema de diversidad de polarización (1210) , y los dos 'downconverters' simples (1220) y (1230) junto con el subsistema de acoplo de potencia óptica al 'chip' (necesario para inyectar la luz proveniente del exterior al 'chip' óptico) , reduciendo así el esfuerzo necesario para su integración y ensamblaje y por lo tanto también su coste.

Aunque teóricamente es factible la integración monolítica de todos esos subsistemas en un mismo 'chip', sin embargo, la precisión requerida para la implementación monolítica de la funcionalidad de diversidad de polarización según las propuestas del estado de la técnica hace los diseños extremadamente sensibles a los pequeños errores de fabricación. Por ello, en la práctica, esta solución es ineficiente y no se utiliza comercialmente. Así, existen en el mercado receptores ópticos coherentes con multiplexación de polarización basados en diversas tecnologías [C.R. Ooerr, L.L. Buhl, Y. Beayens, R. Aroca, s. Chandrasekhar, X. Liu, L. Chen, Y.K. Chen, IEEE Photon. Technol. Lett.,...

Reivindicaciones:

1. 'Downconverter' con diversidad de polarización para señales ópticas 5 multiplexadas en polarización que comprende:

• Dos puertas de entrada, por donde se recibe la señal óptica a demodular OS (1) que contiene información en sus dos polarizaciones (OSx' OSy' Ecuación 11) Y otra por donde se recibe el

oscilador local OL (2) que tiene un estado de polarización arbitrario (OLx' OLy ' Ecuación 12) ;

(Ecuación 11)

(Ecuación 12)

15

• Una red de acoplo y diversidad de polarización (2400) , que es una

red óptica que tiene como entradas la señal recibida (1) Y el

oscilador local (2) y se encarga de distribuir las dos polarizaciones de -A -A estas dos señales entre sus cuatro puertas de salida S (1211) , L

20 (1212) , -B S -B (1213) Y L (1214) que constituyen la entrada de dos

'downconverters' simples (1220, 1230) ; dicha red (2400) definida por

las cuatro matrices de Jones (OJ, 1, OJ, :, OJt, OJt) que

establecen las relaciones de amplitud y fase existentes, para los dos

estados de polarización, entre las entradas y las salidas de la red

25 (Ecuación 13) ;

S A= OJ: . OS LA = OJ: .aL

(Ecuación 13)

SB = OJ: 'OS LB = OJ~ 'OL

• y dos 'Downconverter' simples (1220, 1230) que toman como entrada - A -B

dos señales ópticas, una de señal (S , S ; 1211, 1213) Y otra de - A -B

oscilador local (L , L ; 1212, 1214) , Y genera a la salida dos señales eléctricas (IA, lB, QA, QB; 1221, 1231, 122, 1232) , en formato analógico o digital, que constituyen las señales complejas (rA, rB 5, 6) definidas por la (Ecuación 14) ,

r A =M, A ·SA +M; .~) , r B =M, B 'SB +M: .~) donde () * denota el conjugado sin trasponer; trabajando dichos 'downconverters' simples A (1220) Y B (1230) en condiciones normales de operación (errores acotados del hardware) , M;, B .... O, quedando las señales rA rB

complejas (5) , (6) definidas por la (Ecuación 15) , r A r B

.... M, A 'SA =~) 'LA·SA, .... M, B 'SB = W) 'LB ·SB, donde (y denota la transpuesta conjugada y LA, B son las matrices características de los 'downconverters' A (1220) Y B (1230) , según se define en la (Ecuación 16) ;

(Ecuación 16)

donde L~:: números complejos que relacionan las entradas y salidas de dichos 'downconverters' A (1220) Y B (1230) ;

dicho "downconverter" caracterizado por que la red de acoplo y diversidad de polarización (2400) opera de tal forma que, para los 'downconverters'

simples A (1220) Y B (1230) , caracterizados por LA, B , Y la señal del oscilador local OL (2) utilizados, maximiza el cumplimiento de la condición de ortogonalidad (Ecuación 19)

= =T =

M·M =1 (Ecuación 19)

[q) ' 'OJ

A .~A 'OJ1]

=M= 'VI., _L ___5

(Ecuación 17)

'VI., ~J'OJL B .~B 'OJ5 B

basándose para ello en establecer relaciones precisas en amplitud y fase entre los dos estados de polarización de las entradas y las salidas de la red, es decir, en establecer los módulos de los elementos de sus matrices de Jones (OJ;, OJ, ~, OJ:, OJf) (Ecuación 17) así como las fases adecuadas de dichos elementos.

2. 'Downconverter' con diversidad polarización según la reivindicación anterior caracterizado por que al menos la red de acoplo y diversidad de polarización (2400) , y las redes de diversidad de fase (100) que forman parte de los 'downconverters' simples, son monolíticamente integrables en el mismo 'chip'

3. 'Downconverter' según cualquiera de las reivindicaciones 1 ó 2 caracterizado por que la red de acoplo y diversidad de polarización (2400) comprende una sección de acoplo chip-fibra (1430) y una red de distribución de señales asistida en fase (2440) .

4. 'Downconverter' según la reivindicación anterior caracterizado por que la red de acoplo chip-fibra (1430) comprende un acoplador para la señal (1410) y otro para el oscilador local (1420) que relacionan la señal a

demodular OS (1) Yel oscilador local OL (2) con las entradas S (1411) Y L (1421) de la red de distribución asistida en fase (2440) según (Ecuación 23) y (Ecuación 24)

s~ [COS (Os)

sin (Os)

L~ [COS (O, .1 sin (OL)

-Sin (Os) ]

'OS (Ecuación 23)

cos (Os) -Sin (O, .1]. OL

(Ecuación 24)

COS (OL)

5. 'Downconverter' según cualquiera de las reivindicaciones 3 ó 4 caracterizado por que la red de distribución asistida en fase (2440) presenta '- ---A -A -B -B

dos entradas (S, L; 1411, 1421) Y cuatro salidas (S , L , S , L ; 1211,

1212, 1213, 1214) , relacionadas entre sí por cuatro matrices de Jones (J, ~ ,

J, ~, JJ~' Jr~) que establecen las relaciones de amplitud y fase existentes, 10 para los dos estados de polarización, entre las entradas y las salidas de la red conforme a la (Ecuación 20) ,

SA =J, :'S LA =J~'L

(Ecuación 20)

SB =J, ~'S' LB =J:·L

6. 'Downconverter' según la reivindicación anterior caracterizado por que la red de acoplo y diversidad de polarización (2400) opera de tal forma que maximiza el cumplimiento de la condición de ortogonalidad, particularizada usando la (Ecuación 24) y la (Ecuación 20) , según se define en la (Ecuación 25)

==T =

M·M =! (Ecuación 25)

M = [ (COS (OL) -Sin (OL) ) -J~ .~A 'J'~l

(COS (OL) -sin (OrJ) -J~ .~B • J%

donde LA, B son las matrices características de los 'downconverters' A (1220) Y 8 (1230) según se define en la (Ecuación 16) .

7. 'Downconverter' según la reivindicación anterior caracterizado por que el 5 ángulo de proyección del oscilador local sobre el 'chip' eL y el desfase diferencial cfJDiSl se eligen de manera que se maximiza el cumplimiento de la (Ecuación 32) Y (Ecuación 33) ,

[la~12 'la, ~12 'IL~12 -lbfl2'lb, ~12 'IL!1]'cos2 (eJ=

(Ecuación 32)

[lafl2'la, ~12 'IL~12 -lbtl2 'lb, ~12 'IL:1 2 ]'Sin 2 (eL) 2

la~ l'la~ l'lbfl'lb, ~ I·IL ~12·IL!1.cos2 (eL) -exp (-jcfJDiSl ) +

(Ecuación 33)

+ lafl'la%I'lbr~I'lb, :I'IL:12 'IL~12 .sin2 (eL ) = o y por tanto se maximiza el cumplimiento de la condición de ortogonalidad definida en la (Ecuación 25) ; dicho desfase diferencial cfJDist definido según la (Ecuación 34) , 15

donde I1cfJ: = q;:X -q;~ (con p=A, B y q=S, L) son los desfases diferenciales de polarización en cada uno de dichos caminos, q;:X, q;~ (con p=A, B y q=S, L)

los desfases introducidos por la red de distribución de señales asistida en fase, definidos en la (Ecuación 21) , y q;:: = arg (L~::) los desfases introducidos por los 'donconverters' A (1220) Y 8 (1230) .

8. 'Downconverter' según la reivindicación 7 caracterizado por que se eligen el ángulo de proyección del oscilador local sobre el 'chip' eL = (2k + 1) ' 45 0,

siendo k un número entero, y el desfase diferencial CPDist = ±180° , para maximizar el cumplimiento de la condición de ortogonalidad definida en la (Ecuación 25) .

9. 'Downconverter' según cualquiera de las reivindicaciones 3 a 5 caracterizado por que los 'downconverter' simples (1220) ó (1230) ,

presentan un comportamiento ideal y por tanto M:, B = O , LA, B =1 (con 1 la matriz identidad) , siendo LA, B las matrices características de los 'downconverters' A (1220) Y 8 (1230) , según se define en la (Ecuación 16) .

10. 'Downconverter' según la reivindicación anterior caracterizado por que el

ángulo de proyección del oscilador local sobre el 'chip' (J L Y el desfase diferencial, se eligen de manera que se maximice el cumplimiento de (Ecuación 26) y (Ecuación 27) ,

[latl2'la~12 -lbtl2 'lbffI2]'COS2 (eL ) = [laZl2'la, ~12 -lbtl2 'lb~12] 'sin 2 (eL)

(Ecuación 26)

latl'la~I'lb:I'lb, :I' cos2 (eL ) -exp (-jCPDist) + la:I·laffl·lbt l'lb~ l· sin2 (eL ) = O

(Ecuación 27)

y por tanto se maximice el cumplimiento de la condición de ortogonalidad definida en la (Ecuación 25) ; dicho desfase diferencial CPDist definido según la (Ecuación 28)

(Ecuación 28)

siendo ~4J: = CP~ -CP~ (con p=A, B y q=S, L) los desfases diferenciales de polarización en cada uno de dichos caminos y cp~, CP~ (con p=A, B y q=S, L) los desfases introducidos por la red de distribución de señales asistida en fase, definidos en la (Ecuación 21) .

11. 'Downconverter' según cualquiera de las reivindicaciones 3 a 10 caracterizado por que la red de distribución de señales asistida en fase (2440) comprende dos repartidores de señal 'Split' S (440) Y 'Split' L (450) Y unos bloques de fase controlada o desfasadores (510) , (520) , (530) , (540) , (550) , (560) .

12. 'Downconverter' según la reivindicación anterior caracterizado por que los repartidores de señal 'Split' S (440) Y 'Split' L (450) se implementan con divisores de potencia (420) .

13. 'Downconverter' según la reivindicación 11 caracterizado por que los repartidores de señal 'Split' S (440) Y 'Split' L (450) se implementan con separadores de polarización (410) .

14. 'Downconverter' según cualquiera de las reivindicaciones 11 a 13 caracterizado por que los bloques de fase controlada o desfasadores (510) , (520) , (530) , (540) , (550) , (560) se implementan con guías-ondas de interconexiónWK~ (2123) , Wg% (2124) , Wg: (2125) , Wg: (2126) .

15. 'Downconverter' según cualquiera de las reivindicaciones 1 a 14 caracterizado por que el sistema de inyección de luz sobre el 'chip' se realiza por el borde del "chip' ('edge coupling') .

16. 'Downconverter' según cualquiera de las reivindicaciones 1 a 14 caracterizado por que el sistema de inyección de luz sobre el "chip' está realizado a través de cualquiera de las superficies del 'chip' mediante acoplo

por rejilla de difracción o 'grating'.

17. 'Downconverter' según cualquiera de las reivindicaciones 4 a 16

caracterizado por que el ajuste del ángulo eL se realiza de forma mecánica, electrónica o térmica.

18. 'Downconverter' según cualquiera de las reivindicaciones 3 a 17 en el que la red de distribución de señales asistida en fase (2440) incorpora cualquier tipo de ajuste interno dentro del chip (térmico, electroóptico o cualquier otro) para modificar sus relaciones de fase entrada-salida.

19. 'Downconverter' según cualquiera de las reivindicaciones 1 a 18 caracterizado por que cada uno de los 'downconverters' simples (1220, 1230) está basado en un híbrido de 90°.

20. 'Downconverter' según la reivindicación anterior caracterizado por que cada uno de los 'downconverters' simples (1220, 1230) presenta conversión IQ analógica, incluyendo una etapa de conversión optoelectrónica.

21. 'Downconverter' según la reivindicación anterior caracterizado por que la etapa de conversión optoelectrónica comprende dos fotodotectores balanceados y dos amplificadores de transimpedancia no balanceados seguidos de dos muestreadores (conversores AtD) .

22. 'Downconverter' según la reivindicación 20 caracterizado por que la etapa de conversión optoelectrónica comprende cuatro fotodotectores y dos amplificadores de transimpedancia balanceados seguidos de dos muestreadores (conversores AtD) .

23. 'Downconverter' según la reivindicación 19 caracterizado por que cada uno de los 'downconverters' simples (1220, 1230) presenta conversión IQ

digital, incluyendo una etapa de conversión optoelectrónica.

24. 'Oownconverter' según la reivindicación anterior caracterizado por que la etapa de conversión optoelectrónica comprende cuatro fotodotectores y cuatro amplificadores de transimpedancia, cuatro muestradores (conversores AtO) y una red de combinación digital.

25. 'Oownconverter' según cualquiera de las reivindicaciones 1 a 18 caracterizado por que cada uno de los 'downconverters' simples (1220, 1230) está basado en un híbrido de 120°.

26. 'Oownconverter' según la reivindicación anterior caracterizado por que cada uno de los 'downconverters' simples (1220, 1230) presenta conversión la analógica, incluyendo una etapa de conversión optoelectrónica.

27. 'Oownconverter' según la reivindicación anterior caracterizado por que la etapa de conversión optoelectrónica comprende tres fotodotectores y tres amplificadores de transimpedancia, una red de combinación analógica y dos muestradores (conversores AtO) .

28. 'Oownconverter' según la reivindicación 25 caracterizado por que cada uno de los 'downconverters' simples (1220, 1230) presenta conversión la digital, incluyendo una etapa de conversión optoelectrónica.

29. 'Oownconverter' según la reivindicación anterior caracterizado por que la etapa de conversión optoelectrónica comprende tres fotodotectores, tres amplificadores de transimpedancia, tres muestradores (conversores AtO) y una red de combinación digital.

30. Receptor óptico coherente para señales multiplexadas en polarización que comprende un 'downconverter' con diversidad de polarización para

señales ópticas multiplexadas en polarización conforme cualquiera de las reivindicaciones anteriores 1 a 29.

31. Receptor óptico coherente según la reivindicación anterior que además comprende:

• Una puerta de entrada por donde se recibe la señal óptica a demodular OS (1) que tiene una cierta longitud de onda central y

contiene información en sus dos polarizaciones (OSx, OSy) ;

• un oscilador local (1100) que genera una señal óptica OL (2) cuya longitud de onda es cercana o idéntica a la longitud de onda central de la señal recibida y que tiene un estado de polarización arbitrario OLx' OLy; Y

• un subsistema de procesado de señal (1300) analógico o digital que rA rB

toma como entradas las señales electronicas (5) y (6) provenientes del 'downconverter' (2200) y obtiene a su salida las señales demoduladas fx (3) Y r y (4) que recuperan las señales de información de la señal original OSx y OSy respectivamente utilizando para ello los algoritmos habituales en los receptores ópticos coherentes para la ortogonalización, recuperación de portadora, sincronismo de símbolo, demultiplexación de la polarización y cancelación de la dispersión tal y como están descritos en el estado de la técnica.

32. Receptor óptico coherente según cualquiera de las reivindicaciones 30 ó

caracterizado por que para la obtención de rx (3) y r y (4) a partir de rA

(5) y r B (6) se utilizan los algoritmos de demultiplexación de la polarización usados para corregir el giro arbitrario de polarización que introduce el canal de fibra óptica.

33. Receptor óptico coherente según cualquiera de las reivindicaciones 30 a 32 caracterizado por que el oscilador local (1100) es monolíticamente integrable en el mismo 'chip' (3000) junto con las redes de diversidad de polarización y de diversidad de fase.

34. Receptor óptico coherente para señales multiplexadas en polarización según cualquiera de las reivindicaciones 30 a 32 caracterizado por que el que el oscilador local (1100) es externo al 'chip' (3000) , por lo que no se encuentra monolítica mente integrado junto con las redes de diversidad de polarización y de diversidad de fase.

35. Receptor óptico coherente para señales multiplexadas en polarización según cualquiera de las reivindicaciones 30 a 34 caracterizado por que presenta un subsistema de frecuencia intermedia y un segundo 'downconverter' realizado por medios electrónicos para trasladar la señal de frecuencia intermedia a banda base

36. Receptor óptico coherente para señales multiplexadas en polarización según cualquiera de las reivindicaciones 30 a 35 caracterizado por que presenta cualquier subsistema analógico o digital que permite llevar a cabo la demultiplexación de la polarización mediante la realización de un giro de polarización que pueda reaprovecharse para la obtención de rx (3) y r y (4)

a partir de r A (5) y rB (6) .

Patentes similares o relacionadas:

RECEPTOR HETERODINO INDEPENDIENTE DE LA POLARIZACIÓN PARA SEÑALES ÓPTICAS MODULADAS EN FASE Y CODIFICADAS DIFERENCIALMENTE, del 27 de Agosto de 2018, de UNIVERSITAT POLITECNICA DE CATALUNYA: Un receptor heterodino independiente de la polarización para señales ópticas moduladas en fase y codificadas diferencialmente. El receptor tiene una arquitectura […]

Receptor OFDM multi-longitud de onda, método de compensación del desplazamiento de frecuencia y sistema, del 18 de Mayo de 2016, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de compensación del desplazamiento de frecuencia, en donde el método de compensación del desplazamiento de frecuencia se utiliza […]

DOWNCONVERTER INTEGRADO CON DIVERSIDAD DE POLARIZACIÓN PARA RECEPTOR ÓPTICO COHERENTE CON MULTIPLEXACIÓN POR POLARIZACIÓN, del 5 de Febrero de 2015, de UNIVERSIDAD DE MALAGA: Downconverter con diversidad de polarización para receptor óptico coherente con multiplexación por polarización, susceptible de ser integrado […]

DOWNCONVERTER INTEGRADO CON DIVERSIDAD DE POLARIZACIÓN PARA RECEPTOR ÓPTICO COHERENTE CON MULTIPLEXACIÓN POR POLARIZACIÓN, del 5 de Febrero de 2015, de UNIVERSIDAD DE MALAGA: Downconverter con diversidad de polarización para receptor óptico coherente con multiplexación por polarización, susceptible de ser integrado […]