PROCEDIMIENTO ADAPTATIVO DE CALIBRACIÓN DÍGITAL CONCURRENTE DEL OFFSET EN COMPARADORES EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS).

El objeto de la presente invención es un procedimiento adaptativo para la calibración del offset de comparadores en convertidores analógico-digitales (ADCs).

La técnica que implementa permite ajustar mediante un control digital de bajo coste la tensión umbral efectiva o transición de los comparadores sin afectar al camino natural de señal, y por tanto, sin interrupción de la conversión A/D de la entrada analógica. Se trata, por tanto, de una técnica de calibración concurrente.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200930175.

Solicitante: CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC).

Nacionalidad solicitante: España.

Inventor/es: GINÉS ARTEAGA,Antonio José, PERALÍAS MACÍAS,Eduardo José, RUEDA RUEDA,Adoración.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M1/10 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 1/00 Conversión analógica/digital; Conversión digital/analógica (conversión de valores analógicos en, o a partir de una modulación diferencial H03M 3/00). › Calibración o ensayos.

PDF original: ES-2373282_A1.pdf

Fragmento de la descripción:

Procedimiento adaptativo de calibración digital concurrente del offset en comparadores en convertidores analógico-digitales (ADCs).

Objeto de la invención

El objeto de la presente invención es un procedimiento para la calibración del offset de comparadores en convertidores analógico-digitales (ADCs). La invención es completamente general y puede aplicarse a una arquitectura genérica de comparador La técnica que implementa permite ajustar mediante un control digital de bajo coste la tensión umbral efectiva o transición de los comparadores sin afectar al camino natural de señal, y por tanto, sin interrupción de la conversión A/D de la entrada analógica. Su aplicación a una topología de conversión directa (conocida como ADC de tipo flash) permite la calibración concurrente de la no-linealidad debido a dicho offset. La invención puede aplicarse sin restricción a otras topologías de conversión A/D que utilizan el convertidor flash como elemento constitutivo. Entre estas arquitecturas se incluyen las topologías sigma-delta, subranging, de interpolación, de aproximaciones sucesivas, interleaved, así como multi-etapa (también conocida como Pipeline).

Antecedentes de la invención

En un convertidor analógico-digital, denotado como convertidor A/D o simplemente ADC (Analog to Digital Converter, según sus siglas en inglés), la cuantificación de la señal de entrada en aplicaciones de alta velocidad se realiza mediante comparadores regenerativos de tipo latch. Gracias a la realimentación positiva se minimiza el tiempo de decisión para un consumo específico de potencia y área, y por tanto, se puede aumentar la frecuencia de conversión. Desafortunadamente, esta arquitectura es bastante sensible al proceso tecnológico, condiciones ambientales, así como al desapareamiento entre transistores y diferencias de cargas (véase la publicación J. He, S, Zhan, D. Chen, y R. Geiger, "A simple and accurate method to predict offset voltage in dynamic comparators", Proc. of IEEE Inter. Symp. on Cir. and Systems, ISCAS, pp. 1934-1937, May 2008), presentando offsets aleatorios (desviaciones de los umbrales de comparación respecto a la situación ideal) que pueden llegar a alcanzar los 300 mV en los procesos CMOS actuales. La gran variabilidad de los comparadores basados en un único latch (conocidos como stand-alone latch) limita su aplicación a convertidores de muy baja precisión, con resoluciones típicas de 1-2 bits.

El problema del offset en los comparadores se ha tratado de reducir tradicionalmente, e independientemente de la arquitectura de ADC considerada, mediante el empleo de técnicas en el dominio analógico. En la publicación, M. Bruccoleri y P. Cusinato, "Offset reduction technique for use with high speed CMOS comparators", IEE Electronics Letters, vol. 32, no. 13, pp. 1193-1194, Jun 1996, se introdujo un comparador de tipo stand-alone latch con múltiples realimentaciones para la reducción del offset. La principal desventaja de este método, al margen de la complejidad, es que provoca un aumento de la carga en los nudos internos que obviamente se traslada a una degradación de las prestaciones dinámicas. Otra posibilidad comúnmente considerada en la bibliografía, es el uso de un preamplificador a la entrada del latch, con o sin fase de cancelación del offset propio (véase B. Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill, 2000). Aunque este bloque adicional atenúa la contribución al offset total del latch por su ganancia, introduce un aumento no despreciable en el consumo total de potencia, al mismo tiempo que incrementa el tiempo de decisión reduciendo la frecuencia máxima de operación.

Una alternativa para solventar las limitaciones de las técnicas anteriores en aplicaciones de baja potencia y alta velocidad es la calibración. Como se detalla a continuación, estos métodos pueden clasificarse en dos grupos dependiendo de si la compensación del offset en los comparadores afecta o no al camino natural de la señal analógica de entrada.

En el primer grupo (técnicas de calibración con fase de medida no-concurrente) se incluyen todos aquellos procedimientos que rompen el camino de entrada para inyectar un estimulo de calibración. Por la naturaleza no-concurrente del proceso de medida, estas técnicas requieren en general la interrupción de la conversión A/D de la entrada, por lo que los errores debidos al envejecimiento de los componentes o cambios ambientales (temperatura, polarización, etc.) únicamente pueden ser calibrados en los periodos de inactividad del ADC.

En aquellos sistemas que operan de forma continua, y por tanto no disponen de periodos de inactividad, se utilizan recursos adicionales de hardware y/o procesamiento especial de señal que permitan realizar el proceso de medida no-concurrente sin afectar a la conversión A/D. En la publicación, I. R. Nadi, R. Baird, M. M. Kostelnik y M. Wesley, "Multi-bank flash ADC array with uninterrupted operation during offset calibration and auto-zero", U.S. Pat. No. 6,459,394, Oct. 2002, este proceso de calibración, de aquí en adelante llamado "concurrente-virtual", se lleva a cabo mediante el empleo de hardware redundante. Se incluyen comparadores adicionales que permiten mantener la conversión A/D de la entrada mientras se realiza la caracterización del offset en los dispositivos seleccionados. Una vez concluida la fase de medida la función de los comparadores se intercambia y comienza un nuevo ciclo de calibración. La principal desventaja de esta aproximación, al margen de los espúreos provocados por el intercambio periódico de los comparadores, es el coste adicional en hardware y potencia debido al hardware redundante.

En las publicaciones, R. Croman, M. Goldenberg, J. P. Hein, "Method and Circuit for Calibration of Flash Analog to Digital Converters", U.S. Pat. No. 5,990,814, Mar. 1999 y M. M. Kostelnik, R. Croman, M. Goldenberg, "Offset Calibration of Flash ADC Array", U.S. Pat. No. 6,084,538, Jul. 2000, se introdujo una técnica alternativa para la lograr la calibración concurrente-virtual. En este método se evita la duplicación de hardware, eliminando ocasionalmente una muestra de la señal de entrada, para sustituirla por un estímulo en DC que permita la compensación del offset. Para recuperar la información perdida durante el ciclo de calibración, la lógica digital realiza una interpolación de la muestra omitida reconfigurando los comparadores restantes. Al margen de la complejidad de la lógica resultante, la gran sensibilidad a la frecuencia de interpolación y la efectividad limitada para señales de alta frecuencia, esta técnica requiere un refresco periódico de las medidas de calibración ya que el valor del offset se almacena, siguiendo un método similar al introducido en B. Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill, 2000, de forma analógica en un condensador. En B. Jonsson, C. Jansson, "Comparator offset calibration for A/D converters", U.S. Pat. No. 7,075,465, Oct. 2005, se presentó un método de calibración no-concurrente que solventaba el problema de almacenamiento realizando una medida digital del offset. Durante la fase de medida de esta técnica, se interrumpe la conversión de entrada para inyectar un estímulo en DC, al mismo tiempo que se realiza un barrido en rampa de un código digital de calibración. Este código modifica mediante un convertidor digital-analógico adicional (los autores sugieren una realización capacitiva del mismo) la tensión umbral efectiva del comparador. El valor óptimo para la cancelación del offset se selecciona monitorizando independientemente la salida digital de cada comparador. De forma similar a los casos anteriores, para alcanzar un proceso de calibración concurrente (en modo virtual), esta técnica va a necesitar, bien incluir hardware adicional, con el consiguiente consumo de potencia y área, o bien omitir una de las muestras de entrada para incluir los estímulos de calibración (con la consiguiente degradación de las prestaciones debido a la interpolación).

El segundo grupo de técnicas de calibración existentes en la bibliografía, denominadas en contraposición al caso anterior "técnicas de calibración concurrente-real", realizan una corrección del offset en los comparadores sin afectar al camino natural de señal analógica de entrada, y por tanto, sin interrumpir la conversión A/D (fase de medida concurrente a la operación natural del comparador). Esta nueva aproximación hace uso de... [Seguir leyendo]

Reivindicaciones:

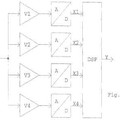

1. Procedimiento adaptativo de calibración digital concurrente del offset de los comparadores en convertidores analógico-digitales (ADCs) de tipo flash, caracterizado por disponer de un control digital en cada uno de los comparadores (Compi) del ADC bajo calibración (ADCUC), definido por un código digital, Ki, inicializado a cero, que modifica la posición efectiva de la transición o umbral de comparación ti asociado a dicho comparador (Compi) con un paso mínimo adaptativo δ, y que además comprende realizar las siguientes operaciones:

2. Procedimiento de acuerdo con la reivindicación 1, donde el aumento y disminución del código de calibración Kj se llevan a cabo según pasos constantes.

3. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde la operación de obtener una representación digital (Tj) de las transiciones actuales tj de los comparadores en el ADCUC se realiza mediante las siguientes operaciones:

4. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde el aumento de Tj+1 y la disminución de Tj de la estimación de las transiciones se llevan a cabo según pasos constantes.

5. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, que comprende la realizar un cambio de variable según la ecuación, INLj = Tj - Tj(ideal) u otro similar, de modo que las operaciones se realizan directamente sobre la nueva variable obtenida.

6. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, que comprende realizar un cambio de variable en el código de calibración Kj consecuente con el comparador programable que mantenga la realimentación negativa.

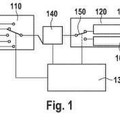

7. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde la estimación digital (X) se obtiene a partir de un segundo convertidor analógico-digital ADCtest conectado en paralelo al ADCUC.

8. Procedimiento de acuerdo con la reivindicación 7, donde el ciclo de conversión del ADCtest es controlado mediante un generador de número pseudoaleatorio.

9. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde el ADCUC es un sub-ADC de una de las etapas (STGi) de un ADC de tipo Pipeline, donde:

10. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde cada uno de los comparadores programables Compi comprende al menos un banco de transistores controlados por la señal Ki destinado a modificar la impedancia de al menos uno de los nudos internos de la arquitectura del comparador programable Compi.

11. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde cada uno de los comparadores programables Compi comprende adicionalmente al menos un banco de transistores controlados por la señal Ki conectado en paralelo a unos dispositivos de entrada de señales analógicas del Compi.

12. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde el ADCUC de tipo flash comprende un codificador termométrico-binario (TBC) sumador para la generación del código de salida c del ADCUC que determina un comportamiento monótono del ADCUC.

13. Procedimiento de acuerdo con cualquiera de las reivindicaciones 1-11, donde el ADCUC de tipo flash hace uso de un codificador termométrico-binario optimizado (O-TBC) que comprende;

14. Procedimiento de acuerdo con cualquiera de las reivindicaciones 1-11, donde el ADCUC de tipo flash usa un codificador termométrico-binario optimizado para la generación del código de salida c con reordenación de transiciones de comparadores tj y códigos de calibración Kj, que comprende una memoria

15. Unidad lógica (ULC) para la calibración concurrente del offset de los comparadores en un convertidor analógico-digital bajo calibración (ADCUC) según el procedimiento de la reivindicación 1, caracterizado porque comprende:

16. Unidad lógica de calibración (ULC) de acuerdo con la reivindicación 15, donde la variación de Kj se lleva a cabo mediante pasos constantes.

17. Unidad lógica de calibración (ULC) de acuerdo con cualquiera de las reivindicaciones 15-16, donde la habilitación del bloque de comparación (CB) y/o el bloque sumador/restador proviene de una señal ENABLE (EN) dependiente de la actualización del valor de la estimación de la transición Tj.

18. Unidad lógica de calibración (ULC) de acuerdo con cualquiera de las reivindicaciones 15-17, donde el dispositivo (PDM) para la estimación digital de transiciones (Ti) del ADCUC a partir de una salida digital (c) del ADCUC y de una estimación digital (X) de su entrada analógica (x) más precisa que dicha representación digital (c), a su vez comprende:

19. Unidad lógica de calibración (ULC) de acuerdo cualquiera la reivindicación-18, donde el aumento de Tj+1 y la disminución de Tj se llevan a cabo según pasos constantes.

20. Unidad lógica de calibración (ULC) de acuerdo con cualquiera de las reivindicaciones 16-19, donde los elementos a, b y c del dispositivo de estimación de transiciones (PDM) están adaptados para funcionar directamente con una estimación digital de la no-linealidad integral (INLj) según un cambio de variable dado por la ecuación INLj = Tj - Tj(ideal).

21. Unidad lógica de calibración (ULC) de acuerdo con cualquiera de las reivindicaciones 15-20, donde los elementos a, b, c y d están adaptados para funcionar con un código de calibración K'j según un cambio de variable dado por la ecuación, K'j = - Kj.

Patentes similares o relacionadas:

Compensación de deriva, del 20 de Noviembre de 2019, de Teledyne Signal Processing Devices Sweden AB: Un método asociado a un diseño de circuito eléctrico predefinido, en donde cada circuito eléctrico fabricado de acuerdo con el diseño de circuito […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal, del 1 de Agosto de 2013, de ROBERT BOSCH GMBH: Procedimiento para la corrección de un error de offset de un convertidor de señal , en donde elprocedimiento presenta los siguientes […]

Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal, del 1 de Agosto de 2013, de ROBERT BOSCH GMBH: Procedimiento para la corrección de un error de offset de un convertidor de señal , en donde elprocedimiento presenta los siguientes […]

PROCEDIMIENTO ADAPTATIVO PARA LA ESTIMACIÓN DE LA INL EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS), del 3 de Diciembre de 2012, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): Procedimiento adaptativo para la estimación de la INL en convertidores analógico-digitales (ADCs). Permite caracterizar y testar los convertidores analógico-digitales mediante […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

CIRCUITO MULTIPLICADOR DE UN UNICO BIT CON FUNCION DE AJUSTE DE FASE, del 8 de Abril de 2011, de OSAKI ELECTRIC CO., LTD: Circuito multiplicador de un único bit con función de ajuste de fase.Aumenta la resolución del ajuste de fase. Incluye un elemento aritmético […]

EMPAREJAMIENTO DINAMICO DE ELEMENTOS PARA CONVERTIDORES A/D., del 16 de Marzo de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON: Un método para un emparejamiento dinámico de elementos para un subconvertidor D/A de una etapa de convertidor A/D, caracterizado porque en ese dicho método se incluye el paso […]

SISTEMA DE GENERADOR CON PROCESAMIENTO INTELIGENTE DE SEÑAL DE POSICIÓN, del 30 de Noviembre de 2011, de VESTAS WIND SYSTEMS A/S: Sistema de generador de potencia eléctrica que incluye - un generador de potencia (GEN) que incluye un rotor impulsado por un árbol, - un procesador […]