CIRCUITO MULTIPLICADOR DE UN UNICO BIT CON FUNCION DE AJUSTE DE FASE.

Circuito multiplicador de un único bit con función de ajuste de fase.

Aumenta la resolución del ajuste de fase. Incluye un elemento aritmético de un bit 9 que multiplica señales de un bit dentro del cual las dos señales analógicas se convierten por un elemento de conversión {dl}{sg} 1, con una frecuencia de reloj del elemento aritmético de un bit que se fija a un múltiplo entero de la frecuencia de reloj del elemento de conversión {dl}{sg}, tiene dos elementos de almacenamiento multi-etapa 7 y 8 que almacenan respectivamente señales digitales de un bit, e introducen las salidas de multi-etapas almacenadas dentro del elemento aritmético de un bit, y un elemento de fijación del ajuste de fase 10 que fija las temporizaciones de salida de las dos salidas multi-etapa extraídas de los elementos de almacenamiento multi-etapa en diferentes puntos del tiempo dentro de un período de reloj del elemento de conversión {dl}{sg}; evitando aumentar su frecuencia

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200800485.

Solicitante: OSAKI ELECTRIC CO., LTD.

Nacionalidad solicitante: Japón.

Dirección: 2-7, HIGASHI-GOTANDA, 2 CHOME, SHINAGAWA-KU TOKYO 141-8646 JAPON.

Inventor/es: OHHIRA,TAKEO, AIKYO,YASUAKI, KAWASHIMA,NAOTO, GO,KAZUNORI.

Fecha de Solicitud: 21 de Febrero de 2008.

Fecha de Publicación: .

Fecha de Concesión: 29 de Marzo de 2011.

Clasificación Internacional de Patentes:

- H03K5/00 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › Manipulación de impulsos no cubiertos por ninguno de los otros grupos principales de la presente subclase (circuitos de realimentación H03K 3/00, H03K 4/00; utilizando dispositivos magnéticos o eléctricos no lineales H03K 3/45).

- H03M1/10 H03 […] › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 1/00 Conversión analógica/digital; Conversión digital/analógica (conversión de valores analógicos en, o a partir de una modulación diferencial H03M 3/00). › Calibración o ensayos.

- H03M7/30 H03M […] › H03M 7/00 Conversión de un código, en el cual la información está representada por una secuencia dada o por un número de dígitos, en un código en el cual la misma información está representada por una secuencia o por un número de dígitos diferentes. › Compresión (análisis-síntesis de la voz para reducción de redundancia G10L 19/00; para transmisión de imágenes H04N ); Expansión; Supresión de datos innecesarios, p. ej. reducción de redundancia.

Clasificación PCT:

- H03K5/00 H03K […] › Manipulación de impulsos no cubiertos por ninguno de los otros grupos principales de la presente subclase (circuitos de realimentación H03K 3/00, H03K 4/00; utilizando dispositivos magnéticos o eléctricos no lineales H03K 3/45).

- H03M1/10 H03M 1/00 […] › Calibración o ensayos.

- H03M7/32 H03M 7/00 […] › Conversión en, o a partir de una modulación delta, es decir, una modulación diferencial de un bit.

Fragmento de la descripción:

Circuito multiplicador de un único bit con función de ajuste de fase.

Antecedentes de la invención

La presente invención se refiere a un circuito multiplicador de un único bit con una función de ajuste de fase favorable como circuito aritmético de potencia.

Como se muestra en la Fig. 8, en un circuito aritmético de potencia configurado por un elemento detector de voltaje 101, un elemento detector de corriente 102, elemento de conversión A/D 103 y 104, y un elemento multiplicador 105, se necesita ajustar y corregir los errores de fase (de demora y adelanto) que se producen debido a las capacidades e inductores del elemento detector de voltaje 101 y el elemento detector de corriente 102 para realizar una operación aritmética precisa. Por lo tanto, se necesita realizar un ajuste de fase antes del envío al producto, y se proporcionan los elementos de ajuste de fase 106 y 107. La cantidad de ajuste de fase se obtiene a partir del resultado de una prueba. Para determinar la cantidad de ajuste de fase, se miden los errores de fase por una prueba para el caso de factores de potencia estimados de 1,0 y 0,5, y se determina la cantidad de ajuste de fase de acuerdo con la diferencia de los errores de fase.

Como elemento de ajuste de fase, generalmente se usa el mostrado en la Fig. 9. En la Fig. 9, la señal de salida del elemento de conversión A/D 103 de cualquier señal de la que se controla la fase, la señal X(n) o la señal Y(n), (X(n) en el ejemplo de la Fig. 9), se introduce en un registro de desplazamiento 108, y se obtiene cada señal de salida que está retrasada por un ciclo de reloj, y se saca una señal hacia el circuito de selección 109 que selecciona la señal de salida de acuerdo con la cantidad de retardo, esto es, la cantidad de ajuste de fase.

En este caso, la resolución para el ajuste de fase se determina por la frecuencia de muestreo del elemento de conversión A/D, y por lo tanto, la frecuencia de operación más baja del elemento de conversión A/D se determina de acuerdo con la resolución requerida.

No es deseable aumentar la frecuencia de funcionamiento del elemento de conversión A/D más de lo necesario para aumentar la resolución del ajuste desde el punto de vista de las características del elemento de conversión A/D que es un circuito analógico. Como idea en este caso, hay un método de tomar los datos de interpolación entre dos periodos de reloj por un circuito de cálculo del valor intermedio 110 como se muestra en la Fig. 10. Además, se realiza un método en el cual cualquier elemento de conversión A/D 103 ó 104 es capaz de realizar el proceso de conversión en el flanco de caída del reloj (normalmente los elementos de conversión A/D funcionan con el flanco de subida). De acuerdo con el método, la resolución es de un medio periodo de reloj.

Por otra parte, las técnicas de operar aritméticamente (sumando) los datos de un único bit convertidos de analógico a digital por un convertidor ΔΣ son ya conocidas por la Patente Japonesa Abierta a Inspección Pública Nº 2001-94430 (Documento de Patente 1) y la Patente Japonesa Abierta a Inspección Pública Nº 2005-142877 (Documento de Patente 2).

[Documento de Patente 1] Patente Japonesa Abierta a Inspección Pública Nº 2001-94430.

[Documento de Patente 2] Patente Japonesa Abierta a Inspección Pública Nº 2005-142877.

Sumario de la invención

Para evitar incrementar innecesariamente la frecuencia de funcionamiento del elemento de conversión A/D para obtener una resolución requerida por el ajuste de fase, la técnica anterior mostrada en la Fig. 10, en el caso de usar un convertidor de sobre muestreo tipo ΔΣ para el elemento de conversión A/D, no puede tomar una interpolación de los datos entre los dos ciclos de reloj con una señal de conversión de un bit ya que la señal de conversión es de un bit. La técnica anterior de tomar la fase de reloj de uno de los dos elementos de conversión A/D en un medio periodo no puede usarse cuando sólo un elemento de conversión A/D realiza el procesamiento a tiempo compartido. Específicamente, es difícil aplicar las técnicas anteriores descritas anteriormente a los circuitos de multiplicación de conversión de un único bit ΔΣ descritos en los Documentos de Patente 1 y 2.

Objeto de la presente invención

Un objeto de la presente invención es proporcionar un circuito de multiplicación de un único bit con una función de ajuste de fase capaz de mejorar la resolución del ajuste de fase sin incrementar la frecuencia de operación del elemento de conversión ΔΣ.

Para obtener el objeto descrito anteriormente, la presente invención es un circuito de multiplicación de un único bit que comprende un elemento aritmético de un único bit que multiplica señales digitales de un bit dentro del cual las dos señales analógicas se convierten respectivamente por un elemento de conversión ΔΣ, con una frecuencia de reloj del elemento aritmético de un único bit que se fija como un múltiplo entero de la frecuencia de reloj del elemento de conversión ΔΣ mencionado anteriormente, caracterizado porque tiene dos elementos de almacenamiento multi-etapa que almacenan respectivamente las señales digitales de un bit mencionadas anteriormente, y que introducen las salidas multi-etapas almacenadas en el elemento aritmético de un único bit mencionado anteriormente, y un elemento de fijación del ajuste de fase que fija las temporizaciones de salida de las dos salidas multi-etapa que salen desde los elementos de almacenamiento multi-etapa en diferentes puntos del tiempo dentro de un periodo de reloj del elemento de conversión ΔΣ mencionado anteriormente.

De acuerdo con la presente invención, la resolución del ajuste de fase puede mejorarse sin incrementar la frecuencia de operación del elemento de conversión ΔΣ.

Breve descripción de los dibujos

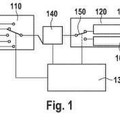

La Fig. 1 es un diagrama de circuito que muestra un circuito de multiplicación de un único bit con una función de ajuste de fase que es la realización 1 de la presente invención y sus circuitos periféricos;

La Fig. 2 es un diagrama que muestra la temporización del funcionamiento de cada parte en la realización 1;

La Fig. 3 es un diagrama que muestra una salida de multiplicación normal y en contraposición una salida de multiplicación de doble velocidad;

La Fig. 4 es un diagrama que muestra la salida de multiplicación de doble velocidad y en contraposición una salida de multiplicación de acuerdo con la realización 1;

La Fig. 5 es un diagrama que muestra un valor intermedio de valores de muestreo de una señal multi-bit;

La Fig. 6 es un diagrama de circuito que muestra un ejemplo en el que la realización 1 de la presente invención está conectada a dos elementos de conversión ΔΣ;

Las Fig. 7A y 7B son diagramas que muestran un elemento de fijación del ajuste de fase y sus temporizaciones de salida en la realización 2 de la presente invención;

La Fig. 8 es un diagrama de bloques que muestra un circuito aritmético de potencia ordinario;

La Fig. 9 es un diagrama que muestra un ejemplo de un elemento de ajuste de fase convencional; y

La Fig. 10 es un diagrama que muestra otro ejemplo del elemento de ajuste de fase convencional.

Descripción de Símbolos

Reivindicaciones:

1. Un circuito de multiplicación de un único bit con una función de ajuste de fase que comprende un elemento aritmético de un único bit que multiplica señales digitales de un bit dentro del cual dos señales analógicas se convierten respectivamente por un elemento de conversión ΔΣ, con una frecuencia de reloj del elemento aritmético de un único bit que se fija a un múltiplo entero de la frecuencia de reloj de dicho elemento de conversión ΔΣ,

en el que la mejora comprende dos elementos de almacenamiento multi-etapa que almacenan respectivamente dichas señales digitales de un bit, y que introduce las salidas multi-etapa almacenadas dentro de dicho elemento aritmético de un único bit, y un elemento de fijación de ajuste de fase que fija las temporizaciones de salida de las dos salidas multi-etapa extraídas desde los elementos de almacenamiento multi-etapa en diferentes puntos del tiempo dentro de un periodo de reloj de dicho elemento de conversión ΔΣ.

2. El circuito de multiplicación de un único bit con una función de ajuste de fase de acuerdo con la reivindicación 1,

en el que se procesan las señales digitales del elemento de conversión ΔΣ compartido por división en el tiempo para dichas dos señales analógicas.

3. El circuito de multiplicación de un único bit con una función de ajuste de fase de acuerdo con la reivindicación 1,

en el que se procesan las señales digitales de dos elementos convertidores ΔΣ que realizan individualmente operaciones de conversión A/D para dichas dos señales de entrada analógica.

4. El circuito de multiplicación de un único bit con una función de ajuste de fase de acuerdo con una cualquiera de las reivindicaciones de 1 a 3,

en el que la temporización de salida de uno de dichos elementos de almacenamiento multi-etapa se fija en la pendiente de subida del reloj de dicho elemento de conversión ΔΣ, y la temporización de salida del otro de dichos dos elementos de almacenamiento multi-etapa se fija en la pendiente de caída del reloj de dicho elemento de conversión ΔΣ.

5. El circuito de multiplicación de un único bit con una función de ajuste de fase de acuerdo con una cualquiera de las reivindicaciones de 1 a 3,

en el que las temporizaciones de salida de dichos dos elementos de almacenamiento multi-etapa se fijan de forma síncrona con un reloj de dicho elemento aritmético de un único bit.

Patentes similares o relacionadas:

Compensación de deriva, del 20 de Noviembre de 2019, de Teledyne Signal Processing Devices Sweden AB: Un método asociado a un diseño de circuito eléctrico predefinido, en donde cada circuito eléctrico fabricado de acuerdo con el diseño de circuito […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

Procedimiento y dispositivo para la conversión analógica-digital de señales, del 21 de Noviembre de 2013, de STAGE TEC ENTWICKLUNGSGESELLSCHAFT FUR PROFESSIONELLE AUDIOTECHNIK MBH: Procedimiento y dispositivo para la conversión analógica-digital de señales por medio de, como mínimo, dosconvertidores A/D (convertidores analógicos-digitales) […]

Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal, del 1 de Agosto de 2013, de ROBERT BOSCH GMBH: Procedimiento para la corrección de un error de offset de un convertidor de señal , en donde elprocedimiento presenta los siguientes […]

Procedimiento y dispositivo de corrección para la corrección de un error de offset de un convertidor de señal, del 1 de Agosto de 2013, de ROBERT BOSCH GMBH: Procedimiento para la corrección de un error de offset de un convertidor de señal , en donde elprocedimiento presenta los siguientes […]

PROCEDIMIENTO ADAPTATIVO DE CALIBRACIÓN DÍGITAL CONCURRENTE DEL OFFSET EN COMPARADORES EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS), del 18 de Diciembre de 2012, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): El objeto de la presente invención es un procedimiento adaptativo para la calibración del offset de comparadores en convertidores analógico-digitales […]

PROCEDIMIENTO ADAPTATIVO PARA LA ESTIMACIÓN DE LA INL EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS), del 3 de Diciembre de 2012, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): Procedimiento adaptativo para la estimación de la INL en convertidores analógico-digitales (ADCs). Permite caracterizar y testar los convertidores analógico-digitales mediante […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

EQUIPO DE DIAGNÓSTICO DE ALTAVOCES Y PROCEDIMIENTO DE UTILIZACIÓN DE ÉSTE MEDIANTE EL USO DE TRANSFORMADA WAVELET, del 24 de Julio de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Equipo de Diagnóstico de Altavoces y procedimiento de utilización de este mediante el uso de transformada Wavelet.

Técnica de detección de fallos o defectos debidos […]

EMPAREJAMIENTO DINAMICO DE ELEMENTOS PARA CONVERTIDORES A/D., del 16 de Marzo de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON: Un método para un emparejamiento dinámico de elementos para un subconvertidor D/A de una etapa de convertidor A/D, caracterizado porque en ese dicho método se incluye el paso […]

SISTEMA DE GENERADOR CON PROCESAMIENTO INTELIGENTE DE SEÑAL DE POSICIÓN, del 30 de Noviembre de 2011, de VESTAS WIND SYSTEMS A/S: Sistema de generador de potencia eléctrica que incluye - un generador de potencia (GEN) que incluye un rotor impulsado por un árbol, - un procesador […]