DISPOSITIVO HIBRIDO MODULAR PARA LA LECTURA DE MATRICES DE SENSORES DE IMAGEN.

Dispositivo híbrido modular para la lectura de matrices de sensores de imagen.

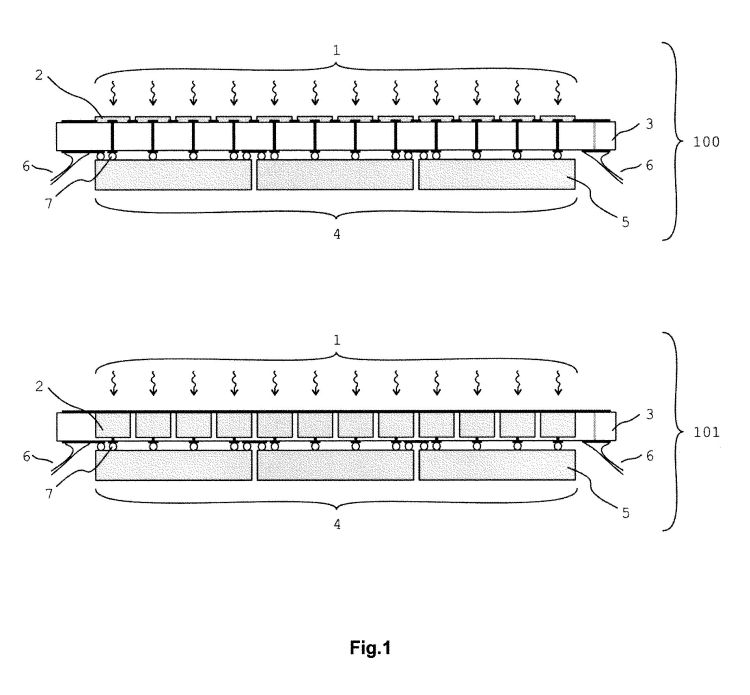

#La presente invención se refiere a circuitos integrados de lectura (ROICs) de matrices de sensores de imagen de plano focal. La invención introduce una nueva estrategia de encapsulado híbrido especialmente modular, ya que la matriz de lectura se construye mediante la interconexión de circuitos integrados idénticos e intercambiables entre sí formando un mosaico de la misma dimensión que el plano focal. La invención también plantea una organización de las conexiones del híbrido que permite independizar totalmente la tecnología de los sensores respecto a la tecnología de los circuitos de lectura. Como resultado, frente al estado del arte actual, la invención presenta la ventaja de que permite reducir los costes y aumentar el rendimiento de fabricación de la matriz lectora, permitir una mayor compatibilidad tecnológica entre sensores y circuitos, así como aumentar la flexibilidad en el escalado de las dimensiones delplano focal.

Tipo: Resumen de patente/invención.

Solicitante: CONSEJO SUPERIOR INVESTIGACIONES CIENTIFICAS.

Nacionalidad solicitante: España.

Provincia: MADRID.

Inventor/es: LOZANO FANTOBA,MANUEL, CABRUJA CASAS, ENRIC, SERRA GRAELLS,FRANCISCO, TERES TERES,LLUIS, BIGAS BACHS,MARC.

Fecha de Solicitud: 8 de Julio de 2005.

Fecha de Publicación: .

Fecha de Concesión: 24 de Noviembre de 2008.

Clasificación Internacional de Patentes:

- G11C7/10 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

- H01L27/14 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 27/00 Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00). › con componentes semiconductores sensibles a los rayos infrarrojos, a la luz, a la radiación electromagnética de ondas más cortas o a la radiación corpuscular, y adaptados para convertir la energía de tales radiaciones en energía eléctrica, o bien como dispositivos de control de la energía eléctrica por tales radiaciones (componentes sensibles a las radiaciones asociados estructuralmente a una o varias fuentes de luz eléctrica H01L 31/14; dispositivos de acoplamiento de guías de luz con elementos opto-electrónicos G02B 6/42).

- H04N5/335 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04N TRANSMISION DE IMAGENES, p. ej. TELEVISION. › H04N 5/00 Detalles de los sistemas de televisión (Detalles de los dispositivos de análisis o sus combinaciones con la producción de la tensión de alimentación H04N 3/00). › que utiliza sensores de imagen de estado sólido [SIES] (H04N 5/32, H04N 5/33 take precedence).

Clasificación PCT:

- G11C7/10 G11C 7/00 […] › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

- H01L27/14 H01L 27/00 […] › con componentes semiconductores sensibles a los rayos infrarrojos, a la luz, a la radiación electromagnética de ondas más cortas o a la radiación corpuscular, y adaptados para convertir la energía de tales radiaciones en energía eléctrica, o bien como dispositivos de control de la energía eléctrica por tales radiaciones (componentes sensibles a las radiaciones asociados estructuralmente a una o varias fuentes de luz eléctrica H01L 31/14; dispositivos de acoplamiento de guías de luz con elementos opto-electrónicos G02B 6/42).

- H04N5/335 H04N 5/00 […] › que utiliza sensores de imagen de estado sólido [SIES] (H04N 5/32, H04N 5/33 take precedence).

Patentes similares o relacionadas:

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Método de procesado de datos, aparato de almacenamiento, disco de estado sólido y sistema de almacenamiento, del 28 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesado de datos, aplicado a un sistema de almacenamiento, en donde el sistema de almacenamiento comprende un anfitrión, un controlador y un […]

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Circuitos de líneas de bits globales de Memoria Estática de Acceso Aleatorio (SRAM) para reducir los fallos de energía durante los accesos de lectura de memoria, y procedimientos y sistemas relacionados, del 17 de Abril de 2019, de QUALCOMM INCORPORATED: Un circuito de línea de bits global de memoria estática de acceso aleatorio, SRAM, para una pluralidad de células de bits de SRAM, que […]

Dispositivo de memoria híbrida con una única interfaz, del 23 de Enero de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento que comprende: recibir, en un controlador , órdenes, direcciones y datos en un dispositivo de memoria mediante una interfaz definida asociada […]

Dispositivo y procedimiento para el procesamiento de cuadros de datos en serie, del 11 de Octubre de 2018, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo para el procesamiento de cuadros de datos en serie, que comprende una unidad de convertidor en serie-paralelo , una unidad de evaluación […]

Arquitectura central en serie de memoria no volátil, del 3 de Septiembre de 2014, de Conversant Intellectual Property Management Inc: Sistema de memoria que comprende: banco de memoria para suministrar datos de lectura de flujo de bits en serie en respuesta a una operación […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme, del 16 de Julio de 2014, de Conversant Intellectual Property Management Inc: Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo […]