Procesador de imágenes para extracción de características.

La presente invención se refiere a un procesador de imágenes para la extracción de características que comprende un único chip no planar que contiene una pluralidad de sensores integrados y recursos de procesamiento distribuidos en dos o más capas adaptado a capturar cuadros de imágenes y extraer características de las imágenes.

En una realización particular, el chip no planar es un circuito integrado CMOS-3D (CI CMOS-3D) con una distribución vertical de los recursos de sensado y de procesado distribuidos en dos o más capas verticales de circuito integrado. El CI CMOS-3D implementa dos o más detectores de características en un único chip reutilizando una pluralidad de circuitos empleados para la obtención del gradiente y de puntos clave. Los detectores de características incluyen un detector invariante a transformaciones (SIFT), un detector de Harris y un detector basado en la matriz Hessiana.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201200090.

Solicitante: UNIVERSIDAD DE SANTIAGO DE COMPOSTELA.

Nacionalidad solicitante: España.

Inventor/es: RODRIGUEZ VAZQUEZ,ANGEL, BREA SÁNCHEZ,Victor Manuel, SUÁREZ CAMBRE,Manuel, PARDO SECO,Fernando Rafael, CARMONA GALÁN,Ricardo.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06T1/00 FISICA. › G06 CALCULO; CONTEO. › G06T TRATAMIENTO O GENERACIÓN DE DATOS DE IMAGEN, EN GENERAL. › Tratamiento de datos de imagen, de aplicación general.

Fragmento de la descripción:

Procesador de imágenes para extracción de características Sector de la Técnica Las realizaciones presentadas se refieren a procesadores de imágenes. Específi-camente, se refieren a procesadores para la adquisición de imágenes y detección de características

Antecedentes de la invención Los procesadores de imágenes convencionales siguen una estructura en la que operan cuadro a cuadro, es decir, primero se capturan los cuadros, posteriormente se codifican al dominio digital y finalmente se procesan. Esta aproximación se beneficia del enorme poder de cálculo de los procesadores digitales en tecnologías de alta integración, pero no es la aproximación más eficiente en términos de velocidad de procesado (tiempo transcurrido entre la entrada y las acciones) ni en términos de consumo de energía.

Los detectores de características invariantes a cambios de escala y rotación se emplean en distintas tareas de procesado de imágenes, como son la detección de objetos y su clasificación, recuperación de imágenes, registro de imágenes o tareas de seguimiento (tracking) . Su naturaleza invariante les confiere repetibilidad, lo que permite trabajar en ambientes con oclusión, o con escenas adquiridas bajo distintas condiciones, como iluminación o captura desde distintos ángulos de visión. Los de-tectores de características modernos invariantes a cambios de escala y rotación, como es el detector de características invariantes a transformaciones de escala, del inglés Scale Invariant Feature Transform (SIFT) , son técnicas de procesado de imágenes complejas con un elevado coste computacional, haciendo difícil su uso empleando procesadores de propósito general y software. Una parte importante de este algo-ritmo es la extracción de la pirámide Gaussiana, que comprende un conjunto de imágenes de diferentes resoluciones, denominadas octavas. Cada octava es el resul-tado de un escalado de 1/4 de la octava anterior. A su vez, cada octava está formada por una serie de imágenes llamadas escalas. Cada escala es el resultado de realizar un filtrado Gaussiano con un ancho dado (nivel-17) en la escala anterior.

En Harris and Stephens (Proc. Avley Vis. Conf., Manchester, pp. 147-152, 1998) se propuso un algoritmo para detectar características, cuya principal ventaja era que los cálculos involucrados en la obtención de las características de las imágenes, llamadas puntos de Harris, no requieren un tiempo de cómputo elevado. Sin embargo, ofrece unos resultados pobres cuando trabaja con cambios de escala y rotación en las imágenes.

El SIFT, presentado en la U.S. Pat. No. 6, 711, 293, es un algoritmo de procesado de imágenes que obtiene características invariantes a cambios de escala y rotación de imágenes digitales. Su principal limitación viene dada por el elevado coste compu-tacional del método, que dificulta su uso en aplicaciones que requieran operar en tiempo real (por ejemplo operar a una tasa de procesado de cuadros de 24 cuadro por segundo o más) .

Para evitar las limitaciones el algoritmo SIFT original, en Bonato et al., (IEEE Trans Circuits Syst., 18 (12) , pp. 1703-1712, 2008) se presenta una implementación sobre una FPGA, del inglés Field Programmable Gate Array. Sin embargo, la adqui-sición de las imágenes no está integrada con los elementos de procesamiento, lo que ralentiza el procesado. Además, el elevado consumo de potencia de las FPGAs hace que sea difícil integrarlas en un sistema de bajo consumo de potencia para tareas de visión por computador.

En Yao et al. (International Conference on Field-Programmable Technology, 2009. FPT 2009) se presenta otra implementación FPGA del algoritmo SIFT. í'umo en el caso de Bonato et al., la adquisición de la imagen no se ha tenido en cuenta a la hora de desarrollar el sistema.

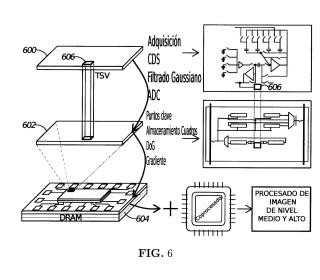

En Kiyoyama et al., (IEEE International Conference on 3D System Integration, 2009) se lleva a cabo el análisis del rendimiento de un circuito paralelo de procesado de señal, que incluye un circuito a nivel de píxel y un convertidor analógico digital (ADC) con muestreo doble correlacionado, del inglés correlated double sampling (CDS) , jerárquico. Este trabajo se centra en la adquisición de la imagen pero no trata el problema de la creación de un núcleo de procesado.Descripción de la invención Las realizaciones mostradas incluyen un procesador de imágenes para extracción de características que comprende un único chip no planar que contiene una plurali-dad de elementos de sensado y procesado distribuidos en dos o más capas adaptados a capturar cuadros de imágenes y extraer características de imágenes. De acuerdo a una realización particular, el chip no planar es un circuito integrado CMOS-3D con una distribución vertical de los elementos de sensado y de procesado a lo largo de dos o más circuitos integrales dispuestos verticalmente. En particular, el circuito integrado CM OS-3D implementa dos o más detectores de características en un único chip. En una realización, y sin limitar su alcance, estas características son invariantes a transformaciones (SIFT) , detector de puntos Harris y detector de características basado en la matriz Hessiana, o una combinación de todas ellas. En particular, el circuito integrado CMOS-3D implementa los detectores de características reutilizan-do una pluralidad de circuitos empleados para la obtención del gradiente y de los puntos clave (keypoints) . A modo de ejemplo, en una realización, el circuito integra-do implementa una arquitectura procesador-por-píxel para alcanzar un paralelismo masivo a nivel de píxel, e incluye un array de procesadores en píxel y una pluralidad de circuitos que en paralelo realizan el SIFT, detectan puntos de Harris, y puntos basado en la Hessiana. Ciertas realizaciones incluyen un red de capacidades en con-mutación (switched capacitar network) multipropósito. Esta red de capacidades en conmutación multipropósito implementa la generación de una pirámide Gaussiana, muestreo doble correlacionado (CDS) , y actúa como memoria analógica a nivel de píxel. Una realización particular de la red de capacidades en conmutación emplea una configuración doble Forward-Euler. De manera similar, el circuito integrado CMOS-3D incluye circuitos compartidos reutilizados para la conversión analógica-digital en píxel y el almacenamiento de los cuadros. En una realización particular, y sin limitar el alcance, los circuitos del circuito integrado se disponen en 4 capas con

(a) una capa para adquisición, muestreo doble correlacionado, filtrado Gaussiano y conversión analógica-digital; (b) un nivel para el almacenamiento de los cuadros, la detección de puntos clave, cálculo de differencia-de-Gaussianas (DoG) , cálculo de gradiente, y conversión analógica-digital compartida; y (e) dos niveles con memoria dinámica de acceso aleatorio, del inglés Dynamic Random Access Memor y (DRAM) . De igual manera, se muestra un método para obtener características de las imáge-nes de forma eficiente usando un circuito integrado. El método comprende: (a) im-plementar en un único chip no planar una pluralidad de elementos de sensado y procesado adaptados a la captura de imágenes y extracción de características y dis-tribuidos en dos o más capas; y (b) reutilizar la pluralidad de circuitos en el chip no planar para realizar un cálculo concurrente del gradiente y la detección de los puntos clave; y el muestreo doble correlacionado (CDS) y la conversión analógica-digital. En una realización particular, el chip no planar implementa dos o más detectores de características en un único chip. Por ejemplo, el detector de características puede ser un detector de características invariante a cambios de escala (SIFT) , un detector de puntos Harris, un detector de puntos dados por la matriz Hessiana, o una com-binación de todos ellos. En una realización particular, el procesador de imágenes descrito se puede usar como un procesador de visión CMOS-3D para ejecutar distintos detectores de ca-racterísticas.. El procesador de imágenes permite al usuario seleccionar el detector de características más apropiado de acuerdo a las necesidades de la aplicación. En una realización, el procesador de imágenes ejecuta dos modos principales: 1) Modo SIFT, proporcionando una alta precisión pero con el coste de una baja velocidad, y 2) Detectores de puntos Harris y basado en la matriz Hessiana, que son más veloces a costa de ofrecer una menor precisión. Esos dos modos son posibles gracias a: 1) la arquitectura CMOS-3D, y 2) el hecho de que ejecutar el SIFT implica ejecutar algunas de las operaciones requeridas para el detector de puntos Harris o detector basado en la matriz Hessiana. En concreto, la realización particular, y sin limitar el alcance, incluye una arquitectura de pixel con CDS a...

Reivindicaciones:

1. Un procesador de imágenes para detección de características que comprende un único chip no planar que contiene una pluralidad de elementos integrados de sensado y procesamiento distribuidos en dos o más capas adaptados para la captura de cuadros de imágenes y la extracción de características de imágenes.

2. El procesador de imágenes de la reivindicación 1, donde el chip no planar es un circuito integrado eMOS tridimensional con una distribución vertical del sensado y los elementos de procesamiento en dos o más capas de circuitos integrados.

3. El procesador de imágenes de la reivindicación 2, donde el circuito integrado CM OS tridimensional implementa dos o más detectores de característicl:lS en un único chip.

4. El procesador de imágenes de la reivindicación 3, donde Jos detectores de características son características invariantes a cambios de escala (81FT) , detectores de puntos Harris, detector basado de la matriz Hessiana, o una combinación de todos ellos.

5. El procesador de imágenes de la I"eivindicación 4, donde el circuito integrado CMOS tridimensional implementa dos o más detectores de características reutilizando una pluralidad de circuitos usados para la extracción del gradiente y puntos clave.

6. El procesador de imágenes de la reivindicación 5, donde el circuito integrado CM () S tridimensional implementa una arquitectura píxel-por-proccsador para obtener un paralelismo masivo a nivel de operación de píxel.

7. El procesador de imágenes de la reivindicación 6, donde el circuito integrado CMOS tridimensional comprende un array de procesadores en píxel y una pluralidad de circuitos que de forma paralela implementan los detectores de característica::; SIFT, detector de puntoo Harris, y detector de puntos basados en la matriz Hessiana.

8. El procesador de imágenes de la reivindicación 7, donde la pluralidad de circuitos incluye una red de capacidades en conmutación multipropósito.

9. El procesador de imágenes de la reivindicación 8, donde la red de capacidades en conmutación multipropósito implementa la generación de la pirámide Gaussiana, muestreo doble correLacionado (correlated double sampling, CDS) en píxel, y una memoria analógica a nivel de píxel.

10. El procesador de imágenes de la reivindicación 9, donde la red de capacidades en conmutación multipropósito presenta una configuración doble ForwardEuler.

11. El procesador de imágenes de la reivindicación 10, donde el circuito integrado CM OS tridimensional incluye la reutilización de circuitos compartidos para la conversión en píxel analógica-digital y el almacenamiento de cuadros.

12. El procesador de imágenes de la reivindicación 11, donde los circuitos del circuito integrado CMOS tridimensional están dispuestos en capas con (a) un nivel para la adquisición, COS, filtrado Gaussiano y conversión analógica-digital;

(b) un nivel para el almacenamiento de cuadros, extracción de puntos clave (keypoints) , cálculo de la diferencia de Gaussianas (Difference-of-Gaussian, DoG) , cálculo del gradiente y compartición de la conversión analógica-digital; y (c) dos niveles con memoria dinámica de acceso aleatorio, del inglés Dynamic Random Memor y Access (DRAM) .

13. Un método para extraer de forllla eficiente características de imágenes mediante un circuito integrado que comprende: (a) implementar un único chip no planar que contiene una pluralidad de elementos integrados de sensado y de procesamiento distri buidos en dos o más niveles adaptados a la captura de cuadros de imágenes y extracción de características de imágenes; y (b) reutilizar una pluralidad de circuitos en el chip no planar para obtener una implementación concurrente del cálculo del gradiente y de 108 puntos clave; CDS y conversión analógica-digita.L

14. El método de la reivindicación 13, donde el chip no planar implementa dos o más detectores de características en un único chip.

15. El método de la reivindicación 14., donde las características son características

invariantes a cambios de escala (SIFT) , detector de puntos de Harris, detector 5 basado en la Hessiana, o una combinación de todos ellos.

16. El método de la reivindicación 15, donde el circuito integrado CMOS tridimensional implementa un procesador por píxel para obtener un paralelismo de operación masivo a nivel de píxel; el circuito integrado CM OS tridimensional comprende un array de procesadores en píxel y una pluralidad de circuitos que realizan en paralelo el SIFT, detección de puntos Harris, detección de puntos basada en la Hessiana; la pluralidad de circuitos incluye una red de capacidades en conmutación multipropósito; la red de capacidades en conmutación multipropósito implementa la generación de la pirámide Gaussiana, el muestreo doble correlacionado (CDS) en píxel, y una memoria analógica a nivel de píxel; la red de capacidades en conmutación multipropósito tiene una configuración doble Forward-Eulerj el circuito integrado CMOS tridimensional incluye recursos compartidos para la conversión analógica-rligital en píxel y el almacenamiento de cuadros; los circuitos del circuito integrado CMOS tridimensional están dispuestos en cuatro capas con (a) un nivel para la adquisición, mues

treo doble correlacionado, filtrado Gaussiano y conversión analógica-digital;

(b) un nivel para el almacenamiento digital de cuadros, extracción de puntos clave, cálculo de la DoG, cálcuk d.el gradiente, y compartición de la conversión analógica-digital; y (e) dos niveles con memoria DRAM.

Patentes similares o relacionadas:

MÉTODO DE DETECCIÓN DE LÍNEAS DE TRANSMISIÓN DE ENERGÍA EN TIEMPO REAL CON VEHÍCULOS AÉREOS NO TRIPULADOS, del 25 de Junio de 2020, de PONTIFICIA UNIVERSIDAD JAVERIANA: La presente invención se refiere a un método para realizar la detección de líneas de transmisión de energía en una imagen capturada mediante una cámara […]

CONFIGURACIÓN Y VISUALIZACIÓN DE UNA INTERFAZ DE USUARIO CON ESTUDIOS DE ATENCIÓN SANITARIA, del 22 de Mayo de 2020, de FUJIFILM MEDICAL SYSTEMS USA INC: Configuración y visualización de una interfaz de usuario con estudios de atención sanitaria. Método y aparato para configurar y visualizar una interfaz de […]

Dispositivo y procedimiento de generación de imágenes de guía utilizando parámetros, del 13 de Mayo de 2020, de CJ CGV Co., Ltd: Un dispositivo de generación de imágenes de guía que comprende: una unidad de generación de imágenes de guía configurada para generar una imagen […]

Procedimiento y sistema para la calibración de un sistema de visión por ordenador, del 1 de Abril de 2020, de Oy Mapvision Ltd: Procedimiento para la calibración de un sistema de visión por ordenador tridimensional, comprendiendo dicho procedimiento las etapas de: disponer […]

Marcado remoto de pasaporte y documento de seguridad, del 29 de Enero de 2020, de SICPA HOLDING SA: Un sistema para marcar remotamente un documento de seguridad, tal como un pasaporte , con un correspondiente sello, etiqueta o visado virtual, que comprende: - una […]

Sistema y método de orientación automatizada para una máquina de movimientos coordinados, del 8 de Enero de 2020, de Recognition Robotics, Inc: Un método de orientación automatizada, que comprende: tomar una imagen inicial de una pluralidad de piezas de trabajo (Wa, Wb, Wc) de forma similar con una cámara […]

Imágenes en línea seguras, del 4 de Diciembre de 2019, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un dispositivo de generación de imágenes seguras para proteger una imagen , comprendiendo el dispositivo de generación de imágenes seguras: un […]

Método y aparato para comprobar neumáticos de rueda de vehículo, del 25 de Septiembre de 2019, de NEXION S.p.A: Un método para comprobar los neumáticos en las ruedas de un vehículo que comprende las etapas siguientes:

- cuando el vehículo está […]

Método y aparato para comprobar neumáticos de rueda de vehículo, del 25 de Septiembre de 2019, de NEXION S.p.A: Un método para comprobar los neumáticos en las ruedas de un vehículo que comprende las etapas siguientes:

- cuando el vehículo está […]