Método para fabricar un nanohilo monocristalino.

Método para fabricar una nanoestructura monocristalina que comprende las etapas de:

a) proporcionar una capa de dispositivo (21) con una orientación 100 sobre un sustrato;

b) proporcionar una capa de tensión (22) sobre la capa de dispositivo;

c) formar patrones (24) en la capa de tensión a lo largo de la dirección 110 de la capa dedispositivo;

d) retirar selectivamente partes de la capa de tensión (22) para obtener partes expuestas (31) de lacapa de dispositivo;

e) someter a ataque químico dependiente del plano las partes expuestas (31) de la capa dedispositivo para obtener unas caras 111 expuestas de la capa de dispositivo (41);

f) oxidar térmicamente la cara 111 expuesta de la capa de dispositivo (41) y formar una capa deoxidación lateral en una superficie de contacto de la capa de dispositivo y la capa de tensión;

g) proporcionar una capa de máscara sobre la cara 111 expuesta oxidada de la capa de dispositivo(51);

h) retirar las partes restantes de la capa de tensión (22) para obtener partes expuestas adicionalesde la capa de dispositivo;

i) retirar la capa de máscara;

j) someter a ataque químico dependiente del plano las partes expuestas adicionales de la capa dedispositivo para formar una nanoestructura monocristalina con una sección transversal de formatriangular, hasta que un lado (91) de la sección transversal de forma triangular que es coplanariocon una sección transversal de la cara 111 expuesta oxidada sea pequeño en comparación condicho lado (92) de la sección transversal de la cara 111 expuesta oxidada.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/NL2010/050512.

Solicitante: UNIVERSITEIT TWENTE.

Nacionalidad solicitante: Países Bajos.

Dirección: Drienerlolaan 5 7522 NB Enschede PAISES BAJOS.

Inventor/es: VAN DEN BERG, ALBERT, BOMER,JOHAN, CARLEN,EDWIN THOMAS, CHEN,SONGYUE, KRAAIJENHAGEN,RODERIK ADRIAAN, PINEDO,HERBERT MICHAEL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H01L21/306 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 21/00 Procedimientos o aparatos especialmente adaptados para la fabricación o el tratamiento de dispositivos semiconductores o de dispositivos de estado sólido, o bien de sus partes constitutivas. › Tratamiento químico o eléctrico, p. ej. grabación electrolítica (para formar capas aislantes H01L 21/31; postratamiento de capas aislantes H01L 21/3105).

- H01L21/308 H01L 21/00 […] › utilizando máscaras (H01L 21/3063, H01L 21/3065, tienen prioridad).

- H01L21/335 H01L 21/00 […] › Transistores de efecto de campo.

- H01L29/06 H01L […] › H01L 29/00 Dispositivos semiconductores adaptados a la rectificación, amplificación, generación de oscilaciones o a la conmutación que tienen al menos una barrera de potencial o de superficie; Condensadores o resistencias, que tienen al menos una barrera de potencial o de superficie, p. ej. unión PN, región de empobrecimiento, o región de concentración de portadores de carga; Detalles de cuerpos semiconductores o de sus electrodos (H01L 31/00 - H01L 47/00, H01L 51/05 tienen prioridad; otros detalles de los cuerpos semiconductores o de sus electrodos H01L 23/00; consistentes en una pluralidad de componentes de estado sólido formados en o sobre un sustrato común H01L 27/00). › caracterizados por su forma; caracterizado por las formas, las dimensiones relativas o las disposiciones de las regiones semiconductoras.

PDF original: ES-2426489_T3.pdf

Fragmento de la descripción:

Método para fabricar un nanohilo monocristalino.

Campo de la invención La invención se refiere a un método para fabricar un nanohilo monocristalino.

Antecedentes de la invención Durante la última década, ha existido un interés creciente en dispositivos a escala nanoscópica debido a su razón superficie-volumen grande y otras propiedades únicas. La fabricación de nanohilo de silicio se ha clasificado como o bien de abajo arriba o bien de arriba abajo. Los dispositivos de nanohilo de silicio realizados con técnicas de abajo arriba son de alta calidad y alto rendimiento, pero esta técnica carece de un método adecuado para definir posiciones de hilo y para formar contactos en ubicaciones específicas. Es difícil formar nanohilos de silicio en disposiciones de dispositivo funcionales. Por otro lado, la fabricación de nanohilo de silicio de arriba abajo usa técnicas convencionales para la fabricación de semiconductores. La formación de patrones a escala nanoscópica se hace normalmente con litografía de UV profundo o litografía de haz de electrones, seguido por ataque químico por iones reactivos o ataque químico anisotrópico en húmedo para transferir nanopatrones en obleas de silicio sobre aislante (SOI) . Sin embargo, hasta hace poco, estas técnicas no eran adecuadas para proporcionar planos bien definidos de nanohilos.

Se ha descrito un procedimiento de fabricación de nanohilo de silicio de arriba abajo por Hashigushi y Mimura (“Fabrication of Silicon Quantum Wires Using Separation by Implanted Oxygen Wager”, Jap. J. Appl. Phys. Vol 33, 1994) . En este documento se propone la combinación de técnicas de ataque químico anisotrópico y oxidación local de silicio. Las dimensiones de sección transversal triangular del nanohilo de silicio se determinan únicamente mediante el grosor de la capa de SOI usada. El documento describe que puede proporcionarse una capa de SOI con un grosor de 160 nm. Tras hacer crecer una capa de SiO2 de 250 nm de grosor por oxidación térmica, se obtuvo una capa de SOI más delgada de aproximadamente 50 nm retirando la capa de óxido. Se notificó la fabricación de hilos cuánticos de silicio con dimensiones de 50 nm.

Sin embargo, se desea la fabricación de nanohilos con dimensiones más pequeñas, puesto que los nanohilos más pequeños tendrán propiedades diferentes. Por ejemplo, se conoce que la sensibilidad de nanohilos de silicio frente al potencial superficial aumenta enormemente cuando se reduce su tamaño desde 200 nm hasta 50 nm y se espera que se reduzca aún más cuando se reducen adicionalmente las dimensiones del nanohilo. “Coulomb blockade oscillations at room temperature in a Si quantum wire metal-oxide-semiconductor field-effect transistor fabricated by anisotropic etching on a silicon-on-insulator substrate” Applied physics letters, AIP, American institute of physics, Melville, NY, Vol. 68, n.º 25, 17 de junio de 1996, páginas 3585 - 3587 da a conocer un procedimiento de fabricación de hilo cuántico MOSFET sobre un sustrato de separación por oxígeno implantado usando ataque químico anisotrópico y oxidación selectiva.

Sumario de la invención El objetivo de esta invención es proporcionar un método mejorado que permita la fabricación de una nanoestructura monocristalina. Para conseguir este objetivo se proporciona un método para fabricar una nanoestructura monocristalina, que comprende las siguientes etapas:

a) proporcionar una capa de dispositivo con una estructura 100 sobre un sustrato;

b) proporcionar una capa de tensión sobre la capa de dispositivo;

c) formar patrones en la capa de tensión a lo largo de la dirección 110 de la capa de dispositivo;

d) retirar selectivamente partes de la capa de tensión para obtener partes expuestas de la capa de dispositivo;

e) someter a ataque químico dependiente del plano las partes expuestas de la capa de dispositivo para obtener unas caras 111 expuestas de la capa de dispositivo;

f) oxidar térmicamente la cara 111 expuesta de la capa de dispositivo y formar una capa de oxidación lateral en una superficie de contacto de la capa de dispositivo y la capa de tensión;

g) proporcionar una capa de máscara sobre la cara 111 expuesta oxidada de la capa de dispositivo;

h) retirar las partes restantes de la capa de tensión para obtener partes expuestas adicionales de la capa de dispositivo;

i) retirar la capa de máscara;

j) someter a ataque químico dependiente del plano las partes expuestas adicionales de la capa de dispositivo para formar una nanoestructura monocristalina con una sección transversal de forma triangular, hasta que un lado de la sección transversal de forma triangular que es coplanario con un lado de una sección transversal de la cara 111 expuesta oxidada sea pequeño en comparación con dicho lado de la sección transversal de la cara 111 expuesta oxidada.

En primer lugar se proporciona una capa de dispositivo con una estructura 100 sobre un sustrato. En realizaciones del método según la invención esta capa de dispositivo puede comprender por ejemplo una oblea de silicio de tipo p 100 o una oblea de silicio de tipo n 100.

A continuación, se proporciona una capa de tensión sobre la capa de dispositivo. Una ventaja de la capa de tensión puede ser que impedirá la formación de dislocaciones en la capa de dispositivo debido a la tensión. Esta tensión se genera mediante la expansión volumétrica de una capa de óxido durante las etapas de oxidación térmica (véase a continuación) . En el caso de una capa de dispositivo de silicio, la capa de tensión puede comprender una capa de nitruro de silicio. Una ventaja del uso de una capa de nitruro de silicio es que el comportamiento de oxidación en la superficie de contacto de la capa de dispositivo de silicio y la capa de tensión de nitruro de silicio se entiende bien y puede reproducirse.

A continuación, se forman patrones en la capa de tensión a lo largo de la dirección 110 de la capa de dispositivo y se retiran selectivamente partes de la capa de tensión para obtener partes expuestas de la capa de dispositivo. La capa de tensión también puede actuar como máscara durante la etapa posterior de someter a ataque químico dependiente del plano las partes expuestas de la capa de dispositivo para obtener una cara 111 expuesta de la capa de dispositivo.

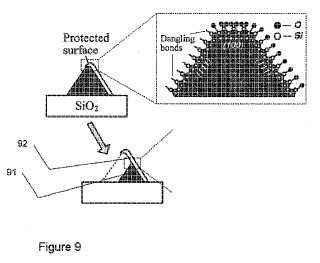

A continuación, se oxida térmicamente la cara 111 expuesta de la capa de dispositivo y se forma una capa de oxidación lateral en una superficie de contacto de la capa de dispositivo y la capa de tensión. Una ventaja de la cara 111 expuesta oxidada de la capa de dispositivo y la capa de oxidación lateral puede ser que forman una capa de protección para la nanoestructura durante una etapa posterior de ataque químico dependiente del plano.

Tras la oxidación, se proporciona una capa de máscara sobre la cara 111 expuesta oxidada de la capa de dispositivo. A continuación, se retiran las partes restantes de la capa de tensión para obtener partes expuestas adicionales de la capa de dispositivo y se retira la capa de máscara.

En la etapa siguiente, se lleva a cabo un ataque químico dependiente del plano de las partes expuestas adicionales de la capa de dispositivo para formar una nanoestructura monocristalina con una sección transversal de forma triangular. Esto procedimiento continúa hasta que un lado de la sección transversal de forma triangular que es coplanario con un lado de una sección transversal de la cara 111 expuesta oxidada sea pequeño en comparación con dicho lado de la sección transversal de la cara 111 expuesta oxidada.

Una ventaja de continuar el ataque químico dependiente del plano puede ser que permite una reducción de tamaño de la nanoestructura. En primer lugar se forma una nanoestructura monocristalina con una sección transversal de forma triangular con aproximadamente las mismas dimensiones que la cara 111 expuesta oxidada. Cuando se continúa el ataque químico dependiente del plano, el tamaño de la nanoestructura monocristalina se reduce adicionalmente en una ubicación rebajada entre la cara 111 expuesta oxidada y una capa sobre la que se proporciona la capa de dispositivo. En una realización, puede reducirse el tamaño hasta que el lado de la sección transversal de forma triangular que está contra un lado de una sección transversal de la cara 111 expuesta oxidada es más pequeño que la mitad del lado de la sección transversal de la cara 111 expuesta oxidada.

Una ventaja del método según la invención puede ser que permite la fabricación de nanoestructuras con dimensiones laterales de tan sólo 20 nm. El método puede aplicarse usando procedimientos de fabricación y fotolitografía a escala microscópica... [Seguir leyendo]

Reivindicaciones:

1. Método para fabricar una nanoestructura monocristalina que comprende las etapas de:

a) proporcionar una capa de dispositivo (21) con una orientación 100 sobre un sustrato;

b) proporcionar una capa de tensión (22) sobre la capa de dispositivo;

c) formar patrones (24) en la capa de tensión a lo largo de la dirección 110 de la capa de dispositivo;

d) retirar selectivamente partes de la capa de tensión (22) para obtener partes expuestas (31) de la capa de dispositivo;

e) someter a ataque químico dependiente del plano las partes expuestas (31) de la capa de dispositivo para obtener unas caras 111 expuestas de la capa de dispositivo (41) ;

f) oxidar térmicamente la cara 111 expuesta de la capa de dispositivo (41) y formar una capa de oxidación lateral en una superficie de contacto de la capa de dispositivo y la capa de tensión;

g) proporcionar una capa de máscara sobre la cara 111 expuesta oxidada de la capa de dispositivo (51) ;

h) retirar las partes restantes de la capa de tensión (22) para obtener partes expuestas adicionales de la capa de dispositivo;

i) retirar la capa de máscara;

j) someter a ataque químico dependiente del plano las partes expuestas adicionales de la capa de dispositivo para formar una nanoestructura monocristalina con una sección transversal de forma triangular, hasta que un lado (91) de la sección transversal de forma triangular que es coplanario con una sección transversal de la cara 111 expuesta oxidada sea pequeño en comparación con dicho lado (92) de la sección transversal de la cara 111 expuesta oxidada.

2. Método según la reivindicación 1, en el que el lado de la sección transversal de forma triangular que está contra un lado de una sección transversal de la cara 111 expuesta oxidada es más pequeño que la mitad del lado de la sección transversal de la cara 111 expuesta oxidada.

3. Método según una de las reivindicaciones 1-2, en el que la capa de dispositivo (21) comprende una oblea de silicio de tipo p 100 o una oblea de silicio de tipo n 100.

4. Método según una de las reivindicaciones 1-3, en el que un grosor de la capa de dispositivo proporcionada es superior a 50 nm, o está en el intervalo d.

20. 400 nm.

5. Método según una de las reivindicaciones 3-4, en el que la capa de tensión (22) comprende una capa de nitruro de silicio.

6. Método según una de las reivindicaciones 3-5, en el que un grosor de la capa de tensión (22) es inferior a 150 nm, o está en el intervalo d.

10. 40 nm, o es de aproximadamente 50 nm.

7. Método según una de las reivindicaciones 5-6, en el que la etapa b) comprende depositar la capa de nitruro de silicio por deposición química en fase de vapor a baja presión o por deposición química en fase de vapor potenciada por plasma.

8. Método según una de las reivindicaciones 1-7, en el que la etapa d) comprende retirar selectivamente partes de la capa de tensión (22) mediante ataque químico por iones reactivos.

9. Método según una de las reivindicaciones 3-8, en el que la etapa e) comprende usar una disolución de ataque químico de hidróxido de tetrametilamonio diluida o una disolución de ataque químico de hidróxido de potasio.

10. Método según una de las reivindicaciones 3-9, en el que la etapa g) comprende depositar una capa de silicio policristalino.

11. Método según una de las reivindicaciones 3-10, en el que la etapa h) comprende usar una disolución de ataque químico de ácido fosfórico a 60 grados Celsius.

12. Método según una de las reivindicaciones 3-11, en el que la etapa j) comprende usar una disolución de ataque químico de hidróxido de tetrametilamonio diluida o una disolución de ataque químico de hidróxido de potasio.

13. Método según una de las reivindicaciones 12-13, en el que la disolución de ataque químico tiene una temperatura de 180 grados Celsius.

14. Método según una de las reivindicaciones 1-14, que comprende además la etapa de

I) controlar una conductividad de capa de dispositivo, que comprende las etapas de 1) implantar iones antes de la etapa b) 2) efectuar un recocido térmico durante las etapas b) -k) 3) retirar una región de implantación de iones inicial durante la etapa k) .

15. Método según una de las reivindicaciones 1-15, que comprende además la etapa de m) que consiste en proporcionar un dieléctrico de puerta, que comprende las etapas de

1) proporcionar una capa de óxido sobre superficies 111 con un grosor de 10-20 nm 2) efectuar un recocido térmico en una atmósfera de N2.

16. Método según una de las reivindicaciones 1-16, que comprende además la etapa de n) proporcionar un contacto eléctrico que comprende las etapas de 1) retirar selectivamente partes de la capa de tensión para formar zonas de contacto

2) proporcionar una capa de metal en las zonas de contacto 3) efectuar un recocido térmico.

17. Método según la reivindicación 16, en el que las zonas de contacto se forman sobre partes de la capa de dispositivo, siendo las dimensiones de sección transversal de las mismas mayores que la sección transversal de forma triangular.

18. Método según la reivindicación 1, en el que la capa de dispositivo comprende una oblea de germanio de tipo p 100 o una oblea de germanio de tipo n 100.

Patentes similares o relacionadas:

PROCEDIMIENTO DE FABRICACIÓN DE CÉLULAS SOLARES EN OBLEAS DE GERMANIO, del 8 de Mayo de 2020, de UNIVERSIDAD POLITECNICA DE MADRID: Se describe un procedimiento de fabricación de células solares en obleas de germanio que comprende realizar un adelgazamiento de la cara trasera […]

Composición de microdecapado y método para usar la misma, del 18 de Diciembre de 2019, de MACDERMID, INCORPORATED: Una composición de microdecapado para tratar superficies metálicas que comprenden: a) una fuente de iones cúpricos; b) ácido, en donde el ácido […]

Composición para el tratamiento por grabado químico de un material de resina, del 26 de Junio de 2019, de OKUNO CHEMICAL INDUSTRIES CO., LTD: Composición para el tratamiento por grabado químico de un material de resina, comprendiendo la composición una solución acuosa que presenta […]

Composición acuosa alcalina de grabado y de limpieza y procedimiento de tratamiento de la superficie de sustratos de silicio, del 8 de Febrero de 2019, de BASF SE: Una composición acuosa alcalina de grabado y de limpieza que comprende: (A) al menos un hidróxido de amonio cuaternario; preferiblemente seleccionado […]

Método de texturización de las superficies de obleas de silicio, del 29 de Octubre de 2018, de UNIVERSITAT KONSTANZ: Método para la texturización de las superficies de obleas de silicio, que comprende las etapas de inmersión de la oblea de silicio en una solución […]

Composición para el tratamiento por grabado químico de un material de resina, del 8 de Octubre de 2018, de OKUNO CHEMICAL INDUSTRIES CO., LTD: Composición para el tratamiento por grabado químico de un material de resina, comprendiendo la composición una solución acuosa que presenta una concentración de ion […]

Pastas de grabado que contienen partículas para superficies y capas de silicio, del 26 de Noviembre de 2014, de MERCK PATENT GMBH: Procedimiento para el grabado de superficies y capas de silicio, o de superficies vítreas que consisten en un derivado de silicio, caracterizado […]

Procedimiento de grabado selectivo de silicio, del 4 de Junio de 2014, de SACHEM INC.: Procedimiento para grabar una capa de silicio dispuesta sobre un sustrato, que comprende:

grabar anisótropamente un primer surco en la capa de silicio;

realizar […]

Procedimiento de grabado selectivo de silicio, del 4 de Junio de 2014, de SACHEM INC.: Procedimiento para grabar una capa de silicio dispuesta sobre un sustrato, que comprende:

grabar anisótropamente un primer surco en la capa de silicio;

realizar […]