DISPOSITIVO DE MEMORIA Y MÉTODO PARA EL ACCESO ÓPTICO DE DATOS EN PARALELO.

Dispositivo de memoria y método para el acceso óptico de datos en paralelo.

Dispositivo de memoria de acceso de datos en paralelo y método para acceder en paralelo a los datos de dicho dispositivo de memoria. El dispositivo comprende: un módulo de almacenamiento que comprende: una variedad de segmentos de almacenamiento basados en tecnología de semiconductores; un receptor de datos del dispositivo de almacenamiento relacionado con cada segmento de almacenamiento; un emisor de datos del dispositivo de almacenamiento relacionado con cada segmento de almacenamiento; y una unidad de gestión del dispositivo de almacenamiento relacionada con cada segmento de almacenamiento para la gestión del segmento de almacenamiento, el receptor de datos del dispositivo de almacenamiento asociado y el emisor de datos del dispositivo de almacenamiento asociado; y un módulo de control que comprende: un receptor de datos del controlador relacionado con cada emisor de datos del almacén; un emisor de datos del controlador relacionado con cada receptor de datos del almacén; una unidad de gestión del controlador relacionada con los receptores de datos del controlador y con los emisores de datos del controlador para la gestión de los receptores de datos del controlador y los emisores de datos del controlador.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201030757.

Solicitante: UNIVERSITAT DE BARCELONA.

Nacionalidad solicitante: España.

Inventor/es: SANUY CHARLES,Andreu, DIEGUEZ BARRIENTOS,Angel, CASANOVA MOHR,Raimon, ARBAT CASAS,Anna.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C13/04 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 13/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento no cubiertos por los grupos G11C 11/00, G11C 23/00, ó G11C 25/00. › que utilizan elementos ópticos.

- G11C7/10 G11C […] › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

PDF original: ES-2370222_A1.pdf

Fragmento de la descripción:

Dispositivo de memoria y método para el acceso óptico de datos en paralelo.

La presente invención se refiere a un dispositivo de memoria para el acceso de datos en paralelo y con un método para el acceso en paralelo a los datos en dicho dispositivo de memoria. La invención también se refiere a un programa de ordenador para la aplicación de dicho método para acceder de forma paralela a los datos en dicho dispositivo de memoria.

Estado de la técnica

Existen diferentes medios y métodos para el almacenamiento de datos, por ejemplo en sistemas de computación. Dichos medios se pueden clasificar en dos categorías principales: almacenamiento masivo (por ejemplo, discos duros) y memorias (por ejemplo, RAM). Los dispositivos de almacenamiento masivo normalmente son dispositivos no volátiles externos con una capacidad de almacenamiento muy alta, pero con una baja velocidad de acceso a datos, mientras que las memorias pueden ser calificadas en general como dispositivos internos, que pueden ser volátiles o no volátiles, con una menor capacidad de almacenamiento pero con una mayor velocidad de acceso que las de los dispositivos de almacenamiento masivo.

Ambas categorías de medios para almacenar datos se basan en principios eléctricos, magnéticos y/o ópticos. De hecho, se han realizado inversiones muy cuantiosas para financiar la investigación sobre dichos principios físicos con el fin de producir memorias que ofrezcan las ventajas más apreciables de acuerdo a las aplicaciones que están destinadas. Los parámetros más relevantes tenidos en cuenta al evaluar las memorias son: velocidad, coste y densidad (tamaño frente a la capacidad).

En la actualidad, los tipos más extendidos de memorias en el mercado son las memorias estáticas de acceso aleatorio ("Static Random Access Memory", SRAM), las memorias dinámicas de acceso aleatorio ("Dynamic Random Access Memory", DRAM) y las memorias flash. Dichos tipos de memorias se basan en las características eléctricas de determinados materiales semiconductores, por lo que se suelen llamar memorias semiconductoras. En otras palabras, SRAM, DRAM y memorias flash utilizan circuitos integrados basados en semiconductores para almacenar datos. Un chip de memoria semiconductora normalmente contienen millones de pequeños transistores y condensadores.

Las memorias DRAM se llaman dinámicas porque el mantenimiento de los datos almacenados requiere revisar y volver a cargar dichos datos cada cierto periodo de tiempo en un ciclo refrescante, mientras que las memorias SRAM son capaces de mantener los datos almacenados sin necesidad de medidas refrescantes. Así, las memorias, tanto las DRAM como las SRAM son volátiles. Se considera que las memorias DRAM son más lentas que las SRAM, pero, por otra parte, las DRAM son más baratas y tienen mayor densidad que las SRAM.

Las memorias flash usan transistores basados en puertas flotantes de tal manera que la carga contenida (representando 0 o 1) se mantiene en el transistor durante un largo periodo de tiempo (10 años o más) incluso sin suministro eléctrico. Las memorias flash tienen la ventaja de ser no-volátiles y tienen una mayor densidad y son más baratas que las DRAM y SRAM, pero, por otra parte, las memorias flash son más lentas que las DRAM y SRAM. Es decir, el principal punto débil de las memorias flash en relación a las DRAM y SRAM es la velocidad de acceso a los datos.

Por otra parte, las memorias flash también tienen aplicaciones relevantes como dispositivos de almacenamiento masivo. Por ejemplo, existen discos de estado sólido que están totalmente basados en memorias flash y discos híbridos que están parcialmente basados en memorias flash. Un disco híbrido cuenta con un disco duro convencional y una memoria caché basada en tecnología de memoria Flash, dicha memoria caché está dedicada a almacenar datos que son accedidos continuamente. En comparación con los discos duros convencionales, los discos híbridos tienen la ventaja de aumentar la velocidad global de acceso a los datos y reducir el consumo de energía porque el disco duro convencional incluido en el disco híbrido puede parar sus motores cuando sólo se accede a los datos almacenados en la memoria caché.

Existen también tecnologías de memoria "emergentes" que están bastante menos extendidas que las comerciales memorias DRAM, SRAM y flash. El término "emergente" se utiliza en el sentido de que dichas tecnologías parecen ofrecer la posibilidad de producir memorias con altas prestaciones en el futuro pero no ahora, principalmente porque estas tecnologías no están todavía lo suficientemente maduras y/o es necesario aplicar nuevos procesos de producción muy caros para la producción de dichas memorias.

Una de dichas tecnologías de memoria "emergente" se refiere a memorias memorias ferroeléctricas de acceso aleatorio ("Ferroelectric Random Access Memory", FRAM). La FRAM es una memoria no volátil basada en el uso de sustancias ferroeléctricas que tienen un comportamiento dipolar (dos estados posibles) de manera que la aplicación de un campo eléctrico provoca que cambie el estado de la sustancia ferroeléctrica (lógicamente, de 0 a 1 o inversa). Las memorias FRAM ofrecen la misma funcionalidad que las memorias flash con más velocidad, pero tienen como desventajas densidades de almacenamiento mucho más bajas, una capacidad mucho menor y un mayor coste que las memorias Flash. Por lo tanto, es comúnmente aceptado que la tecnología FRAM debe seguir evolucionando para tomar el lugar de las memorias Flash en el mercado.

Otra tecnología de memoria "emergente" se refiere a memorias magnetoresistentes de acceso aleatorio ("Magnetoresistance Random Access Memory", MRAM). La MRAM es una memoria no volátil basada en una propiedad cuántica llamada "spin" de una sustancia ferromagnética, dicho "spin" puede tener dos valores posibles (arriba o abajo) de manera que la aplicación de un campo eléctrico hace que cambie el "spin" (lógicamente, de 0 a 1 o inversa). Se acepta generalmente que la velocidad de las memorias MRAM es equivalente a la velocidad de las memorias dinámicas más rápidas (DRAM, por ejemplo), pero las MRAM son más caras y tiene menor densidad que las DRAM, SRAM y memorias flash. Generalmente se supone que la tecnología MRAM no está suficientemente madura, ya que, por ejemplo, se requiere una corriente eléctrica muy alta para crear el campo magnético inducido para escribir en la memoria.

También ha habido intentos de diseñar memorias basadas en principios ópticos físicos. Por ejemplo, la patente europea EP0627116B1 revela una memoria óptica que permite la escritura y lectura en paralelo en varias células de memoria a la vez. Dicha memoria óptica comprende una pluralidad de células de memoria yuxtapuestas, cada una de las cuales cuenta con un soporte de almacenamiento para la recepción de un respectivo haz de luz. El punto de incidencia del haz de luz en la celda de memoria correspondiente sólo debe ser desplazado entre los puntos de memoria incluida precisamente en esta celda de memoria. La memoria óptica comprende además, medios de control eléctrico para lograr un desplazamiento constante y mutuamente igual de grande de el punto de incidencia de cada uno de los haces de luz de las células de memoria en el punto de la memoria correspondiente.

La memoria óptica descrita en EP0627116B1 requiere una gran precisión de los medios para desplazar el punto de incidencia del haz de luz correspondiente para que el haz de luz afecte únicamente punto de memoria apuntado (o correcto). Decir que sólo se puede lograr gran precisión, si es posible, a través de medios complejos y costosos para desplazar el punto de incidencia del haz de luz. Además, debe haber una distancia mínima entre los puntos de memoria para evitar que el haz de luz afecte a puntos de memoria incorrectos (por ejemplo, adyacente al punto de la memoria de destino), dicha distancia entre los puntos de la memoria implica menor densidad de los chips de memoria. Esto es lo mismo que decir que, a pesar de que dicha memoria óptica puede aumentar la velocidad de escritura/lectura de datos a través de escritura/lectura en paralelo de varias células de memoria a la vez, tiene los inconvenientes de ser más cara y menor densidad que las actualmente más extendidas memorias: DRAM, SRAM y memorias flash.

En conclusión, existen tecnologías de memoria alternativas (FRAM, y las memorias MRAM quizá óptica) que en un futuro pueden tomar el lugar de las memorias más extendidas en la actualidad (DRAM, SRAM y las memorias Flash), sobre todo porque se supone que dichas tecnologías... [Seguir leyendo]

Reivindicaciones:

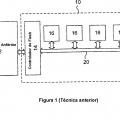

1. Dispositivo de memoria de acceso de datos en paralelo, que comprende: un módulo almacén (13) que comprende:

una variedad de segmentos de almacenamiento (16) basados en tecnología de semiconductores;

un receptor de datos del dispositivo de almacenamiento (17) relacionado con cada segmento de almacenamiento (16);

un emisor de datos del dispositivo de almacenamiento (22) relacionado con cada segmento de almacenamiento (16);

una unidad de gestión del dispositivo de almacenamiento (25) relacionada con el segmento de almacenamiento (16) para la gestión del segmento de almacenamiento (16), el receptor de datos del almacén asociado (17) y el correspondiente emisor de datos del dispositivo de almacenamiento (22);

un módulo de control (10) que comprende:

un receptor de datos del controlador (21) relacionado con cada uno de los emisores de datos del almacén;

un emisor de datos del controlador (15) relacionado con cada receptor de datos del almacén;

una unidad de gestión del controlador (11) relacionado con los receptores de datos del controlador (21) y los emisores de datos del controlador (15) para la gestión de los receptores de datos del controlador (21) y los emisores de datos del controlador (15).

2. Dispositivo de memoria según la reivindicación 1, donde la tecnología de semiconductores es semiconductor complementario de metal-óxido (CMOS).

3. Dispositivo de memoria según cualquiera de las reivindicaciones 1 ó 2, donde cada emisor de datos del controlador (15) es un emisor óptico y cada receptor de datos del dispositivo de almacenamiento (17) es un receptor óptico.

4. Dispositivo de memoria según cualquiera de las reivindicaciones 1 a 3, donde cada receptor de datos del controlador (21) es un receptor óptico y cada emisor de datos del dispositivo de almacenamiento (22) es un emisor óptico.

5. Dispositivo de memoria según cualquiera de las reivindicaciones 1 a 3, donde cada receptor de datos del controlador (21) es un receptor eléctrico y cada emisor de datos del dispositivo de almacenamiento (22) es un emisor eléctrico.

6. Dispositivo de memoria según cualquiera de las reivindicaciones 3 a 5, donde cada receptor óptico es una matriz que comprende al menos un receptor óptico.

7. Dispositivo de memoria según la reivindicación 6, donde por lo menos una unidad receptora óptica se compone de cuatro unidades de recepción ópticas.

8. Dispositivo de memoria según cualquiera de las reivindicaciones 6 ó 7, donde cada unidad recepción óptica es píxel con salida binaria semiconductor complementario de metal-óxido, estando dicho píxel CMOS integrado con su segmento de almacenamiento asociado basado en tecnología CMOS.

9. Dispositivo de memoria según la reivindicación 8, en el que cada píxel CMOS con salida binaria es un píxel CMOS con salida binaria sin realimentación y sin señal de reset.

10. Dispositivo de memoria según cualquiera de las reivindicaciones 8 o 9, donde cada píxel CMOS con salida binaria es un fotodiodo de avalancha.

11. Dispositivo de memoria según cualquiera de las reivindicaciones 3 a 10, en el cual cada emisor óptico es un emisor láser de superficie de cavidad vertical (VCSEL).

12. Dispositivo de memoria según las reivindicaciones 3 a 11, que además comprende un dieléctrico para enfocar la luz entre cada emisor óptico y su receptor óptico asociado.

13. Dispositivo de memoria según la reivindicación 12, donde el dieléctrico para enfocar la luz es el aire.

14. Dispositivo de memoria según cualquiera de las reivindicaciones 3 a 11, que comprende además una microlente para enfocar la luz dispuesta entre cada emisor óptico y su receptor óptico asociado.

15. Dispositivo de memoria según cualquiera de las reivindicaciones 3 a 11, que comprende además un trozo de fibra óptica para enfocarla luz dispuesta entre cada emisor óptico y su receptor óptico asociado.

16. Método para el acceso en paralelo a los datos en un dispositivo de memoria según cualquiera de las reivindicaciones 1 a 15, el método comprende:

recibir datos por parte de la unidad de gestión del controlador (901,101) datos sobre el acceso;

generar por parte de la unidad de gestión del controlador (902; 102) al menos una trama de control de los datos recibidos sobre el acceso,

representar por parte de cada trama de control el acceso a un segmento de almacenamiento de la memoria del dispositivo;

para cada trama de control que representa el acceso a un segmento de almacenamiento:

17. Método según la reivindicación 16, que comprende además:

emitir por parte de la unidad de gestión del dispositivo de almacenamiento relacionada con el segmento de almacenamiento (905, 105) una trama de control respuesta relacionada con la trama de control a través de su emisor de datos asociado.

18. Método según la reivindicación 14, que comprende además:

recibir por parte de la unidad de gestión del controlador (910, 110) la trama de control respuesta relacionada con la trama de control a través del receptor de datos del controlador relacionado con el segmento de almacenamiento;

verificar por parte de la unidad de gestión del controlador (911, 111) si la trama de control respuesta recibida comprende al menos un error acerca de la recepción de la trama de control;

en caso de resultado positivo:

19. Método según cualquiera de las reivindicaciones 16 a 18, donde acceso es acceso escritura y acceso al segmento de almacenamiento es escribir datos en el segmento de almacenamiento;

el método comprende además:

para cada trama de control que representa acceso escritura a un segmento de almacenamiento:

y en donde la unidad de gestión del dispositivo de almacenamiento relacionada con el segmento de almacenamiento que escribe datos en el segmento de almacenamiento según la trama de control comprende:

para cada trama de lectura relacionada con la trama de control:

20. Método según la reivindicación 19, que comprende además:

emitir por parte de la unidad de gestión del dispositivo de almacenamiento relacionada con el segmento de almacenamiento (918) una trama de lectura respuesta relacionada con la trama de escritura a través de su emisor de datos del dispositivo de almacenamiento asociado.

21. Método según la reivindicación 20, que comprende además:

recibir por parte de la unidad de gestión del controlador (922) la trama de escritura respuesta a través del receptor de datos del controlador relacionado con el segmento de almacenamiento;

verificar por parte la unidad de gestión del controlador (923) si la trama de escritura respuesta recibida contiene al menos un error acerca de la recepción de la de la trama de escritura;

en caso de resultado positivo:

transferir (921) el control del método la unidad de gestión del controlador que emite (915) la trama de escritura a través del emisor de datos del controlador relacionado con el segmento de almacenamiento.

22. Método según la reivindicación 16, donde el acceso es acceso lectura y acceder al segmento de almacenamiento es leer datos del segmento de almacenamiento;

y donde la unidad de gestión del dispositivo de almacenamiento relacionada con el segmento de almacenamiento que lee datos del segmento de almacenamiento según la trama de control comprende:

para cada lectura de datos de un segmento de almacenamiento representada en la trama de control:

23. Método según la reivindicación 22, que comprende además: recibir por parte de la unidad de gestión del controlador (117) la trama de lectura a través del receptor de datos del controlador relación con el segmento de almacenamiento;

emitir por parte de la unidad de gestión del controlador (118) una trama de lectura respuesta relacionada con la trama de lectura a través del emisor de datos del controlador relacionado con el segmento de almacenamiento.

24. Método según la reivindicación 23, que comprende además: recibir por parte de la unidad de gestión del dispositivo de almacenamiento relacionada con el segmento de almacenamiento (122) la trama de lectura respuesta a través del receptor de datos del dispositivo de almacenamiento relacionado con el segmento de almacenamien- to;

verificar por parte de la unidad de gestión del dispositivo de almacenamiento (123) si la trama de lectura respuesta comprende al menos un error acerca de la recepción de la trama de lectura;

en caso de resultado positivo:

transferir (121) el control del método a la unidad de gestión del dispositivo de almacenamiento relacionado con el segmento de almacenamiento que emite (116) la trama de lectura respuesta a través del emisor de datos del segmento del almacén relacionado con el segmento de almacenamiento.

25. Programa de ordenador que comprende instrucciones de programa para hacer que un ordenador lleve a cabo un método de acceso paralelo a los datos en un dispositivo de memoria según cualquiera de las reivindicaciones 1 a 15, el método según cualquiera de las reivindicaciones 16 a 24.

26. Programa de ordenador según la reivindicación 25, dentro de un medio de almacenamiento.

27. Programa de ordenador según la reivindicación 25, soportados en una señal portadora.

Patentes similares o relacionadas:

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Método de procesado de datos, aparato de almacenamiento, disco de estado sólido y sistema de almacenamiento, del 28 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesado de datos, aplicado a un sistema de almacenamiento, en donde el sistema de almacenamiento comprende un anfitrión, un controlador y un […]

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Circuitos de líneas de bits globales de Memoria Estática de Acceso Aleatorio (SRAM) para reducir los fallos de energía durante los accesos de lectura de memoria, y procedimientos y sistemas relacionados, del 17 de Abril de 2019, de QUALCOMM INCORPORATED: Un circuito de línea de bits global de memoria estática de acceso aleatorio, SRAM, para una pluralidad de células de bits de SRAM, que […]

Dispositivo de memoria híbrida con una única interfaz, del 23 de Enero de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento que comprende: recibir, en un controlador , órdenes, direcciones y datos en un dispositivo de memoria mediante una interfaz definida asociada […]

Dispositivo y procedimiento para el procesamiento de cuadros de datos en serie, del 11 de Octubre de 2018, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo para el procesamiento de cuadros de datos en serie, que comprende una unidad de convertidor en serie-paralelo , una unidad de evaluación […]

Arquitectura central en serie de memoria no volátil, del 3 de Septiembre de 2014, de Conversant Intellectual Property Management Inc: Sistema de memoria que comprende: banco de memoria para suministrar datos de lectura de flujo de bits en serie en respuesta a una operación […]

Esquema de control de sistema de memoria Flash, del 16 de Julio de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Método para programación en un sistema de memoria Flash que tiene una pluralidad de dispositivos de memoria Flash, comprendiendo el método:

recibir un […]

Esquema de control de sistema de memoria Flash, del 16 de Julio de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Método para programación en un sistema de memoria Flash que tiene una pluralidad de dispositivos de memoria Flash, comprendiendo el método:

recibir un […]