MICROPROCESADOR CON SELECCIÓN AUTOMÁTICA DE PARALELISMO SIMD.

Un procedimiento para controlar el paralelismo de operaciones en un procesador de datos en paralelo,

que comprende: monitorizar una o más condiciones en relación con el procesamiento llevado a cabo por el procesador de datos en paralelo; cuando la una o más condiciones monitorizadas se correspondan con un primer estado, ejecutar una o más instrucciones en paralelo en dos elementos de procesamiento en paralelo del procesador de datos en paralelo, proporcionando una ruta de datos con un primer ancho: y cuando la una o más condiciones monitorizadas se correspondan con un segundo estado, ejecutar una o más instrucciones en paralelo en el primero de los dos elementos de procesamiento en paralelo, de manera que se procesen los datos de un segundo ancho de banda menor que el primero, mientras que el segundo de los dos elementos de procesamiento en paralelo está inactivo; en el cual la monitorización comprende: monitorizar la temperatura del procesador de datos en paralelo, en el cual el primer estado está asociado con una temperatura monitorizada en, o por debajo de, un umbral de temperatura y el segundo estado está asociado con una temperatura por encima del umbral; y monitorizar una tarea llevada a cabo mediante la ejecución de la una o más instrucciones, en el cual en el primer estado la tarea solicita el procesamiento de datos del primer ancho a una frecuencia superior a un umbral de frecuencia establecido

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2006/020614.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE SAN DIEGO, CALIFORNIA 92121 ESTADOS UNIDOS DE AMERICA.

Inventor/es: DOCKSER,KENNETH,ALAN.

Fecha de Publicación: .

Fecha Solicitud PCT: 25 de Mayo de 2006.

Clasificación Internacional de Patentes:

- G06F1/20T

- G06F1/32P

- G06F9/318 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › con extensión o modificación de operaciones.

- G06F9/38E

- G06F9/38T

Clasificación PCT:

- G06F9/38 G06F 9/00 […] › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

PDF original: ES-2360816_T3.pdf

Fragmento de la descripción:

Campo de la técnica

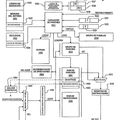

El presente objeto se refiere a técnicas y equipos para controlar automáticamente el estatus activo (activo e inactivo) de uno, o diversos, elementos procesadores de datos en paralelo, p. ej., de un procesador de Instrucción Única y Datos Múltiples (SIMD) o similar, para igualar el grado de paralelismo operativo con una condición en relación con las operaciones de procesamiento del procesador.

Antecedentes

Muchos dispositivos utilizan procesadores integrados, tales como microprocesadores y procesadores de señales digitales, con disposiciones complejas de lógica para llevar a cabo funciones de procesamiento de datos de acuerdo con instrucciones de programa. Las aplicaciones que precisan procesamiento digital de datos multimedia, tales como video, audio o gráficos, se están volviendo cada vez más populares entre los consumidores. Sin embargo, el procesamiento de tal información es intensivo y ha resultado en arquitecturas de procesadores que son particularmente adecuadas para tales datos.

Los datos multimedia típicamente incluyen una cantidad considerable de datos “en paralelo”. Los datos son “en paralelo” cuando las unidades individuales de datos no son dependientes entre sí. Por lo tanto, el procesamiento de una unidad de datos es independiente del procesamiento de otra unidad, esto es que no es necesario esperar a que el procesamiento de otra unidad sea completado. Como resultado, es posible efectuar al tiempo diversas de las mencionadas operaciones independientes de datos en paralelo. Esta característica de ciertos tipos de datos, particularmente las formas comunes de datos multimedia, ha llevado a la creación de procesadores en paralelo, que pueden manipular simultáneamente unidades de datos en paralelo. El procesamiento en paralelo de datos multimedia, por ejemplo, a menudo ayuda a aumentar sustancialmente la velocidad total de procesamiento.

Se han desarrollado diversas arquitecturas y tipos de instrucciones para el procesamiento de datos en paralelo, particularmente para aplicaciones multimedia. Por ejemplo, los procesadores de Instrucción Única y Datos Múltiples (SIMD) procesan datos en paralelo. El procesamiento multimedia usando instrucciones SIMD reduce el número total de instrucciones requeridas para ejecutar una tarea de programa particular y acelera la ejecución al operar sobre múltiples elementos de datos en paralelo. Aunque el procesador puede ejecutar una única corriente de instrucciones, la ejecución SIMD de tales instrucciones procesa concurrentemente múltiples corrientes de datos en paralelo.

Muchas aplicaciones de procesadores, incluyendo los dispositivos del tipo de elevado procesamiento de datos en paralelo como los procesadores SIMD, producen severas restricciones en la potencia y la energía que los circuitos del procesador pueden consumir. Por ejemplo, los dispositivos portátiles, como los teléfonos móviles, PDAs (asistentes digitales portátiles) y consolas de videojuegos de mano, utilizan baterías como suministro de energía. Sin embargo, estos dispositivos incluyen microprocesadores sofisticados y en algunos casos usan coprocesadores para el procesamiento relacionado con multimedia. Los diseños de procesadores para tales aplicaciones aseguran un cuidadoso control del consumo de potencia y energía, típicamente, para alargar la vida de carga en la batería de suministro de energía así como la vida del chip incluido.

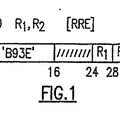

La arquitectura de un procesador establece un “ancho” de la ruta de datos a través del procesador, esto es el tamaño máximo de los datos que pueden ser procesados. Los diseños de procesamiento en paralelo, tales como las arquitecturas de procesadores SIMD, son típicamente escaladas para proporcionar un ancho de ruta de datos que se corresponda con la cantidad máxima de datos paralelos que el dispositivo puede procesar durante un ciclo dado. Los procesadores SIMD actuales disponibles pueden procesar hasta 128 bits de datos a un mismo tiempo, lo que significa que el ancho total de la ruta de datos es 128 bits. Sin embargo, en cualquier momento dado, las porciones paralelas del procesador pueden estar procesando unidades más pequeñas de datos.

Aunque se conocen otros tamaños, hoy en día los procesadores en paralelo comunes ofrecen una ruta de datos de 64 bits o un ancho de ruta de datos de 128 bits. La ruta de datos está construida por elementos de procesamiento en paralelo, aunque las rutas pueden estar configuradas para manejar datos de diferentes anchos. Por ejemplo, una ruta de datos de 128 bits puede ser fragmentada en pequeños tamaños, esto es que el procesador puede procesar secciones de los datos de 128 bits que tengan una longitud de 8 bits, 16 bits, 32 bits o 64 bits, según lo especificado por las instrucciones de SIMD escritas para la aplicación particular. Usando instrucciones de 8 bits, por ejemplo, un procesador con una ruta de datos con un ancho de 128 bits puede procesar dieciséis unidades de datos de 8 bits, en paralelo. Por el contrario, en la ruta de datos de 64 bits, si una instrucción requiere 128 bits, entonces los datos pueden ser divididos en dos secciones de 64 bits, y la instrucción es ejecutada secuencialmente en ambas secciones de 64 bits. Por supuesto, el procesamiento de cada sección de 64 bits puede entrañar procesamiento en paralelo, p. ej., de unidades de datos de 8 bits. Dividiendo el procesamiento de la instrucción de 128 bits, la ruta de datos con un ancho de 64 bits puede manejar la instrucción de 128 bits, aunque el tiempo para el procesamiento dividido es mayor.

Estas operaciones permiten una utilización óptima de los recursos en paralelo del procesador. Aún así, se presentan ocasiones en las que no son necesarios todos los recursos disponibles para aplicaciones de procesamiento particulares u ocasiones en las que puede ser deseable un funcionamiento completo. Por ejemplo, muchas funciones o aplicaciones del procesador simplemente no requieren la capacidad de procesamiento completa del dispositivo procesador o requieren la capacidad de procesamiento completa sólo por un periodo de tiempo muy limitado. En el ejemplo de procesador con ruta de datos de 128 bits, una aplicación o una porción de la misma puede requerir sólo un procesamiento de datos de 64 bits durante un/os periodo/s de tiempo, por ejemplo, porque existe una cantidad de paralelismo de datos limitada, la cantidad de datos a procesar es baja, o no existe una gran necesidad de velocidad. Sin embargo, si los elementos que proporcionan la ruta de datos de 128 bits son energizados por completo de manera continua, los elementos en paralelo no usados están consumiendo energía de manera innecesaria.

A modo de otro ejemplo, las operaciones de procesamiento completamente en paralelo implican una actividad intensa de todos los elementos en paralelo. Por lo tanto, todos los elementos en paralelo generan calor. Algunos diseños de procesador, por ejemplo los que están encapsulados en un paquete plástico para aplicaciones de bajo coste, pueden no ser capaces de soportar el calor por encima de determinadas temperaturas. Las operaciones a altas velocidades de manera continua de todo el conjunto de elementos en paralelo durante un periodo de tiempo extendido pueden generar demasiado calor.

Podría diseñarse un procesador en paralelo con un nivel de paralelismo más bajo de lo requerido para algunas aplicaciones, con el fin de que sea más eficiente para aplicaciones que no requieran un nivel elevado de paralelismo. Aunque estos compromisos pueden reducir el consumo de potencia y, por lo tanto, la generación de calor, resultan en energía gastada y un rendimiento bajo cuando se requiere más paralelismo.

Por lo tanto, existe la necesidad de una técnica para ajustar automáticamente el paralelismo de tal procesador en base a la tarea de procesamiento y/o a las condiciones ambientales.

El documento US2003/0088799 A1 da a conocer un sistema para la regulación de la temperatura de los componentes eléctricos y la tasa de consumo de potencia a través de la reconfiguración entre diferentes anchos de bus de interconexión.

El documento US2004/254965 A1 da a conocer una unidad computacional que comprende un procesador que tiene una pluralidad de elementos de procesamiento, cada uno de los mismos con una unidad de lógica aritmética, y un controlador para controlar los elementos de procesador. El procesador puede proporcionar un bit respectivo de una palabra de bits múltiples a cada uno de los elementos de procesador y permite transmitir señales entre las unidades lógicas aritméticas para permitir a las unidades ejecutar... [Seguir leyendo]

Reivindicaciones:

1. Un procedimiento para controlar el paralelismo de operaciones en un procesador de datos en paralelo, que comprende:

monitorizar una o más condiciones en relación con el procesamiento llevado a cabo por el procesador de datos en paralelo;

cuando la una o más condiciones monitorizadas se correspondan con un primer estado, ejecutar una o más instrucciones en paralelo en dos elementos de procesamiento en paralelo del procesador de datos en paralelo, proporcionando una ruta de datos con un primer ancho: y

cuando la una o más condiciones monitorizadas se correspondan con un segundo estado, ejecutar una o más instrucciones en paralelo en el primero de los dos elementos de procesamiento en paralelo, de manera que se procesen los datos de un segundo ancho de banda menor que el primero, mientras que el segundo de los dos elementos de procesamiento en paralelo está inactivo;

en el cual la monitorización comprende:

monitorizar la temperatura del procesador de datos en paralelo, en el cual el primer estado está asociado con una temperatura monitorizada en, o por debajo de, un umbral de temperatura y el segundo estado está asociado con una temperatura por encima del umbral; y

monitorizar una tarea llevada a cabo mediante la ejecución de la una o más instrucciones, en el cual en el primer estado la tarea solicita el procesamiento de datos del primer ancho a una frecuencia superior a un umbral de frecuencia establecido.

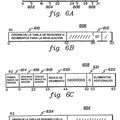

2. El procedimiento de la reivindicación 1, en el cual la ejecución de una o más instrucciones del primer elemento de procesamiento en paralelo, mientras el segundo de los dos elementos de procesamiento en paralelo está inactivo, comprende:

expandir una instrucción que solicita el procesamiento de datos en paralelo de los datos del primer ancho en una pluralidad de instrucciones que comprenden dos instrucciones que solicitan el procesamiento de datos en paralelo de los datos del segundo ancho; y

ejecutar las dos instrucciones secuencialmente en el primer elemento de procesamiento en paralelo.

3. El procedimiento de la reivindicación 2, en el cual:

ejecutar la una o más instrucciones de procesamiento en el elemento de procesamiento en paralelo proporciona un procesamiento de datos con un ancho de 64 bits en base a unas instrucciones ejecutadas; y

ejecutar la una o más instrucciones de procesamiento en el primer y el segundo elementos de procesamiento en paralelo proporciona el procesamiento de datos con un ancho de 128 bits en base a las instrucciones ejecutadas.

4. El procedimiento de la reivindicación 1, en el cual cada uno del primer y el segundo elementos de procesamiento en paralelo comprende una unidad de lógica aritmética.

5. El procedimiento de la reivindicación 4, en el cual la una o más instrucciones ejecutadas en el primero y segundo elementos de procesamiento son instrucciones de tipo Instrucción Única y Datos Múltiples (SIMD).

6. El procedimiento de la reivindicación 5, en el cual el primero y segundo elementos de procesamiento son elementos de un coprocesador SIMD.

7. El procedimiento de la reivindicación 1, en el cual ejecutar la una o más instrucciones en el elemento de procesamiento en paralelo comprende el procesamiento de datos multimedia.

8. El procedimiento de la reivindicación 1, en el cual

la potencia al segundo elemento de procesamiento en paralelo es cortada cuando el segundo elemento de procesamiento en paralelo está inactivo; o

una señal de reloj procedente del segundo elemento de procesamiento en paralelo es cortada cuando el segundo

11

elemento de procesamiento en paralelo está inactivo.

9. El procedimiento de la reivindicación 1 en el cual la monitorización de una tarea comprende determinar la frecuencia con la que las instrucciones solicitan el procesamiento de datos del primer ancho.

10. El procedimiento de la reivindicación 1, que comprende adicionalmente:

detectar una transición desde el primer estado hasta el segundo estado a partir de la monitorización de la condición,

desactivar el segundo elemento de procesamiento en paralelo, en respuesta a la transición detectada desde el primer estado al segundo estado;

detectar una transición desde el primer estado hasta el segundo estado a partir de la monitorización de la una o más condiciones; y

activar el segundo elemento de procesamiento en paralelo, en respuesta a la transición detectada desde el segundo estado al primer estado.

11. El procedimiento de la reivindicación 10, en el cual las etapas de activación y desactivación están adaptadas para mitigar la hiperpaginación potencial.

12. Un procesador de datos en paralelo (11), que comprende:

una lógica (27, 29, 31) configurada para monitorizar una o más condiciones en relación con el procesamiento llevado a cabo por el procesador de datos en paralelo;

un primer elemento de procesamiento (23) y un segundo elemento de procesamiento (25), estando el segundo elemento de procesamiento en paralelo conectado para operar en paralelo con el primer elemento de procesamiento, proporcionando la operación en paralelo del primer y segundo elementos de procesamiento un procesamiento de datos en paralelo con un primer ancho cuando la una o más condiciones monitorizadas se correspondan con un primer estado, en el cual el primer ancho es mayor que el segundo ancho;

un primer procesador en paralelo configurado para ejecutar una o más instrucciones con el fin de procesar datos de un segundo ancho menor que el primer ancho, mientras el segundo elemento de procesamiento en paralelo está inactivo, cuando la una o más condiciones monitorizadas se correspondan con un segundo estado; en el cual la lógica configurada para monitorizar comprende

un sensor de temperatura configurado para monitorizar la temperatura del procesador de datos en paralelo, en el cual el primer estado está asociado con una temperatura monitorizada que está en, o por debajo de, un umbral de temperatura y el segundo estado está asociado con una temperatura que está en, o por encima de, un umbral; y

una lógica configurada para monitorizar una tarea efectuada por ejecución de la una o más instrucciones, en el cual en el primer estado la tarea solicita un procesamiento de datos con el primer ancho a una frecuencia superior a una frecuencia diana establecida.

13. El procesador de datos en paralelo de la reivindicación 12, en el cual el primer y segundo elementos de procesamiento están configurados para procesar datos en respuesta a instrucciones del tipo Instrucción Única y Datos Múltiples (SIMD).

14. El procesador de datos en paralelo de la reivindicación 13, en el cual cada uno del primer y segundo elementos de procesamiento comprende una unidad de lógica aritmética de tipo SIMD.

15. El procesador de datos en paralelo de la reivindicación 12 ó 13, que comprende adicionalmente una etapa (17) de expansión de instrucciones, para convertir una instrucción SIMD que solicita que los datos del segundo ancho sean procesados para crear una pluralidad expandida de instrucciones SIMD que solicitan el procesamiento de los datos del primer ancho, estando la etapa de expansión de instrucciones configurada adicionalmente para suministrar secuencialmente la pluralidad expandida de instrucciones SIMD al primer elemento de procesamiento para su ejecución.

16. El procesador de datos en paralelo de la reivindicación 12, en el cual la lógica está adaptada para controlar la activación y desactivación del segundo elemento de procesamiento para mitigar la potencial hiperpaginación.

17. El procesador de datos en paralelo de la reivindicación 12, en el cual la lógica está adaptada para determinar si ya no queda por procesar ninguna instrucción de programa con el segundo ancho que esté en vuelo y, en respuesta, desactivar selectivamente el segundo elemento de procesamiento.

Patentes similares o relacionadas:

Microprocesador o microcontrolador potenciado, del 27 de Febrero de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un dispositivo de microprocesador de n bits que comprende: una unidad central de procesamiento de n bits (CPU); una pluralidad de registros […]

MECANISMO EN UN MICROPROCESADOR PARA EJECUTAR INSTRUCCIONES NATIVAS DIRECTAMENTE DESDE LA MEMORIA, del 13 de Enero de 2011, de IP-FIRST LLC: Un aparato en un microprocesador para ejecutar las instrucciones nativas que se proporcionan directamente al microprocesador a través de un canal principal […]

SISTEMA DE PROCESAMIENTO DE DATOS CON EJECUCION CONDICIONAL DE INSTRUCCIONES COMPUESTAS EXTENDIDAS., del 16 de Diciembre de 2004, de MOTOROLA, INC.: Un sistema para dar órdenes a un procesador de datos, el sistema incluye una raíz de instrucción que tiene un campo de selección de operación para seleccionar […]

SISTEMA INFORMATICO., del , de COMMUNICATE LTD.: EN UN SISTEMA DE ORDENADOR CON UN PROCESADOR RISC QUE UTILIZA INSTRUCCIONES DE 32 BITS, CIERTAS INSTRUCCIONES SE ALMACENAN EN FORMA COMPRIMIDA DE 16 BITS Y SE EXPANDEN […]

MICROPROCESADOR QUE UTILIZA UN CAMPO DE INSTRUCCION PARA ESPECIFICAR FUNCIONALIDAD EXTENDIDA, del 1 de Junio de 1999, de ADVANCED MICRO DEVICES INC.: SE DESCRIBE UN MICROPROCESADOR QUE EXPANDE LA FUNCIONALIDAD O RENDIMIENTO DE UNA ARQUITECTURA IMPLEMENTADA DE MANERA TRANSPARENTE O NO TRANSPARENTE. EL […]

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 23 de Octubre de 2009, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 23 de Octubre de 2009, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción […]

TRATAMIENTO DE INSTRUCCIONES DE RESUMEN DE MENSAJE, del 16 de Agosto de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para ejecutar una instrucción de resumen de mensaje en un sistema de ordenador, comprendiendo la instrucción de resumen de mensaje una función […]

TRATAMIENTO DE INSTRUCCIONES DE RESUMEN DE MENSAJE, del 16 de Agosto de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para ejecutar una instrucción de resumen de mensaje en un sistema de ordenador, comprendiendo la instrucción de resumen de mensaje una función […]