MICROPROCESADOR QUE UTILIZA UN CAMPO DE INSTRUCCION PARA ESPECIFICAR FUNCIONALIDAD EXTENDIDA.

SE DESCRIBE UN MICROPROCESADOR QUE EXPANDE LA FUNCIONALIDAD O RENDIMIENTO DE UNA ARQUITECTURA IMPLEMENTADA DE MANERA TRANSPARENTE O NO TRANSPARENTE.

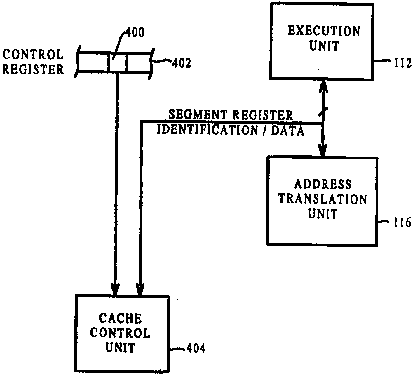

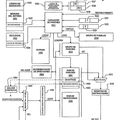

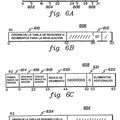

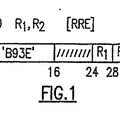

EL MICROPROCESADOR ESTA CONFIGURADO PARA DETECTAR LA PRESENCIA DE PREFIJOS DE PRIORIDAD DE SEGMENTOS EN SECUENCIAS DE CODIGO DE INSTRUCCIONES QUE SE EJECUTAN EN UN MODO DE MEMORIA PLANA Y USAR EL VALOR DEL PREFIJO PARA CONTROLAR FUNCIONES INTERNAS O EXTERNAS. ADICIONALMENTE, EL MICROPROCESADOR SE PUEDE CONFIGURAR PARA INDICAR UN CAMBIO O MODIFICACION DE LA EJECUCION NORMAL DE LAS INSTRUCCIONES QUE SIGUEN. SE MUESTRAN MUCHAS REALIZACIONES QUE USAN PREFIJOS DE PRIORIDAD DE SEGMENTO PARA EXPANDIR EL RENDIMIENTO O CAPACIDAD DEL MICROPROCESADOR. SE PUEDE MANTENER COMPATIBILIDAD HACIA ATRAS CON IMPLEMENTACIONES MAS ANTIGUAS QUE LA ARQUITECTURA X86 CUANDO SE IMPLEMENTAN REALIZACIONES TRANSPARENTES.

Tipo: Resumen de patente/invención.

Solicitante: ADVANCED MICRO DEVICES INC..

Nacionalidad solicitante: Estados Unidos de América.

Dirección: ONE AMD PLACE, MAIL STOP 68,SUNNYVALE, CALIFORNIA 94088-34.

Inventor/es: DUTTON, DREW, J., CHRISTIE, DAVID, S.

Fecha de Publicación: .

Fecha Solicitud PCT: 7 de Junio de 1996.

Fecha Concesión Europea: 31 de Marzo de 1999.

Clasificación Internacional de Patentes:

- G06F9/318 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › con extensión o modificación de operaciones.

Países PCT: Alemania, España, Francia, Reino Unido, Oficina Europea de Patentes.

Patentes similares o relacionadas:

Microprocesador o microcontrolador potenciado, del 27 de Febrero de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un dispositivo de microprocesador de n bits que comprende: una unidad central de procesamiento de n bits (CPU); una pluralidad de registros […]

MICROPROCESADOR CON SELECCIÓN AUTOMÁTICA DE PARALELISMO SIMD, del 9 de Junio de 2011, de QUALCOMM INCORPORATED: Un procedimiento para controlar el paralelismo de operaciones en un procesador de datos en paralelo, que comprende: monitorizar una o más condiciones […]

MECANISMO EN UN MICROPROCESADOR PARA EJECUTAR INSTRUCCIONES NATIVAS DIRECTAMENTE DESDE LA MEMORIA, del 13 de Enero de 2011, de IP-FIRST LLC: Un aparato en un microprocesador para ejecutar las instrucciones nativas que se proporcionan directamente al microprocesador a través de un canal principal […]

SISTEMA DE PROCESAMIENTO DE DATOS CON EJECUCION CONDICIONAL DE INSTRUCCIONES COMPUESTAS EXTENDIDAS., del 16 de Diciembre de 2004, de MOTOROLA, INC.: Un sistema para dar órdenes a un procesador de datos, el sistema incluye una raíz de instrucción que tiene un campo de selección de operación para seleccionar […]

SISTEMA INFORMATICO., del , de COMMUNICATE LTD.: EN UN SISTEMA DE ORDENADOR CON UN PROCESADOR RISC QUE UTILIZA INSTRUCCIONES DE 32 BITS, CIERTAS INSTRUCCIONES SE ALMACENAN EN FORMA COMPRIMIDA DE 16 BITS Y SE EXPANDEN […]

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 23 de Octubre de 2009, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 23 de Octubre de 2009, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción […]

TRATAMIENTO DE INSTRUCCIONES DE RESUMEN DE MENSAJE, del 16 de Agosto de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para ejecutar una instrucción de resumen de mensaje en un sistema de ordenador, comprendiendo la instrucción de resumen de mensaje una función […]

TRATAMIENTO DE INSTRUCCIONES DE RESUMEN DE MENSAJE, del 16 de Agosto de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para ejecutar una instrucción de resumen de mensaje en un sistema de ordenador, comprendiendo la instrucción de resumen de mensaje una función […]