DISPOSITIVO DE CONTROL DE LA TENSION DE POLARIZACION DE UN MODULO ELECTRONICO FUNCIONAL.

Dispositivo de control de la tensión de polarización de un módulo electrónico funcional.

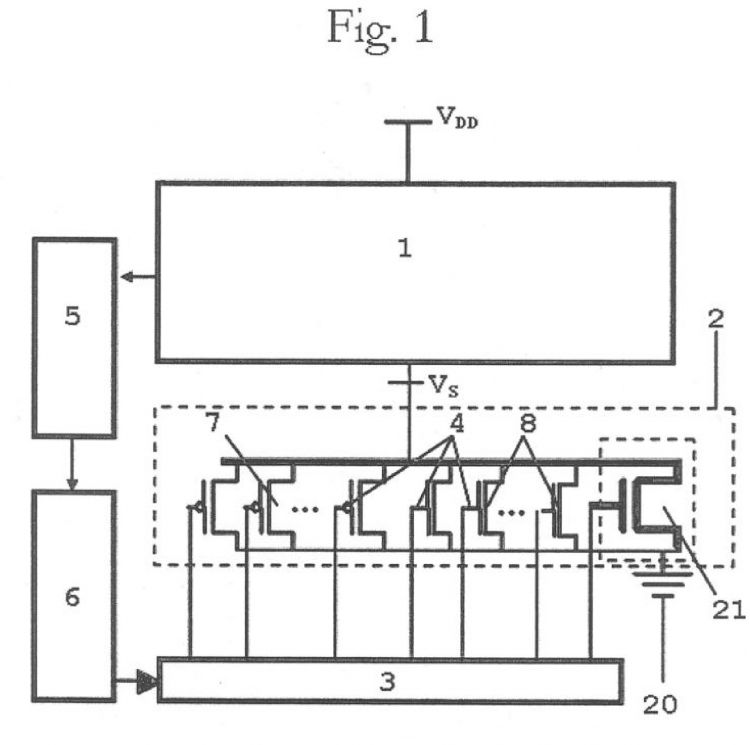

Dispositivo de control de la tensión de polarización (VDD-VS) para minimizar la potencia consumida por un módulo electrónico funcional (1) garantizando la retención de memoria, que comprende un conjunto de transistores (2) conectado en serie, un registro de control digital (3) que actúa sobre ellos mediante el control de su tensión de puerta (4), una unidad de medida (5) de la corriente de fuga y una unidad de control (3) que a partir de las señales de medida generadas por la unidad de medida (5) genera los valores digitales del registro de control para que la intersección entre la curva de carga del módulo y la curva de transferencia del conjunto de transistores se sitúa en la mínima corriente de fuga que mantiene la tensión de polarización (VDD-VS) por encima de una mínima tensión de polarización (U)

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200702180.

Solicitante: UNIVERSITAT POLITECNICA DE CATALUNYA.

Nacionalidad solicitante: España.

Provincia: BARCELONA.

Inventor/es: FERRE FABREGAS,ANTONI, FIGUERAS PAMIES,JOAN, BALADO SUAREZ,LUZ, SANAHUJA MOLINER,RICARD.

Fecha de Solicitud: 30 de Julio de 2007.

Fecha de Publicación: .

Fecha de Concesión: 26 de Agosto de 2010.

Clasificación Internacional de Patentes:

- G11C5/14R

Clasificación PCT:

- G11C5/14 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 5/00 Detalles de memorias cubiertos por el grupo G11C 11/00. › Disposiciones para la alimentación.

Fragmento de la descripción:

Dispositivo de control de la tensión de polarización de un módulo electrónico funcional.

La invención se refiere a un dispositivo de control de la tensión de polarización de un módulo electrónico funcional que permite reducir al mínimo las pérdidas energéticas provocadas por las corrientes de fuga.

Antecedentes de la invención

Un módulo electrónico funcional que precisa una tensión de polarización para funcionar está sujeto, por la naturaleza de sus componentes, a unas corrientes de fuga que dependen de dicha polarización.

Dicha tensión de polarización es la diferencia de potencial entre la tensión de alimentación (VDD) y la masa (VS).

En general, a mayor polarización, mayores corrientes de fuga, según las leyes aplicables a los componentes que componen estos módulos, y por lo tanto mayores pérdidas energéticas.

Por otro lado, para asegurar la retención de memoria de estos módulos, es preciso aplicar a sus terminales una tensión mínima, en general menor que la tensión de alimentación VDD.

Por ello, los sistemas que mantienen fija la polarización implican unas corrientes de fuga no óptimas.

A tal efecto, en el estado de la técnica se contemplan como soluciones, entre otras, el control de la tensión de alimentación VDD o el control de la tensión del sustrato.

Otra solución es interponer, entre el módulo y la masa, un conjunto de transistores, de modo que se establece un punto de funcionamiento que es la intersección de la curva de carga del módulo y la curva característica de un conjunto de transistores, lo cual permite limitar la tensión de polarización. De esta manera, dicha conexión (VS) pasa a ser una masa virtual cuya tensión se puede modificar.

Una solución de este tipo, que se divulga en el documento "Locally Switched and Limited Source-Body Bias and Other Leakage Reduction Techniques for a Low-Power Embedded SRAM", S. Cserveny, et al., Trans. CAS-II, vol. 52, num. 10, páginas 636-640, consiste en interponer entre VS y la masa un pMOS y un nMOS, ambos dispuestos en paralelo, de manera que definen una carga que, en combinación con el módulo, permite ajustar el punto de funcionamiento del módulo, disminuyendo la tensión de polarización y, por lo tanto, la corriente de fuga y la potencia energética consumida.

Esta solución, que se considera como antecedente más directo, permite una reducción de las corrientes de fuga, pero, sin embargo, como la curva característica resultante de asociar dichos transistores en paralelo es fija, no permite adaptar VS a la tensión máxima que permite retener la memoria y minimizar las corrientes de fuga.

Por lo tanto, es evidente la necesidad de disponer de un sistema de control de la tensión VS de un módulo funcional, es decir de la tensión de polarización, que haga esta mínima para reducir al máximo las corrientes de fuga, pero que garantice esta sea suficiente para asegurar el funcionamiento de esta unidad funcional.

Descripción de la invención

Con esta finalidad, la presente invención propone un sistema de control de la tensión de polarización adaptativo que resuelve el inconveniente mencionado, presentando otras características ventajosas que se describirán a continuación.

La invención es un dispositivo de control de la tensión de polarización (VDD-VS) de un módulo electrónico funcional conectado entre un terminal de alimentación y la masa, que tiene una curva de carga y una mínima tensión de polarización de retención de memoria, y se caracteriza por el hecho de que comprende:

de modo que los valores digitales del registro de control son generados para que el punto de funcionamiento resultado de la intersección entre la curva de carga y la curva característica de transferencia se sitúe en la mínima corriente de fuga que mantenga la tensión de polarización por encima de la mínima tensión de polarización.

Con estos elementos dispuestos con la estructura descrita se dispone de un sistema de control adaptativo que responde a las variaciones del estado de funcionamiento del módulo, de manera que se garantiza permanentemente la retención de memoria y se disminuye al máximo la corriente de fuga, y consecuentemente, las pérdidas de potencia eléctrica.

Preferentemente, el conjunto de transistores comprende dos o más transistores nMOS y dos o más transistores pMOS, de manera que se pueden obtener, mediante la combinación de estados de los transistores, varias curvas características diferentes.

Ventajosamente, el conjunto de transistores comprende el mismo número de transistores nMOS que de transistores pMOS y aún más preferentemente, 4 transistores nMOS y 4 transistores pMOS, cantidades suficientes para disponer de suficientes curvas características para obtener una tensión de polarización óptima.

Más preferentemente, los transistores pMOS están dispuestos con el sustrato conectado a (VS) y los transistores nMOS están dispuestos con el sustrato conectado a masa, de manera que las curvas características de dichos componentes se adaptan a las necesidades de control de la invención.

Finalmente, el conjunto de transistores comprende un interruptor de by-pass dispuesto en paralelo con los transistores controlado por dicho registro de control digital que permite conectar directamente el terminal VS a masa.

Breve descripción de los dibujos

Para mejor comprensión de cuanto se ha expuesto se acompañan unos dibujos en los que, esquemáticamente y tan sólo a título de ejemplo no limitativo, se representan unos casos prácticos de realización.

La figura 1 es un diagrama de bloques funcionales de la invención.

La figura 2 representa las curvas características del módulo electrónico funcional y del conjunto de transistores en función de la tensión de masa virtual VS.

La figura 3 es un diagrama de bloques funcionales de la invención según una realización preferida que comprende 4 transistores pMOS y 4 transistores nMOS.

La figura 4 es un gráfico en el que se representan las curvas características de un módulo electrónico funcional y del conjunto de transistores de la realización de la figura 3.

La figura 5 es una ampliación del gráfico de la figura 4 correspondiente a la zona de bajos valores de VS.

Descripción de realizaciones preferidas

Según una realización preferida de la invención y tal como se ilustra en la figura 1, el dispositivo de control de la tensión de polarización VDD-VS de un módulo electrónico funcional 1 de la invención comprende:

El dispositivo de control de la tensión de polarización VDD-VS del módulo electrónico funcional 1 controla la tensión VS utilizando una combinación de transistores pMOS 7 y nMOS 8 dispuestos en paralelo que se pueden controlar digitalmente por su tensión...

Reivindicaciones:

1. Dispositivo de control de la tensión de polarización (VDD-VS) de un módulo electrónico funcional (1) conectado entre un terminal de alimentación (VDD) y la masa (20), teniendo dicho módulo electrónico funcional (1) una curva de carga y una mínima tensión de polarización de retención de memoria, caracterizado por el hecho de que comprende:

2. Dispositivo según la reivindicación 1, caracterizado por el hecho de que dicho conjunto de transistores (2) comprende dos o más transistores nMOS (7) y dos o más transistores pMOS (8).

3. Dispositivo según la reivindicación 2, caracterizado por el hecho de que dicho conjunto (2) comprende tantos transistores nMOS (7) como transistores pMOS (8).

4. Dispositivo según la reivindicación 1, caracterizado por el hecho de que dicho conjunto (2) comprende 4 transistores nMOS (7) y 4 transistores pMOS (8).

5. Dispositivo según la reivindicación 2, caracterizado por el hecho de que los transistores pMOS están dispuestos con el sustrato conectado a (VS) y los transistores nMOS están dispuestos con el sustrato conectado a masa (20).

6. Dispositivo según la reivindicación 1, caracterizado por el hecho de que dicho conjunto de transistores comprende un interruptor de by-pass (21) dispuesto en paralelo con dichos transistores controlado por dicho registro de control digital (3).

Patentes similares o relacionadas:

Sistema y método para el control de múltiples reguladores de tensión, del 25 de Marzo de 2020, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Una unidad de gestión de energía , que comprende: un circuito de control digital operativo para generar primero y segundo valores de tensión (logic_vsel, […]

Esquema de doble alimentación en el circuito de memoria, del 1 de Marzo de 2019, de QUALCOMM INCORPORATED: Un dispositivo de memoria de semiconductor de doble voltaje que comprende: una pluralidad de controladores de escritura (105a-c) que reciben señales de entrada de datos de […]

Métodos y sistemas para gestión de datos de memoria no volátil, del 9 de Enero de 2019, de Winbond Electronics Corp: Un sistema, que comprende: una primera matriz de memoria no volátil resistiva ; una segunda matriz de memoria no volátil basada en transistores […]

Borne seleccionable por el usuario para conexión de regulador interno a un condensador externo de filtro/estabilización y prevención de sobrecorriente entre los mismos, del 10 de Diciembre de 2015, de MICROCHIP TECHNOLOGY INCORPORATED: Un dispositivo de circuito integrado que tiene un regulador interno de la tensión y varias conexiones externas seleccionables , en […]

Borne seleccionable por el usuario para conexión de regulador interno a un condensador externo de filtro/estabilización y prevención de sobrecorriente entre los mismos, del 10 de Diciembre de 2015, de MICROCHIP TECHNOLOGY INCORPORATED: Un dispositivo de circuito integrado que tiene un regulador interno de la tensión y varias conexiones externas seleccionables , en […]

Circuito integrado con tensión de alimentación independiente para la memoria que es diferente de la tensión de alimentación del circuito lógico, del 23 de Abril de 2013, de APPLE INC.: Un circuito integrado que comprende: al menos un circuito lógico alimentado por una primera tensión de alimentación; y al menos un circuito de memoria […]

CIRCUITO PARA GENERAR TENSIONES NEGATIVAS, del 16 de Enero de 2002, de SIEMENS AKTIENGESELLSCHAFT: LA INVENCION SE REFIERE A UN CIRCUITO PARA GENERAR TENSIONES NEGATIVAS, QUE COMPRENDE UN PRIMER TRANSISTOR (TX2), CUYO PRIMER TERMINAL ESTA CONECTADO A UN TERMINAL DE […]

CIRCUITO DE REGULACION DE TENSION DE PROGRAMACION, PARA MEMORIAS PROGRAMABLES., del 16 de Septiembre de 1995, de GEMPLUS CARD INTERNATIONAL: LA INVENCION CONCIERNE A LOS CIRCUITOS PARA PRODUCIR UNA TENSION VPP A PARTIR DE UNA ALIMENTACION MAS PEQUEÑA VCC. TALES CIRCUITOS SON UTILES POR EJEMPLO […]

CIRCUITO INTEGRADO CON TENSIÓN DE ALIMENTACIÓN INDEPENDIENTE PARA LA MEMORIA QUE ES DIFERENTE DE LA TENSIÓN DE ALIMENTACIÓN DEL CIRCUITO LÓGICO, del 14 de Diciembre de 2011, de APPLE INC.: Un circuito integrado , que comprende: por lo menos un circuito lógico alimentado por una primera tensión de alimentación (VL) recibida en una primer5 a entrada al circuito […]