PUERTA LÓGICA DIFERENCIAL DE N ENTRADAS.

Puerta lógica diferencial de n entradas.

La presente invención permite realizar las funciones lógicas OR/NOR,

AND/NAND con estándares con diferencias de tensión entre los estados lógicos "0" y "1" inferiores a 0,7 V, tales como LVDS. Esto es útil en aplicaciones en las que se requiere una alta velocidad de transmisión y una buena inmunidad al ruido.

La invención se basa en una serie de circuitos electrónicos en los que se hace uso de 2n diodos Schottky del tipo Zero Bias y comparadores, en los que según el tipo de conexión entre ellos se consigue realizar un tipo de entrada lógica u otra.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201100287.

Solicitante: UNIVERSIDAD COMPLUTENSE DE MADRID.

Nacionalidad solicitante: España.

Inventor/es: TEJEDOR ÁLVAREZ,Luis Ángel.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K19/0956 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › Lógica de transistores FET y de diodos Schottky (H03K 19/096 tiene prioridad).

- H03K19/20 H03K 19/00 […] › caracterizados por la función lógica, p. ej. circuitos Y, O, NI, NO (H03K 19/003 - H03K 19/01 tienen prioridad).

Fragmento de la descripción:

Puerta lógica diferencial de n entradas.

Resumen:

Puerta lógica diferencial de n entradas.

La presente invención permite realizar las funciones lógicas OR/NOR, ANO/NANO con estándares con diferencias de tensión entre los estados lógicos "O" y "1" inferiores a 0, 7 V, tales como LVOS. Esto es útil en aplicaciones en las que se requiere una alta velocidad de transmisión y una buena inmunidad al ruido.

La invención se basa en una serie de circuitos electrónicos en los que se hace uso de 2n diodos Schottky del tipo Zero Bias y comparadores, en los que según el tipo de conexión entre ellos se consigue realizar un tipo de entrada lógica u otra.

Sector de la Técnica:

Sector industrial de fabricación de semiconductores y componentes microelectrónicos.

Estado de la Técnica:

Actualmente los estándares lógicos rápidos diferenciales y con offset de continua, como L VDS (Low Voltage Differential Signalling) o ECL (Emittercoupled Logic) , se utilizan con éxito en aplicaciones que requieren una alta velocidad de transmisión de información por canales ruidosos o bien una alta velocidad de proceso de dicha información.

Mientras que en el caso de las familias lógicas ECL, PECL (Positive Emittercoupled Logic) y L VPECL (Low Voltage Emitter-coupled Logic) existe una pequeña gama de componentes comerciales para realizar la transmisión, recepción y procesado digital de los datos, por ejemplo del fabricante ON Semiconductor (www.onsemi.com) . en LVOS existen componentes para transmitir, recibir o regenerar la señal, pero no para realizar operaciones lógicas con ella. Esto es un problema si la aplicación en cuestión requiere un consumo de potencia bajo, que se puede conseguir con L VOS pero no con las otras familias.

Sin recurrir a componentes electrónicos que contengan la función lógica integrada, se han realizado algunos montajes que realizan funciones lógicas mediante transistores y diodos Schottky, como en la patente US3914620. Esto es útil para el estándar ECL, pero no cuando la diferencia de tensión entre los niveles lógicos es menor que la típica caída de tensión de un diodo en directa, de unos 0, 7 V para un diodo de silicio convencional, o de 0, 5 V para un Schottky, con cierta variación de estos niveles según fabricantes y modelos.

Hasta ahora, la solución habitualmente adoptada cuando se necesitaba realizar una operación lógica con señales L VDS consistía en convertir la señal a otro estándar, típicamente de la familia ECL ya que las tradicionales TTL o CMOS no son capaces de conseguir las mismas velocidades; realizar la operación lógica y volver a convertir la señal al estándar L VDS. Este tipo de soluciones, aunque son capaces de realizar la función deseada, presentan varios problemas: necesitan componentes especiales para realizar la conversión, son caras, consumen más debido a que las tecnologías ECL mantienen un nivel de continua a la salida del orden de 3V mientras que en LVSO ese nivel es de 1V, y son propensas a errores.

Este problema planteado se resuelve con la invención propuesta ya que ésta consiste en una serie de circuitos capaces de realizar las funciones lógicas OR/NOR o ANO/NANO en estándar LVOS u otros que también utilicen señales diferenciales. En concreto, en estándar L VDS no existe ninguna otra alternativa conocida.

Explicación de la Invención:

La invención se basa en una serie de circuitos electrónicos capaces de realizar las funciones lógicas OR/NOR o ANO/NANO en estándar L VDS u otros que también utilicen señales diferenciales. En general la invención puede funcionar con cualquier estándar diferencial, aunque resulta especialmente interesante para aquellos en los que la diferencia de tensión entre la señal "O" y la "1" es inferior a la caída de tensión en un diodo polarizado en directa (del orden de 0, 7 V) . En concreto en estándar LVDS no existe ninguna otra alternativa conocida.

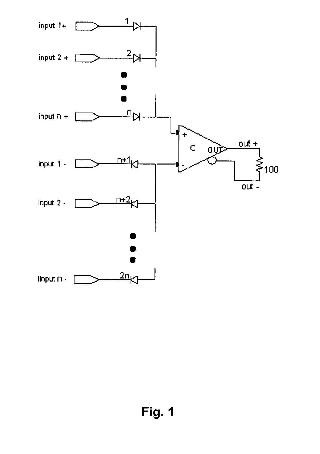

En el caso de la puerta OR la invención consta de un comparador (C) y 2n diodos Schottky de tipo "lero Bias" (1, 2, ... , n, n+1, n+2, ... , y 2n) en una configuración como la que se muestra en la figura1. Las entradas positivas (input 1 +, input 2+, input n+) entran por el ánodo de cada uno de los diodos 1, 2, ... y n, que tienen todos sus cátodos conectados a la entrada positiva del comparador (C) . Por el contrario, las entradas negativas (input 1-, input 2-, input n-) entran por el cátodo de los diodos n+1, n+2, ... , y 2n, que a su vez tienen todos sus ánodos cortocircuitados y unidos a la entrada negativa del comparador (C) .

El modo de funcionamiento es el siguiente: si todas las entradas tienen ceros lógicos, en estándar LVDS habrá 1 V en todas las entradas positivas (input 1+, input 2+, input n+) y 1, 4 Ven las negativas (input 1-, input 2-, input n-) . Al utilizar diodos Schottky tipo "lero Bias" se consigue que apenas haya caída de tensión en ellos y que, por lo tanto, el comparador (C) vea 1 V en su entrada positiva y 1, 4 V en la negativa. El comparador producirá como señal de salida un O lógico.

Por el contrario, si al menos una de las entradas diferenciales tiene un 1 lógico, en la entrada positiva del comparador habrá 1, 4 V Y en la negativa 1 V, con lo cual habrá un 1 lógico a la salida del comparador (C) . De este modo se consigue realizar la función lógica OR.

La característica principal del diseño propuesto es su capacidad para trabajar con estándares que tienen una diferencia de tensión entre las señales de Oy 1 lógicos inferior a 0, 7 V. Ello es posible gracias a que los diodos Schottky tipo "lero Bias" tienen una caída de tensión entre ánodo y cátodo muy pequeña (idealmente de O V) , de modo que la tensión cuando hay un 1 lógico siempre es mayor que cuando hay un O. Con diodos convencionales de silicio, la diferencia de tensión entre cátodo y ánodo sería de aproximadamente 0, 7 V, lo que haría inviable el circuito. Además, el hecho de que los diodos utilizados en la invención sean Schottky, permite que la puerta lógica pueda trabajar con señales muy rápidas, con pulsos al menos tan cortos como 1, 5 ns.

En cualquier otro estándar que también utilice señales diferenciales los niveles de tensión serán distintos, pera mientras las entradas positivas tengan una tensión mayor en estado "1" que en "O" y las negativas una tensión mayor en "O" que en "1 ", la invención funcionará.

Si en su lugar se desease realizar la función NOR, bastaría con intercambiar las salidas positiva y negativa del comparador (C) en el circuito anteriormente descrito (figura 2) .

La función ANO también puede realizarse con el mismo circuito (figura 3) , sin más que cambiar la forma de conexión de los diodos. En esta ocasión, se conectan las entradas positivas (input 1 +, input 2+, input n+) al cátodo de cada uno de los diodos 1, 2, ... y n, cuyos ánodos están conectados a su vez con la entrada positiva del comparador (C) y conectando las entradas negativas (input 1-, input 2-, input n-) al ánodo de los diodos n+1, n+2, ... , y 2n, que tienen sus cátodos cortocircuitados y unidos la entrada negativa del comparador (C) .

En este caso de la puerta ANO el modo de funcionamiento es el siguiente: si todas las entradas tienen 1 lógicos, en estándar L VDS habrá 1, 4 V en todas las entradas positivas (input 1 +, input 2+, input n+) y 1 V en las negativas (input 1-, input 2-, input n-) . Al utilizar diodos Schottky tipo "Zera Bias" se consigue que apenas haya caída de tensión en ellos y que, por lo tanto, el comparador (C) vea 1, 4 V en su entrada positiva y 1 V en la negativa. El comparador producirá como señal de salida un 1 lógico.

Por el contrario, si al menos una de las entradas tiene un O lógico, en la entrada positiva del comparador habrá 1 V Y en la negativa 1, 4 V, con lo cual

habrá un O lógico a la salida del comparador (e) . Así se consigue realizar la

función lógica ANO. Análogamente al caso de la puerta OR, la puerta NANO puede obtenerse sin más que invertir las salidas del comparador (e) (figura 4) en este segundo

circuito descrito. Explicación de los dibujos: Figura 1: Esquema de puerta OR de n entradas. Figura 2: Esquema de puerta NOR de n entradas. Figura 3: Esquema de puerta ANO de n entradas.

Figura 4: Esquema de puerta NANO de n entradas. Figura 5: Esquema...

Reivindicaciones:

1. Puerta lógica de n entradas caracterizado porque comprende al menos un comparador (C) y 2n diodos Schottky de tipo "lero Bias" (1, 2, ... , n, n+1, n+2, ... , y 2n)

Y porque realiza las funciones lógicas en estándares que utilizan señales diferenciales.

2. Puerta lógica de n entradas según reivindicación 1 caracterizada porque el estándar diferencial utilizado es el L VDS.

3. Puerta lógica de n entradas según reivindicación 1 caracterizada porque las entradas positivas (input 1 +, input 2+, input n+) entran por el ánodo de cada uno de los diodos 1, 2, ... Y n, que tienen todos sus cátodos conectados a la entrada positiva del comparador (C) , y las entradas negativas (input 1-, input 2-, input n-) entran por el cátodo de los diodos n+1, n+2, ... , y 2n, que a su vez tienen todos sus ánodos cortocircuitados y unidos a la entrada negativa del comparador (C) .

4. Puerta lógica de n entradas según reivindicaciones 1, 2 Y 3 caracterizada porque cuando todas las entradas tienen ceros lógicos, en estándar L VDS, hay una tensión de 1 Ven todas las entradas positivas (input 1+, input 2+, input n+) y una tensión de 1, 4 V en las entradas negativas (input 1-, input 2-, input n-) de los diodos, la señal pasa por ellos sin que apenas haya caída de tensión en su interior y el comparador (C) reconoce 1 V en su entrada positiva y 1, 4 V en la negativa y produce como señal de salida un O lógico, generando la función lógica OR;

y porque cuando al menos una de las entradas tiene un 1 lógico, en estándar LVDS, el comparador (C) reconoce 1 Ven su entrada positiva y 1, 4 Ven la negativa y produce como señal de salida un O lógico, generando la función lógica OR.

5. Puerta lógica de n entradas según reivindicaciones 1, 2, 3 Y 4 caracterizada porque cuando se intercambian las salidas positiva y negativa del comparador (C) se genera la función lógica NOR.

6. Puerta lógica de n entradas según reivindicación 1 caracterizada porque las entradas positivas (input 1 +, input 2+, input n+) entran por el cátodo de cada uno de los diodos 1, 2, ... Y n, que tienen todos sus ánodos conectados a la entrada positiva del comparador (C) , y las entradas negativas (input 1-, input 2-, input n-) entran por el ánodo de los diodos n+1, n+2, ... , y 2n, que a su vez tienen todos sus cátodos cortocircuitados y unidos a la entrada negativa del comparador (C) .

7. Puerta lógica de n entradas según reivindicaciones 1, 2 Y 6 caracterizada porque cuando todas las entradas tienen unos lógicos, en estándar L VOS, hay una tensión de 1, 4 V en todas las entradas positivas (input 1 +, input 2+, input n+) y una tensión de 1 V en las entradas negativas (input 1-, input 2-, input n-) de los diodos, la señal pasa por ellos sin que apenas haya caída de tensión en su interior y el comparador (C) reconoce 1, 4 V en su entrada positiva y 1 V en la negativa y produce como señal de salida un 1 lógico, generando la función lógica ANO.

y porque cuando al menos una de las entradas tiene un cero lógico, en estándar LVOS, el comparador (C) reconoce 1 V en su entrada positiva y 1, 4 V en la negativa y produce como señal de salida un O lógico, generando la función lógica ANO.

8. Puerta lógica de n entradas según reivindicaciones 1, 2, 6 Y 7 caracterizada porque cuando se intercambian las salidas positiva y negativa del comparador (C) se genera la función lógica NANO.

Patentes similares o relacionadas:

Diseños para lógica XOR y XNOR, del 8 de Junio de 2016, de Tela Innovations, Inc: Un diseño de circuito exclusivo OR lógico, que comprende: seis transistores PMOS; y cinco transistores NMOS, en el que los cinco transistores […]

CIRCUITO DE BLOQUEO., del 1 de Abril de 2002, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): CIRCUITO DE RETENCION DE BAJA TENSION ADAPTADO AL MODO DIFERENCIAL CON UNA TENSION DE ALIMENTACION DE 2,5 V Y UNA OSCILACION DE TENSION DE 200 MV A 300 MV. SE […]

INVERSOR CONMUTABLE., del 1 de Abril de 1999, de MENDEZ-VIGO BARASONA, JAVIER: INVERSOR CONMUTABLE QUE SE ACTIVA CUANDO LA BASE EMISOR PUEDA COMPUTAR, ES DECIR, CUANDO LA SUMA DE LAS CORRIENTES SON IGUALES A LA CORRIENTE […]

SISTEMA Y CIRCUITOS ELECTRONICOS DIGITALES MULTIESTADO., del 1 de Abril de 1992, de ARIÑO FERRER, FRANCISCO JAVIER: SISTEMA Y CIRCUITOS ELECTRONICOS DIGITALES MULTIESTADO QUE PUEDEN ADOPTAR VARIOS ESTADOS O NIVELES LOGICOS DIFERENTES, Y QUE COMPRENDE DISTINTOS CIRCUITOS DETECTORES […]