PROCEDIMIENTO Y DISPOSITIVO PARA COMPARAR DATOS EN UN SISTEMA INFORMATICO CON AL MENOS DOS UNIDADES DE EJECUCION.

Procedimiento para comparar datos en un sistema informático (G60) con al menos dos unidades de ejecución (G10a,

G10b), en donde la comparación de los datos se realiza en una unidad de comparación (G20) y cada unidad de ejecución (G10a, G10b) trata datos de entrada y genera datos de salida, caracterizado porque una unidad de ejecución (G10a, G10b) de la unidad de comparación prefija que el siguiente dato de salida se pretende comparar con un dato de salida de al menos una segunda unidad de ejecución (G10a, G10b) y, de aquí, se produce una comparación de al menos los dos datos de salida

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2006/064730.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20,70442 STUTTGART.

Inventor/es: MUELLER, BERND, BOEHL,EBERHARD, WEIBERLE,REINHARD, COLLANI,YORCK, GMEHLICH,RAINER.

Fecha de Publicación: .

Fecha Concesión Europea: 2 de Diciembre de 2009.

Clasificación Internacional de Patentes:

- G06F11/16C6

- G06F11/16T

Clasificación PCT:

- G06F11/16 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Detección o corrección de errores en un dato por redundancia en el hardware.

Fragmento de la descripción:

Procedimiento y dispositivo para comparar datos en un sistema informático con al menos dos unidades de ejecución.

Estado de la técnica

La invención se basa en un procedimiento y un dispositivo para comparar entre datos de salida de al menos dos unidades de ejecución de un microprocesador, conforme a los preámbulos de las reivindicaciones independientes.

Los errores transitorios, provocados por partículas alfa o radiación cósmica, se están convirtiendo cada vez más en un problema para circuitos integrados. A causa de anchuras estructurales decrecientes, tensiones en reducción y mayores frecuencias de reloj aumenta la probabilidad de que un pico de tensión, provocado por una partícula alfa o una radiación cósmica, falsee un valor lógico en un circuito integrado. Un resultado de cálculo erróneo puede ser la consecuencia. En los sistemas importantes para la seguridad es necesario por ello detectar estos errores de forma fiable.

En los sistemas importantes para la seguridad, como por ejemplo un sistema regulador ABS en un vehículo de motor, en los que tienen que detectarse con seguridad funciones defectuosas del sistema electrónico, se prevén normalmente redundancias para el reconocimiento de errores precisamente en el caso de los mecanismos de control correspondientes de tales sistemas. De este modo, por ejemplo, en los sistemas ABS conocidos está duplicado en cada caso todo el microcontrolador, en donde todas las funciones ABS se calculan de forma redundante y se comprueba su coincidencia. Si se produce una discrepancia de los resultados, se desconecta el sistema ABS.

Estas unidades de procesador con al menos dos unidades de ejecución integradas se conocen también como arquitecturas Dual-Core o Multi-Core. Las diferentes unidades de ejecución (Cores) ejecutan de forma redundante y sincronizada el mismo segmento de programa, se comparan los resultados de las dos unidades de ejecución, y se reconoce después un error al comparar la coincidencia. Los ordenadores Multi-core se conocen ya del documento US5572662.

Ventajas de la invención

Si se pretende que los procesadores Dual-Core actuales trabajen en un modo de comparación, los Cores o las unidades de ejecución tienen que ser en gran medida idénticos, para que las señales de salida puedan compararse en cada ciclo. Sin embargo, bajo aspectos de seguridad es también ventajoso que se utilicen unidades de ejecución redundantes. Sin embargo, si las unidades de ejecución son redundantes las señales de salida de estas unidades de ejecución ya no pueden compararse en cada ciclo.

La tarea de esta invención es comparar señales de salida de unidades de ejecución redundantes. La invención aquí presentada resuelve este problema mediante la implantación de una señal de control con la que una unidad de ejecución de una unidad de comparación señala que la dato, que se emite con esta señal, se pretende comparar con una dato de la otra unidad de ejecución. De este modo pueden utilizarse unidades de ejecución redundantes y softwares redundantes. Sólo los datos a comparar y su formato tienen que ser comparables. De la respectiva implantación de la invención aquí descrita depende de si también tiene que ser idéntica la secuencia en la que tienen que transmitirse los datos a comparar de la unidad de comparación.

Esta tarea es resuelta conforme a la invención mediante las particularidades definidas en las reivindicaciones 1 y 8 independientes adjuntas.

De forma ventajosa una unidad de ejecución de la unidad de comparación prefija que el siguiente dato de salida se pretende comparar con un dato de salida de al menos una segunda unidad de ejecución y, de aquí, se produce una comparación de al menos los dos datos de salida. De forma conveniente al menos dos unidades de ejecución tratan los datos de entrada con independencia unos de otros. La prefijación de que se pretende comparar el siguiente dato de salida se realiza ventajosamente mediante una señal de comparación. La señal de comparación y el dato de salida que se pretende comparar se emiten de forma que puedan asociarse entre sí de forma inequívoca. De forma conveniente se asocia al dato que se pretende comparar una identificación, mediante la cual se activa la comparación. Todas las unidades de ejecución señalizan de forma ventajosa qué datos de salida se pretende comparar, a través de al menos una memoria tampón, en una secuencia prefijable. De forma ventajosa una unidad de ejecución de la unidad de comparación prefija que el siguiente dato de salida se pretende comparar con un dato de salida de al menos la segunda unidad de ejecución y, según esto, se realiza una comparación de al menos los dos datos de salida. De forma ventajosa está prevista en el dispositivo al menos una memoria tampón, que está configurada de tal modo que los datos se archivan de forma intermedia en una secuencia prefijable y después pueden alimentarse a la unidad de comparación. De forma ventajosa se trata en el caso de la memoria tampón de una memoria FIFO. De forma ventajosa se representa esto en un dispositivo así como en un sistema informático que contiene este dispositivo.

Se deducen ventajas adicionales y configuraciones ventajosas de las particularidades de las reivindicaciones así como de la descripción.

Figuras

En la figura 1 se ha representado un sistema microprocesador G60 con dos unidades de ejecución G10a y G10b, así como una unidad de comparación G20.

En la figura 2 se ha representado una forma de ejecución de una unidad de comparación G20 con dos colas G21a y G21b.

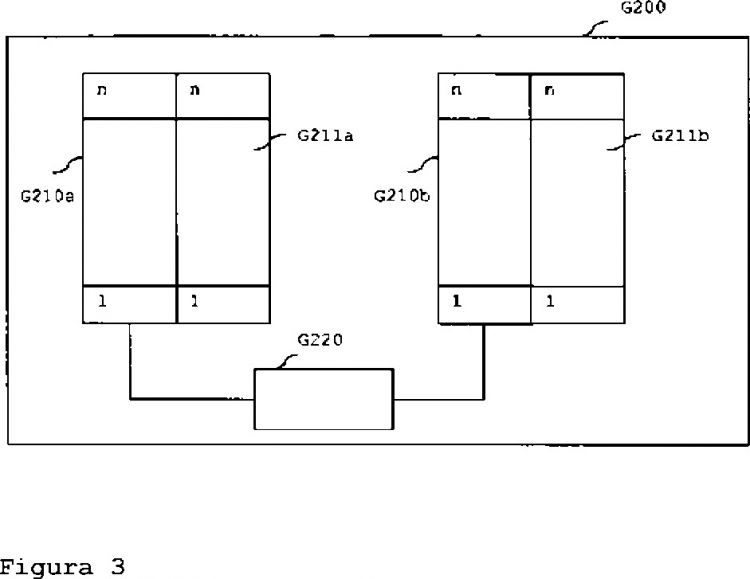

En la figura 3 se ha representado una forma de ejecución de una unidad de comparación G200 con en cada caso dos listas G210a, G211a y G211b.

Descripción de los ejemplos de ejecución

Una unidad de ejecución puede designar de aquí en adelante, a este respecto, tanto un procesador/Core/CPU, como también una FPU (Floating Point Unit), DSP (procesador digital de señales), Coprocesador o ALU (Arithmetic Logical Unit). La invención se refiere a un sistema multiprocesador G60, representado en la figura 1 con al menos dos unidades de ejecución G10a, G10b y una unidad de comparación G20. Cada una de las unidades de ejecución G10a, G10b tiene al menos una salida a interfaces de sistema G30a, G30b correspondientes. A través de estos interfaces puede activarse registros, memorias o periféricos como salidas digitales, convertidores C/A y controladores de comunicación. Las señales de salida de las unidades de ejecución G10a, G10b pueden compararse en la unidad de comparación G20. En el caso de una diferencia se reconoce un error y pueden adoptarse medidas correspondientes. Para la comparación se utilizan los datos de salida y/o las direcciones de las unidades de ejecución. Es posible someter señales de control adicionales a una comparación. A continuación se habla del dato, con independencia de las señales de salida seleccionadas que se pretende comparar, el cual se pretende comparar con otros datos.

La figura 1 muestra una posible implementación para un sistema microprocesador G60 con dos unidades de ejecución G10a y G10b. La unidad de comparación G20 se activa mediante una señal de control G50a, G50b de las unidades de ejecución G10a, G10b. Si una unidad de ejecución G10a, G10b pretende transmitir un dato al interfaz de sistema G30a o G30b, sin que éste se pretenda comparar, estos se transmiten sin aplicar las señales G50a, G50b. La unidad de comparación G20 no se ocupa de este modo de estos datos. Si una unidad de ejecución G10a, G10b quiere transmitir un dato al interfaz de sistema G30a o G30b y se pretende comparar este dato con un dato correspondiente de la otra unidad de ejecución G10a, G10b, se genera además de las señales de salida de la unidad de ejecución, necesarias para una transferencia de datos al interfaz de sistema, una señal G50a en G10a, G50b en G10b para la unidad de comparación G20. Estas señales G50a y G50b son generadas también por las unidades de ejecución G10a y G10b. Estas señalizan a la unidad de comparación G20 que el dato transmitido al interfaz de sistema, opcionalmente con la dirección correspondiente, se pretende comparar con un dato correspondiente en cada caso de la otra unidad de ejecución. La comparación tiene después lugar si la otra unidad de ejecución transmite un dato a su interfaz de sistema y con ello señala a la unidad de comparación G20 también una comparación a ejecutar. La señal G50a en G10a, G50b en G10b para al comparación no es necesario que se genere al mismo tiempo que la transmisión del dato desde la unidad de ejecución, pero sí de...

Reivindicaciones:

1. Procedimiento para comparar datos en un sistema informático (G60) con al menos dos unidades de ejecución (G10a, G10b), en donde la comparación de los datos se realiza en una unidad de comparación (G20) y cada unidad de ejecución (G10a, G10b) trata datos de entrada y genera datos de salida, caracterizado porque una unidad de ejecución (G10a, G10b) de la unidad de comparación prefija que el siguiente dato de salida se pretende comparar con un dato de salida de al menos una segunda unidad de ejecución (G10a, G10b) y, de aquí, se produce una comparación de al menos los dos datos de salida.

2. Procedimiento según la reivindicación 1, caracterizado porque al menos dos unidades de ejecución (G10a, G10b) tratan los datos de entrada con independencia unos de otros.

3. Procedimiento según la reivindicación 1, caracterizado porque la prefijación de que el siguiente dato de entrada se pretende comparar se realiza mediante una señal de comparación.

4. Procedimiento según la reivindicación 3, caracterizado porque la señal de comparación y el dato de salida que se pretende comparar se emiten de forma que puedan asociarse entre sí de forma inequívoca.

5. Procedimiento según la reivindicación 4, caracterizado porque se asocia al dato que se pretende comparar una identificación, mediante la cual se activa la comparación.

6. Procedimiento según la reivindicación 1, caracterizado porque todas las unidades de ejecución (G10a, G10b) cuyos datos de salida se pretende comparar, señalizan esto a la unidad de comparación (G20).

7. Procedimiento según la reivindicación 1, caracterizado porque los datos de salida que se pretende comparar se almacenan de forma intermedia a través de al menos una memoria tampón, en una secuencia prefijable.

8. Dispositivo para comparar datos en un sistema informático (G60) con al menos dos unidades de ejecución (G10a, G10b) y una unidad de comparación (G20), en donde la comparación de los datos se realiza en la unidad de comparación (G20) y cada unidad de ejecución (G10a, G10b) trata datos de entrada y genera datos de salida, caracterizado porque una unidad de ejecución (G10a, G10b) de la unidad de comparación prefija que el siguiente dato de salida se pretende comparar con un dato de salida de al menos una segunda unidad de ejecución (G10a, G10b) y, de aquí, se produce una comparación de al menos los dos datos de salida.

9. Dispositivo según la reivindicación 9, caracterizado porque está prevista en el dispositivo al menos una memoria tampón, que está configurada de tal modo que los datos se archivan de forma intermedia en una secuencia prefijable y después pueden alimentarse a la unidad de comparación.

10. Dispositivo según la reivindicación 10, caracterizado porque en el caso de la memoria tampón se trata de una memoria FIFO.

11. Sistema informático con un dispositivo según la reivindicación 9.

Patentes similares o relacionadas:

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Procedimiento de parada de emergencia y sistema de seguridad asociado, del 20 de Mayo de 2020, de CLEARSY: Procedimiento de parada de emergencia de un elemento de seguridad de un conjunto de seguridad , comprendiendo el conjunto de seguridad […]

Actualización de software de componentes no críticos en sistemas distribuidos críticos para la seguridad dual, del 13 de Mayo de 2020, de Siemens Mobility GmbH: Procedimiento para el funcionamiento de un sistema crítico para la seguridad con al menos un primer dispositivo de datos con un software aprobado y relevante […]

Sistemas críticos de seguridad ferroviaria con redundancia de tareas y capacidad de comunicaciones asimétricas, del 22 de Enero de 2020, de Siemens Mobility, Inc: Sistema de control para un sistema de aplicación crítico de seguridad ferroviaria, que comprende: al menos un controlador, que comprende un procesador […]

Circuito integrado digital protegido contra errores transitorios, del 9 de Octubre de 2019, de THALES: Circuito integrado digital que comprende un conjunto lógico que comprende un bloque lógico funcional, una unidad lógica de detección […]

Circuito de generación de reloj y procedimiento de generación de la señal de reloj, del 12 de Junio de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un circuito de generación de reloj , que comprende una primera fuente de reloj , una segunda fuente de reloj y un circuito de puerta lógica , […]

Sistema informático de seguridad de tipo relevante, del 7 de Mayo de 2019, de Siemens Mobility GmbH: Sistema informático de seguridad de tipo relevante, particularmente un sistema de seguridad ferroviario, con al menos dos canales hardware (A; B), en donde los […]

Método, ordenador y aparato para migrar datos de memoria, del 6 de Marzo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un ordenador, que comprende: un procesador ; un sistema básico de entrada/salida ; una memoria principal , configurada para cargar […]