CIRCUITO INTEGRADO PARA LA LECTURA DIGITAL DE SENSORES DE IMAGEN DE ALTA VELOCIDAD.

Circuito integrado para la lectura digital de sensores de imagen de alta velocidad.

La presente invención se refiere a circuitos integrados de lectura (Read-Out Integrated Circuit, ROIC) de matrices de sensores de imagen. Introduce una nueva topología de modulador de pulsos como parte del conversor analógico-digital para píxeles activos digitales que atenúa las pérdidas de señal debidas a los tiempos de inicialización del integrador analógico. También implementa la función de cancelación de ruido de baja frecuencia del integrador analógico mediante doble muestreo correlado. Frente a la tecnología actual, la invención presenta la ventaja de aumentar la velocidad de captura de la imagen o alternativamente disminuir el consumo de potencia en los píxeles activos sin pérdida de resolución

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200801428.

Solicitante: CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC).

Nacionalidad solicitante: España.

Provincia: MADRID.

Inventor/es: TERES TERES,LLUIS, SIERRA GRAELLS,FRANCISCO, MARGARIT TAULE,JOSEP MARIA.

Fecha de Solicitud: 16 de Mayo de 2008.

Fecha de Publicación: .

Fecha de Concesión: 18 de Agosto de 2010.

Clasificación Internacional de Patentes:

- H01L27/146A4

- H03K17/94L

- H04N3/15E

- H04N5/335B

Clasificación PCT:

- H01L27/00 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00).

- H01L27/146 H01L […] › H01L 27/00 Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00). › Estructuras de captadores de imágenes.

- H03K17/94 H […] › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 17/00 Conmutación o apertura de puerta electrónica, es decir, por otros medios distintos al cierre y apertura de contactos (amplificadores controlados H03F 3/72; disposiciones de conmutación para los sistemas de centrales que utilizan dispositivos estáticos H04Q 3/52). › caracterizado por la manera en que son producidas las señales de control.

- H04N3/15

- H04N5/335 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04N TRANSMISION DE IMAGENES, p. ej. TELEVISION. › H04N 5/00 Detalles de los sistemas de televisión (Detalles de los dispositivos de análisis o sus combinaciones con la producción de la tensión de alimentación H04N 3/00). › que utiliza sensores de imagen de estado sólido [SIES] (H04N 5/32, H04N 5/33 take precedence).

Fragmento de la descripción:

Circuito integrado para la lectura digital de sensores de imagen de alta velocidad.

Sector de la técnica

La presente invención se refiere a los sectores de las tecnologías de la información y de las comunicaciones, y describe un dispositivo microelectrónico específico para la captura digital de imágenes estáticas o dinámicas. Dichas imágenes se descomponen en píxeles, cuyo valor individual se obtiene de la lectura de un sensor óptico monolítico o híbrido. La agrupación en matriz de estos sensores constituye el plano focal de la imagen a capturar. Teniendo en cuenta el estado de la técnica actual, la presente invención presenta la ventaja de permitir mantener la resolución frente a una mayor velocidad de captura de la imagen o alternativamente disminuir el consumo de potencia en los píxeles activos.

Estado de la técnica actual

El mercado de los semiconductores experimenta actualmente una creciente demanda de dispositivos portátiles capaces de capturar imágenes a muy alta velocidad, para aplicaciones tales como navegación nocturna en automoción, diagnóstico médico o equipamiento estratégico. En general, estos dispositivos de imagen se basan en matrices de plano focal (Focal Plane Array, FPA) formadas por píxeles activos sensores (Active Pixel Sensor, APS), cada uno conteniendo tanto el elemento sensor óptico como su circuito individual de pre-procesado.

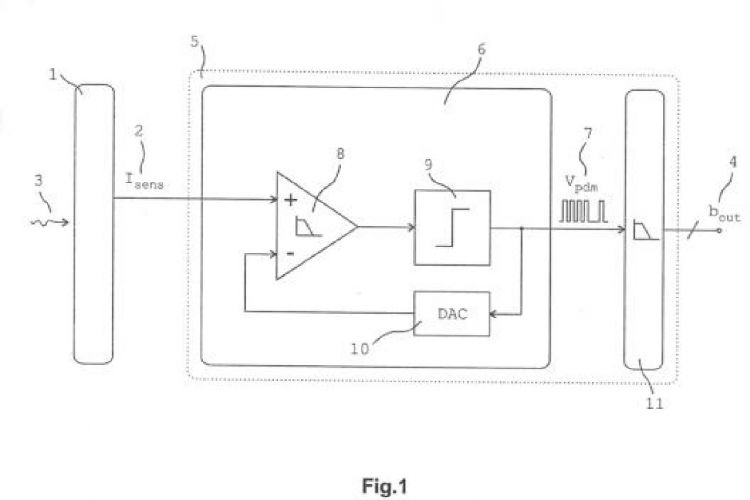

Las técnicas de diseño modernas para celdas APS incluyen parcialmente [US5461425, 1995-10-24, Standford University (US); US6707410, 2004-03-16, Micron Technology Inc. (US); US7023369, 2006-04-04, University of Rochester (US)] o completamente [US6741198, 2004-03-25, R3 Logic Inc (US)] el conversor analógico-digital (Analog-to-Digital Converter, ADC) dentro del propio APS, dando lugar a pixeles activos digitales (Digital Pixel Sensor, DPS). Dadas las restricciones de espacio físico dentro del pixel activo, las arquitecturas ADC más adoptadas en la actualidad para celdas DPS son de tipo predictivo, frente a las alternativas directas (p.e. paralela) y algorítmicas (p.e. aproximaciones sucesivas), ya que permiten simplificar las partes analógicas del ADC. En ese sentido, la cadena de procesado completa o parcialmente incluida dentro de cada DPS se muestra en la Figura 1. Su principio básico de funcionamiento es el siguiente: el sensor óptico (1) genera una corriente Isens (2) proporcional a la potencia de la iluminación incidente (3) y a su función de respuesta; el nivel de corriente (2) se convierte a lectura digital de salida bout (4) discreta, en amplitud y tiempo, mediante el bloque ADC predictivo (5). Dicho ADC (5) se compone de dos etapas en cascada: un modulador PDM, Pulse Density Modulation, (6) y un filtro digital (11). La primera etapa (6) se encarga de discretizar la amplitud a l bit en forma de tren de pulsos Vpdm (7); las partes principales de este modulador (6) son un bloque de ganancia de baja frecuencia (8), un cuantificador (9) y un conversor digital-analógico (Digital-to-Analog Converter, DAC) (10) que suministra la realimentación necesaria para la predicción. La potencia del error de cuantificación resultante de dicha modulación se concentra principalmente en las componentes de alta frecuencia de Vpdm (7), por lo que se aplica a continuación un filtrado digital paso bajo en la segunda etapa (11), que además completa la discretización en tiempo. Como resultado se obtiene la palabra digital de salida bout (4).

Con el fin de reducir el consumo de potencia por pixel, el modulador (6) suele implementarse mediante técnicas de diseño asíncronas, ya sean de tipo "tiempo a primer suceso" (time to first spike) [US5565915, 1996-10-15, Matsushita Electric Industrial Co; US6271785, 2001-09-07, Texas Instruments Inc; US6377303, 2002-04-23, Intel Corp; US6525304, 2003-02-25, Foveon Inc; US6559788, 2003-05-06; US6969879, 2005-11-29, STMicroelectronics Ltd; US7071982, 2006-07-04, Texas Instruments Inc; US7164114, 2007-01-16, Via Technologies Inc], o de tipo "conteo de sucesos" (spike counting) [US7095439, 2006-09-22, Motorola Inc]. La ventaja de la segunda estrategia es la baja actividad de conmutación digital durante la conversión analógica-digital, con la consiguiente reducción del ruido electrónico.

En el caso de celdas DPS de alta velocidad de adquisición, la topología de circuitos comúnmente empleada para moduladores PDM (6) de conteo de sucesos y también para el filtrado digital (11) se muestran en la Figura 2. Con el fin de minimizar el tamaño de la celda DPS, el modulador PDM compacto de conteo de sucesos (200) se reduce a: un integrador implementado mediante un amplificador de transimpedancia capacitivo (Capacitive Translmpedance Amplifier, CTIA) (201) con capacidad de integración Cint (202), que hace las funciones de bloque de ganancia de baja frecuencia (8) y polariza el sensor óptico (1) a una referencia Vref (203); un comparador (204), que hace las funciones de cuantificador (9) respecto a un umbral Vth (205); y una realimentación del tren de pulsos Vpdm (7) hacia la inicialización (206) del CTIA (201), que hace las funciones de DAC (10). Aparte de esta inicialización en cada pulso de Vpdm (7), el CTIA (201) también se inicializa previamente a la fase de conversión analógica-digital mediante la señal Vinit (207) y por el mismo mecanismo (206). El uso del CTIA (201) está especialmente indicado para celdas DPS de alta velocidad que requieran valores bajos de Cint (202), dado que permite compensar valores elevados de capacidad parásita de entrada Cpar (208), ya sea debida al propio sensor óptico (1), al CTIA (201), o a la interconexión monolítica o híbrida entre ambos. Opcionalmente, el modulador PDM (200) también puede incorporar una segunda capacidad Ccds (209) controlada por la misma señal Vpdm (7) a través de la [lave (210), y destinada a cancelar por CDS (Correlated Double Sampling) el ruido de baja frecuencia del CTIA (201) en la señal integrada Vint (211). Respecto al filtrado digital (11), su realización se reduce a un filtro paso-bajo de primer orden implementado mediante un contador digital (212), que hace las funciones de integrador, y una entrada de inicialización (213) controlada por Vinit (207), que implementa las pérdidas en dicho integrador.

El principio de funcionamiento del ADC predicitvo (5) basado en el modulador PDM (200) y el contador digital (212) se ilustra en la Figura 3, teniendo en cuenta que las llaves de la Figura 2 realizan la operación indicada en cada caso para niveles lógicos altos de sus señales de control. Una vez iniciada la fase de conversión analógica-digital (300) mediante Vinit (207), la evolución de la señal integrada Vint (211) describe una rampa (302), positiva o negativa según el signo de Isens (2), hasta el disparo del comparador (204) a una distancia Vth (205), positiva o negativa según el signo de Isens (2), respecto al nivel de reposo Vref (203). Como consecuencia del mencionado disparo, se produce un pulso (303) en la señal Vpdm (7) que causa la inicialización del CTIA (201) y la vuelta de la señal integrada Vint (211) al nivel de reposo Vref (203) para empezar de nuevo el ciclo. En condiciones ideales (301), la duración de dicho pulso (303) es despreciable comparada con su periodicidad Tpdmideal (304), y en consecuencia la frecuencia de la señal Vpdm (7) es 1/Tpdmideal=Isens/CintVth. Teniendo en cuenta que el contador (212) integra el número de pulsos en Vpdm (7) dentro de la ventana de adquisición Tframe (305), la lectura digital de salida bout (4) en condiciones ideales (301) es proporcional a la corriente Isens (2) del sensor óptico (1) a medir según bout=Tframe/Tpdmideal=Isens(Tframe/CintVth).

En la práctica (306), las limitaciones de potencia en los distintos bloques del modulador PDM (200) provocan una duración Tres (307), no nula, de los pulsos (308) en Vpdm (7). Teniendo en cuenta que el CTIA (201) no puede integrar la corriente del sensor Isens (2) en la capacidad Cint (202) durante el tiempo Tres (307), la evolución real (305) de la señal integrada Vint (211) presenta una periodicidad Tpdmreal (309) superior a la ideal Tpdmideal (304), causando una...

Reivindicaciones:

1. Circuito integrado para la lectura digital de sensores de imagen de alta velocidad caracterizado porque comprende (véase la Figura 5):

2. Circuito integrado para la lectura digital de sensores de imagen de alta velocidad, según la reivindicación 1 y caracterizado por comprender (véase la Figura 5):

3. Circuito integrado para la lectura digital de sensores de imagen de alta velocidad, según las reivindicaciones 1 y 2, caracterizado por comprender (véase la Figura 5):

4. Circuito integrado para la lectura digital de sensores de imagen de alta velocidad, según las reivindicaciones 1, 2 y 3, caracterizado por comprender (véase la Figura 5):

5. Circuito integrado según la reivindicación 1, caracterizado (véase la Figura 6) por inicializar la capacidad de integración Cint (502) del integrador CTIA (501) en cada pulso de salida del modulador PDM (500) mediante la apertura de la llave (506) y el cierre de la llave (507), inyectando a través de Creset/cds (503) el nivel de carga necesario para provocar el retorno de la señal Vint (505) a su valor de reposo Vref (203), sin interrumpir la integración de la corriente Isens (2) del sensor óptico (1) en la capacidad de integración Cint (502) en ningún momento durante toda la ventana de conversión Tframe (305).

6. Circuito integrado según la reivindicación 1, caracterizado (véase la Figura 5) por emplear la misma capacidad Creset/cds (503) que en la reivindicación 2 para atenuar por CDS el efecto del ruido de baja frecuencia del CTIA (501) mediante su pre-compensación en Cint (502) en cada generación de pulsos de salida del modulador PDM (500).

Patentes similares o relacionadas:

PANEL DE CONTROL PARA TABLERO DE MANDO DE UN VEHICULO AUTOMOVIL CON AL MENOS UN BOTON ROTATIVO REGULABLE CON UN MANDO OPTICO, del 22 de Enero de 2010, de VALEO CLIMATISATION: Panel de control de vehículos automóviles provisto de al menos un botón rotativo de regulación de un parámetro relativo a un flujo de aire impulsado por un aparato […]

PANEL DE CONTROL PARA TABLERO DE MANDO DE UN VEHICULO AUTOMOVIL CON AL MENOS UN BOTON ROTATIVO REGULABLE CON UN MANDO OPTICO, del 22 de Enero de 2010, de VALEO CLIMATISATION: Panel de control de vehículos automóviles provisto de al menos un botón rotativo de regulación de un parámetro relativo a un flujo de aire impulsado por un aparato […]

Método para generar una imagen en forma electrónica, elemento de imagen para un sensor de imagen para generar una imagen, así como sensor de imagen, del 4 de Enero de 2017, de AIT AUSTRIAN INSTITUTE OF TECHNOLOGY GMBH: Método para generar una imagen de una escena en forma electrónica a través de elementos de imagen, caracterizado porque una medición de exposición […]

CIRCUITO DE EXCITACION CON PROTECCION DE SOBRETENSION PARA CELULAS DE PIXELS., del 1 de Diciembre de 2004, de AGILENT TECHNOLOGIES, INC.: Un aparato de circuito integrado que comprende: un circuito de sobretensión que es capaz de funcionar en un nivel dado (VDD) de tensión de alimentación y […]

CAPTADOR DE IMAGENES EN ESTADO SOLIDO., del 16 de Noviembre de 2004, de CANON KABUSHIKI KAISHA: PARA REALIZAR UN SENSOR MULTIFUNCION EN EL CUAL EN UNA PARTE DE PIXEL UNA ADICION Y UNA NO ADICION, PUEDEN SER ARBITRARIAMENTE EJECUTADAS, HAY SUMINISTRADO UN APARATO […]

DISPOSITIVO SENSOR DE IMAGENES DE ESTADO SOLIDO CON LINEA DE SALIDA COMUN., del 16 de Julio de 2004, de CANON KABUSHIKI KAISHA: UN DISPOSITIVO DE ESTADO SOLIDO SENSOR DE IMAGEN TIENE UN AMPLIFICADOR-INVERSOR CONSTRUIDO CON TRANSISTORES MOS , EL CUAL ESTA PROVISTO DE POTENCIA ELECTRICA […]

PROCEDIMIENTO Y DISPOSITIVO PARA LA DETERMINACION DE LA INFORMACION SOBRE FASES Y/O AMPLITUDES DE UNA ONDA ELECTROMAGNETICA., del 16 de Mayo de 2004, de SCHWARTE, RUDOLF: Procedimiento para la determinación de información sobre fases y/o amplitudes de una onda electromagnética, en el que se irradia una onda electromagnética […]

CIRCUITO PARA PROCESAR UNA SEÑAL ANALOGICA DE TIEMPOS DISCRETOS Y UN SENSOR DE IMAGEN., del 16 de Diciembre de 2003, de FRAUNHOFER-GESELLSCHAFT ZUR FIRDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Circuito para procesar una señal analógica que presenta una secuencia temporal de niveles de señal discretos, en el que cada nivel de señal discreto […]

DISPOSITIVO DE CONVERSION FOTOELECTRICA QUE UTILIZA EL BARRIDO SUPERFICIAL DE CARGAS., del 16 de Noviembre de 2003, de CANON KABUSHIKI KAISHA: LA INVENCION SUMINISTRA UN ELEMENTO QUE TIENE UNA FUNCION DE TRANSFERENCIA DE CARGA NIVELADORA EN UN DISPOSITIVO DE CONVERSION FOTOELECTRICO DEL TIPO DE DIRECCION […]