BUCLE CERRADO DE RETARDO ANALOGICO/NUMERICO.

Un bucle cerrado de retardo (300) incluyendo: un circuito de retardo digital (302) que permite que elementos de retardo (400) realicen un ajuste de fase basto durante la inicialización en el bucle cerrado de retardo;

un circuito de retardo analógico (304) que proporciona, después de terminar el ajuste de fase basto durante la inicialización, un ajuste de fase fino en el bucle cerrado de retardo mientras el circuito de retardo digital (302) se mantiene a un retardo fijo en respuesta a una señal de control; y circuitería (314, 316, 318) que proporciona una señal de control fija al circuito de retardo analógico (304) mientras que el circuito de retardo digital (302) proporciona el ajuste de fase basto, y que proporciona una señal de control variable al circuito de retardo analógico durante el ajuste de fase fino

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/CA2003/002040.

Solicitante: MOSAID TECHNOLOGIES INCORPORATED.

Nacionalidad solicitante: Canadá.

Dirección: 11 HINES ROAD, SUITE 203 OTTAWA, ON K2K 2X1 CANADA.

Inventor/es: VLASENKO,PETER, HAERLE,DIETER.

Fecha de Publicación: .

Fecha Solicitud PCT: 29 de Diciembre de 2003.

Fecha Concesión Europea: 1 de Septiembre de 2010.

Clasificación Internacional de Patentes:

- H03L7/081A1

- H03L7/10 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › para asegurar la sincronización inicial o para ensanchar el dominio de enganche.

Clasificación PCT:

- H03L7/087 H03L 7/00 […] › utilizando al menos dos detectores de fase o un detector de frecuencia y de fase en el bucle.

Clasificación antigua:

- H03L7/087 H03L 7/00 […] › utilizando al menos dos detectores de fase o un detector de frecuencia y de fase en el bucle.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

ANTECEDENTES DE LA INVENCIÓN

Muchos dispositivos, tales como la memoria síncrona dinámica de acceso aleatorio (SDRAM) y los microprocesadores, reciben una señal de reloj externo generada por una fuente de reloj externo, tal como un oscilador de cristal. La señal de reloj externo recibida a través de un teclado de entrada en el dispositivo es dirigida a varios circuitos dentro del dispositivo a través de un árbol de circuitos intermedios. El árbol intermedio introduce un retardo común entre el reloj externo y cada reloj intermedio.

Típicamente, se usa un bucle cerrado de retardo (DLL) con una línea de retardo ajustable para sincronizar la señal de reloj intermedio con la señal de reloj externo retardando la señal de reloj externo aplicada al árbol intermedio. El DLL incluye un detector de fase, que detecta la diferencia de fase entre la señal de reloj externo y una señal de reloj intermedio. En base a la diferencia de fase detectada, el DLL sincroniza la señal de reloj intermedio a la señal de reloj externo añadiendo un retardo apropiado a la señal de reloj externo hasta que la señal de reloj intermedio externo (el reloj interno) esté en fase con la señal de reloj externo. El DLL puede ser implementado como un bucle cerrado de retardo analógico o un bucle cerrado de retardo digital. En un bucle cerrado de retardo analógico se usa una línea de retardo controlada por voltaje para retardar la señal de reloj externo.

US 6 392 456 describe un DLL incluyendo una línea de retardo digital que tiene unidades de retardo analógicas.

La figura 1 es un diagrama de bloques de un bucle cerrado de retardo analógico de la técnica anterior (DLL)

100. El DLL analógico 100 sincroniza una señal de reloj interno CKI con una señal de reloj externo CKE. La señal de reloj externo CKE está acoplada a una línea de retardo controlada por voltaje 102, y la línea de retardo controlada por voltaje 102 está acoplada a memorias intermedias de árbol de relojes 108. La señal de reloj externo CKE retardada es alimentada a las memorias intermedias de árbol de relojes 108 donde se propaga a las salidas del árbol y es aplicada a los varios circuitos. El retardo a través de la memoria intermedia de árboles de reloj 108 da lugar a una diferencia de fase entre la señal de reloj externo CKE y la señal de reloj interno CKI. La línea de retardo controlada por voltaje 102 regula el retardo de la señal de reloj externo CKE incrementando o disminuyendo el retardo, para sincronizar las señales de reloj externo e interno.

Para determinar el retardo apropiado en la línea de retardo, una de las salidas de las memorias intermedias de árbol de relojes 108 está acoplada a un detector de fase 104 donde se compara con la señal de reloj externo CKE. El detector de fase 104 detecta la diferencia de fase entre el reloj interno CKI y el reloj externo CKE. La salida del detector de fase 104 es integrada por una bomba de carga 106 y un condensador de filtro de bucle 112 para proporcionar un voltaje de polarización variable VCTRL 110 para la línea de retardo controlada por voltaje (VCDL) 102. El voltaje de polarización VCTRL selecciona la cantidad de retardo a añadir a la señal de reloj externo por el VCDL 102 para sincronizar la señal de reloj interno CKI con la señal de reloj externo CKE.

El detector de fase 104 es un flip-flop de tipo D con la entrada D acoplada a la señal de reloj externo CKE y la entrada de reloj acoplada a la señal de reloj interno CKI. En cada borde ascendente de la señal de reloj interno CKI, la salida del detector de fase 104 indica si el borde ascendente de la señal de reloj interno está antes o después del borde ascendente de la señal de reloj externo.

El DLL analógico 100 produce un retardo controlado por voltaje con alta exactitud. Sin embargo, el funcionamiento del DLL analógico varía en un rango de frecuencias porque el retardo generado usando la línea de retardo controlada por voltaje varía de forma no lineal con los cambios del voltaje de control de polarización VCTRL.

La figura 2 es un gráfico que ilustra la característica de voltaje de control no lineal para la línea de retardo controlada por voltaje representada en la figura 1. En general, los dispositivos soportan un amplio rango de frecuencias de reloj externo dentro del que se selecciona una frecuencia operativa para un dispositivo concreto. En el ejemplo representado en la figura 2, el dispositivo puede operar a cualquier frecuencia entre el punto A y el punto C. La frecuencia operativa seleccionada está en el punto B.

Como se representa, la característica de voltaje de control es no lineal: pronunciada en un extremo del rango de voltaje de control (punto C) y casi plana en el extremo opuesto (punto A). Esta característica de voltaje de control da lugar a inestabilidad del DLL en el punto C y tiempos de bloqueo largos en el punto A. El amplio rango de frecuencias (retardos) es controlado por el voltaje de polarización VCTRL.

Con referencia de nuevo a la figura 1, el voltaje de polarización VCTRL es la salida de la bomba de carga 106, que permanece en un estado de alta impedancia la mayor parte del tiempo. Cualquier ruido en la señal de voltaje de polarización VCTRL perturba la salida del DLL analógico 100. Por ejemplo, si el DLL analógico está operando en el punto B, un pequeño cambio de voltaje (ΔV) debido a ruido da lugar a un cambio grande en el retardo. Así, el DLL analógico es muy sensible a ruido cuando opera en el punto B, dentro del amplio rango de frecuencias representado desde el punto C al punto A. Por lo tanto, el DLL analógico no es estable dentro de un amplio rango de frecuencias.

Un DLL digital no tiene el problema de estabilidad de un DLL analógico. Sin embargo, la exactitud de un DLL digital es tan alta como la exactitud de un DLL analógico, porque el retardo se facilita combinando un quantum fijo (pasos) de retardo. Cuanto menor es el paso de retardo, más alta es la exactitud. Sin embargo, una disminución del tamaño del paso da lugar a un aumento correspondiente en la zona de silicio porque se requieren más elementos de retardo para cubrir el amplio rango de frecuencias.

La presente invención proporciona un bucle cerrado de retardo según la reivindicación 1, y un método según la reivindicación 7. Se definen realizaciones de la invención en las reivindicaciones 2 a 6 y 8 a 14.

Un bucle cerrado de retardo según la invención puede tener alta exactitud, buena estabilidad y un tiempo de bloqueo rápido en un amplio rango de frecuencias, puede combinar un tiempo de bloqueo más corto, buena exactitud y estabilidad con bajo consumo de potencia y una zona de silicio pequeña para que el bucle cerrado de retardo opere en un amplio rango de frecuencias.

BREVE DESCRIPCIÓN DE LOS DIBUJOS

Los anteriores y otros objetos, características y ventajas de la invención serán evidentes por la siguiente descripción más concreta de realizaciones preferidas de la invención ilustradas en los dibujos acompañantes en los que caracteres de referencia análogos hacen referencia a las mismas partes en todas las diferentes vistas. Los dibujos no son necesariamente a escala, insistiéndose, en cambio, en que ilustran los principios de la invención.

La figura 1 es un diagrama de bloques de un bucle cerrado de retardo analógico de la técnica anterior (DLL).

La figura 2 es un gráfico que ilustra la característica de voltaje de control no lineal para la línea de retardo controlada por voltaje representada en la figura 1.

La figura 3 es un diagrama de bloques de un bucle cerrado de retardo de amplio rango de frecuencias según los principios de la presente invención.

Las figuras 4A-4B ilustran elementos de retardo en el DCDL y el VCDL.

La figura 5 es un esquema de una realización de cualquiera de los elementos de retardo representados en las figuras 4A-4B.

La figura 6 es un gráfico que ilustra la característica de voltaje de control no lineal para el rango estrecho de frecuencia del VCDL en el DLL representado en la figura 3.

La figura 7 es un esquema de una realización del detector de bloqueo y el interruptor analógico representado en la figura 3.

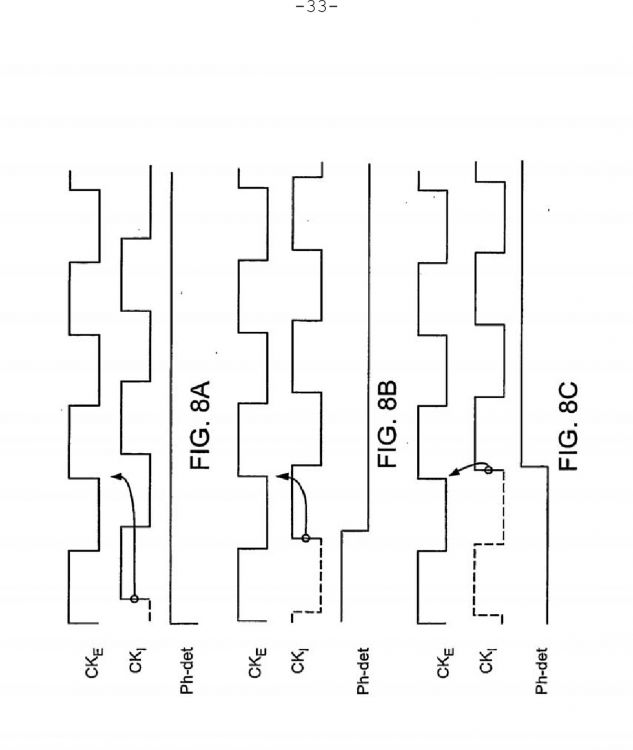

Las figuras 8A-C son diagramas de tiempo que ilustran la relación de la salida del detector de fase a la diferencia de fase entre los relojes.

Y la figura 9 es un diagrama de tiempo que ilustra señales en el esquema representado...

Reivindicaciones:

1. Un bucle cerrado de retardo (300) incluyendo:

un circuito de retardo digital (302) que permite que elementos de retardo (400) realicen un ajuste de fase basto durante la inicialización en el bucle cerrado de retardo;

un circuito de retardo analógico (304) que proporciona, después de terminar el ajuste de fase basto durante la inicialización, un ajuste de fase fino en el bucle cerrado de retardo mientras el circuito de retardo digital (302) se mantiene a un retardo fijo en respuesta a una señal de control; y

circuitería (314, 316, 318) que proporciona una señal de control fija al circuito de retardo analógico

(304) mientras que el circuito de retardo digital (302) proporciona el ajuste de fase basto, y que proporciona una señal de control variable al circuito de retardo analógico durante el ajuste de fase fino.

2. El bucle cerrado de retardo de la reivindicación 1, incluyendo además:

un detector de bloqueo (310) en el circuito de retardo digital (302) que detecta la terminación del ajuste de fase basto, congela el retardo fijo a la terminación y permite el ajuste de fase fino.

3. El bucle cerrado de retardo de la reivindicación 1, donde el circuito de retardo digital opera en un rango de retardo amplio.

4. El bucle cerrado de retardo de la reivindicación 3, donde el circuito de retardo analógico opera en un rango de retardo pequeño dentro del rango de retardo amplio.

5. El bucle cerrado de retardo de la reivindicación 1, donde el circuito de retardo analógico se mantiene a un segundo retardo fijo hasta que el circuito de retardo digital completa el ajuste de fase basto.

6. El bucle cerrado de retardo de la reivindicación 1, donde el circuito de retardo digital incluye una pluralidad de elementos de retardo fijo.

7. Un método para realizar ajuste de fase en un bucle cerrado de retardo incluyendo los pasos de:

permitir que elementos de retardo (400) en un circuito de retardo digital (302) proporcionen ajuste de fase basto en el bucle cerrado de retardo durante la inicialización;

proporcionar una señal de control fija a un circuito de retardo analógico (304) durante el ajuste de fase basto;

proporcionar una señal de control variable al circuito de retardo analógico (304) durante un ajuste de fase fino; y

proporcionar, después de terminar el ajuste de fase basto durante la inicialización, el ajuste de fase fino con el circuito de retardo analógico (304) en el bucle cerrado de retardo mientras que el circuito de retardo digital se mantiene a un retardo fijo proporcionando la señal de control variable al circuito de retardo analógico (304), mientras el circuito de retardo digital (302) se mantiene al retardo fijo.

8. El método de la reivindicación 7, incluyendo

además los pasos de: detectar la terminación del ajuste de fase basto; congelar el ajuste de fase basto a la terminación; y permitir el ajuste de fase fino a la congelación.

9. El método de la reivindicación 7, donde el circuito de retardo digital opera en un rango de retardo amplio.

10. El método de la reivindicación 9, donde el circuito de retardo analógico opera en un segundo rango de retardo que está dentro del rango de retardo.

11. El método de la reivindicación 7, incluyendo además el paso de:

mantener el circuito de retardo analógico a un se

gundo retardo fijo hasta que el circuito de retardo digi

tal complete el ajuste de fase basto.

12. El método de la reivindicación 7, donde el circuito de retardo digital incluye una pluralidad de elementos de retardo fijo.

13. El bucle cerrado de retardo según la reivindica

ción 1, donde el circuito de retardo analógico es distin10 to de y está en serie con el circuito de retardo digital.

14. El método según la reivindicación 7, donde el circuito de retardo analógico es distinto de y está en serie con el circuito de retardo digital.

Patentes similares o relacionadas:

Bucle cerrado de retardo analógico/digital, del 23 de Mayo de 2012, de MOSAID TECHNOLOGIES INCORPORATED: Un bucle cerrado de retardo incluyendo: un circuito de retardo digital que permite que elementos de retardo digital proporcionen ajuste […]

PROCEDIMIENTO DE CONMUTACIÓN DE MODO DE UN OSCILADOR Y DISPOSITIVO OSCILADOR CORRESPONDIENTE, del 13 de Mayo de 2011, de SAGEM MOBILES: Procedimiento de conmutación de modo de un dispositivo oscilador para generar una base de tiempo de un teléfono móvil dando una señal de salida (Ss), para […]

PROCEDIMIENTO DE CONMUTACIÓN DE MODO DE UN OSCILADOR Y DISPOSITIVO OSCILADOR CORRESPONDIENTE, del 13 de Mayo de 2011, de SAGEM MOBILES: Procedimiento de conmutación de modo de un dispositivo oscilador para generar una base de tiempo de un teléfono móvil dando una señal de salida (Ss), para […]

BUCLE ENGANCHADO EN FASE., del 1 de Mayo de 2004, de FUJITSU GENERAL LIMITED: Un circuito PLL en el que están conectados sucesivamente en bucle un comparador de fases, un filtro de bucle, un oscilador de control de tensión y un […]

OSCILADOR PARA UNA ESTACION BASE DE UNA RED CELULAR DIGITAL DE RADIOCOMUNICACIONES., del 1 de Agosto de 2002, de NOKIA NETWORKS OY: EL INVENTO SE REFIERE A UNA UNIDAD OSCILADORA PARA UNA ESTACION DE BASE O SIMILAR EN UNA RED DE RADIO CELULAR DIGITAL. LA UNIDAD OSCILADORA CONSTA DE […]

PROCESO Y DISPOSITIVO DE CONTROL DE MODO DE FUNCIONAMIENTO DE UN BUCLE DE BLOQUEO DE FASE DIGITAL., del 16 de Octubre de 1997, de ALCATEL ALSTHOM COMPAGNIE GENERALE D'ELECTRICITE: ESTE PROCESO DE CONTROL DE MODO DE FUNCIONAMIENTO DE UN BUCLE DE BLOQUEO DE FASE DIGITAL QUE COMPRENDE UN CONTADOR DE CONTROL DE INCREMENTO […]

SINTETIZADOR DE FRECUENCIAS., del 1 de Junio de 1995, de ALCATEL STANDARD ELECTRICA, S.A.: SINTETIZADOR DE FRECUENCIAS. BASADO EN UNA ESTRUCTURA DE BUCLE DE ENGANCHE EN FASE, COMPUESTO POR UN GENERADOR DE SEÑAL DE REFERENCIA , UN PRIMER DETECTOR DE FASE , UN […]

CIRCUITO DE REGULACION DE FASE., del 1 de Noviembre de 1994, de DEUTSCHE THOMSON-BRANDT GMBH: LOS CIRCUITOS DE REGULACION PLL EN OSCILADORES HORIZONTALES DEBEN TENER EN ESTADO BLOQUEADO UNA VELOCIDAD DE REGULACION REDUCIDA, PARA QUE NO SE GENERE EL EFECTO JITTER […]

PROCEDIMIENTO PARA LA REGULACION DE LA FRECUENCIA DE SALIDA GENERADA POR UN OSCILADOR DE FRECUENCIA CONTROLADA, del 16 de Agosto de 2007, de AASTRA DETEWE GMBH: Procedimiento para la regulación de la frecuencia de salida generada por un oscilador de frecuencia controlable, cuya desviación de una frecuencia teórica […]

PROCEDIMIENTO PARA LA REGULACION DE LA FRECUENCIA DE SALIDA GENERADA POR UN OSCILADOR DE FRECUENCIA CONTROLADA, del 16 de Agosto de 2007, de AASTRA DETEWE GMBH: Procedimiento para la regulación de la frecuencia de salida generada por un oscilador de frecuencia controlable, cuya desviación de una frecuencia teórica […]