METODO DE CIFRADO Y DESCIFRADO DE INFORMACION ELECTRONICA UTILIZANDO PERMUTACIONES ALEATORIAS.

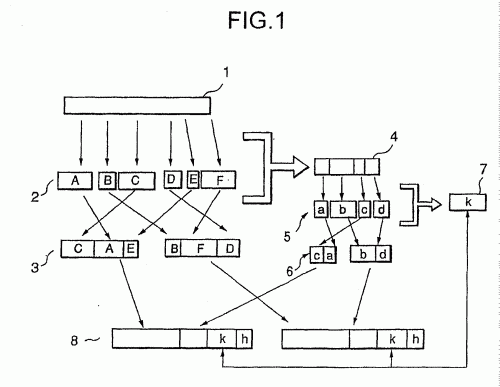

Método de encriptación de información electrónica que comprende etapas de división de un archivo de información electrónica en un número de elementos de información (2) y de generación de más de dos bloques de información (3) seleccionando los elementos de información divididos (2),

caracterizado porque el método incluye las etapas de mezclado de dichos elementos de información (2) seleccionados en diferentes órdenes, en el que cada uno de todos los mencionados elementos de información (2) divididos se incluyen en cualquiera de dichos bloques de información (3) sin redundancia y, también, de generación de un archivo (4) de información de distribución principal que registra la información de división del archivo de información electrónica en dichos elementos de información (2) y la información de formación de los bloques de información (3); de división del archivo (4) de información de distribución principal en un número de fragmentos clave (5); de generación de dos o más bloques clave (6), seleccionando los fragmentos clave (5) divididos y mezclando dichos fragmentos clave (5) seleccionados en orden diferente, en el que cada uno de todos los mencionados fragmentos clave (5) divididos se incluyen en cualquiera de dichos bloques clave (6) sin redundancia; de generación de un archivo (7) de información de distribución secundario que registra la información de formación de dichos fragmentos clave (5) y la información de formación de dichos bloques clave; de creación de un número de paquetes (8) disponiéndolos conjuntamente con dichos bloques de información (3) y los bloques clave (6), o conjuntamente con dichos bloques de información (3), los bloques clave (6) y el archivo (7) de información de distribución secundario; y de almacenamiento o transmisión de los paquetes (8) de manera individual.

Tipo: Resumen de patente/invención.

Solicitante: YASUKURA, YUTAKA.

Nacionalidad solicitante: Japón.

Dirección: 11-13-506 HATAGAYA 1-CHOME, SHIBUYA-KU,TOKYO-TO 151-0072.

Inventor/es: YASUKURA, YUTAKA.

Fecha de Publicación: .

Fecha Solicitud PCT: 20 de Septiembre de 2000.

Clasificación Internacional de Patentes:

- G06F12/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06).

- G06F12/14 G06F […] › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Protección contra la utilización no autorizada de la memoria.

- G06F13/00 G06F […] › Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16).

Clasificación PCT:

- H04L9/34 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 9/00 Disposiciones para las comunicaciones secretas o protegidas. › Bits, o bloques de bits, del mensaje telegráfico intercambiados en el tiempo.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Oficina Europea de Patentes, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Patentes similares o relacionadas:

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Procedimiento de control sistemático de direcciones de zonas de memoria en el marco de una transferencia por acceso directo, del 1 de Abril de 2020, de THALES: Procedimiento de control sistemático por un dispositivo de control de al menos un mensaje de configuración de transferencia, siendo el mensaje de configuración […]

Servidor de seguridad de soporte lógico, del 19 de Febrero de 2020, de Idemia Identity & Security France: Procedimiento de verificación de ejecución de applets (AA1, AB1) desarrolladas en un lenguaje orientado objeto y compiladas en código intermedio, siendo el procedimiento […]

Múltiples conjuntos de campos de atributos dentro de una única entrada de tabla de páginas, del 25 de Septiembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento que comprende: traducir , por una primera unidad de procesamiento , una dirección de memoria virtual a una […]

Procedimiento para proteger datos relevantes para la seguridad en una memoria caché, del 14 de Agosto de 2019, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para proteger datos relevantes para la seguridad en una memoria caché, archivándose una copia de los datos relevantes para la seguridad […]

Archivo seguro, del 7 de Agosto de 2019, de Waterfall Security Solutions Ltd: Aparato de almacenamiento, que comprende: una memoria ; un procesador de encriptado , que está configurado para recibir y encriptar datos transmitidos desde uno […]

Sistemas y métodos para proporcionar como salida un resultado de una instrucción de procesador vigente tras su salida de una máquina virtual, del 3 de Abril de 2019, de Bitdefender IPR Management Ltd: Un sistema anfitrión que comprende al menos un procesador hardware configurado para ejecutar una máquina virtual y un programa de seguridad informática, en donde el al menos […]

Sistema y método para la gestión distribuida de ordenadores compartidos, del 20 de Febrero de 2019, de Zhigu Holdings Limited: Método para operar una arquitectura de gestión informática de múltiples niveles, teniendo dicho método los siguientes pasos: operar un ordenador […]