METODO PARA REDUCIR LOS EFECTOS DEL RUIDO EN LAS MEMORIAS NO VOLATILES POR LECTURA MULTIPLE.

Un método para escribir un valor de datos objetivo en una memoria no volátil,

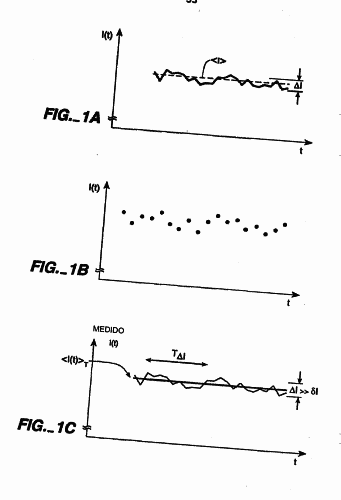

que comprende alterar el estado de un elemento de almacenamiento (301) en la memoria no volátil; verificar un parámetro (Di) indicativo del estado resultante del elemento de almacenamiento en relación con un valor de referencia indicativo del valor de los datos objetivo; y determinar si alterar más el estado del elemento de almacenamiento como respuesta a dicha verificación, que se caracteriza por el hecho de que, al verificar el parámetro se realizan una pluralidad de comparaciones para comparar el parámetro con el valor de referencia indicativo del valor de los datos objetivo.

Tipo: Resumen de patente/invención.

Solicitante: SANDISK CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 140 CASPIAN COURT,SUNNYVALE, CA 94089.

Inventor/es: GONZALEZ, CARLOS J., GUTERMAN, DANIEL C.

Fecha de Publicación: .

Fecha Concesión Europea: 14 de Junio de 2006.

Clasificación Internacional de Patentes:

- G11C16/34 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 16/00 Memorias de sólo lectura programables y borrables (G11C 14/00 tiene prioridad). › Determinación del estado de programación, p. ej. tensión umbral, sobreprogramación o subprogramación, retención.

- G11C7/10 G11C […] › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

Clasificación PCT:

- G11C16/34 G11C 16/00 […] › Determinación del estado de programación, p. ej. tensión umbral, sobreprogramación o subprogramación, retención.

- G11C7/10 G11C 7/00 […] › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

Patentes similares o relacionadas:

Dispositivo de memoria de semiconductor no volátil, del 28 de Agosto de 2019, de Winbond Electronics Corp: Un dispositivo de almacenamiento de semiconductor no volátil , que comprende: una matriz de memoria ; una pluralidad de circuitos de retención de […]

Esquema de distribución con umbral multinivel flash, del 8 de Enero de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Un dispositivo de memoria que comprende: Un arreglo de memoria que tiene celdas de memoria dispuestas en filas y columnas caracterizadas porque: cada celda de memoria […]

Operaciones de mantenimiento para celdas de almacenamiento de datos de múltiples niveles, del 22 de Junio de 2012, de APPLE INC.: Un artículo de fabricación que comprende instrucciones legibles por máquina que, cuando se ejecutan, hacen que se lleven a cabo operaciones, caracterizado […]

SISTEMA Y PROCEDIMIENTO PARA EL FUNCIONAMIENTO SEGURO A ALTA TEMPERATURA DE UNA MEMORIA FLASH., del 1 de Marzo de 2007, de TRW AUTOMOTIVE ELECTRONICS & COMPONENTS GMBH: Sistema para el funcionamiento seguro a alta temperatura de una memoria flash , con un sensor de temperatura que mide la temperatura que caracteriza […]

TECNICAS PARA REDUCIR LOS EFECTOS DE LAS UNIONES ENTRE ELEMENTOS DE ALMACENAJE DE FILAS ADYACENTES DE CELULAS DE MEMORIA., del 16 de Noviembre de 2006, de FLARION TECHNOLOGIES, INC.: Un método para operar una matriz de células de memoria no volátil que almacena datos como diferentes niveles de carga en elementos de almacenamiento […]

PROCEDIMIENTO DE REPETICIÓN PARA TARJETAS INTELIGENTES, del 28 de Diciembre de 2011, de NXP B.V.: Dispositivo de recuperación, para recuperar datos de almacenamiento válidos (SD) en la memoria que presenta: - medios de almacenamiento para almacenar datos […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Método de procesado de datos, aparato de almacenamiento, disco de estado sólido y sistema de almacenamiento, del 28 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesado de datos, aplicado a un sistema de almacenamiento, en donde el sistema de almacenamiento comprende un anfitrión, un controlador y un […]